Abstract

This paper presents an innovative reliability bench of aging life tests designed to high power RF applications for device lifetime under pulse conditions. The temperature effect on the parameters of power RF LDMOS (Radio Frequency Laterally Diffused-Metal–Oxide–Semiconductor) devices is highlighted. Indeed, the acceleration of the degradation mechanisms is related, directly or indirectly, to the temperature variation. The tests carried out on the power amplifier will be "Life-test RF" type (accelerated aging under constant constraints) over a period of 1500 h to quantify the drifts of the parameters measured (mainly POUT and IDSS) under reliability bench life-test at different temperatures. The parameters of devices have been characterized i.e. static, dynamic and RF before and after testing. This allows us to quantify the degradation, of the shift, of a certain number of electrical quantities (VTH, GM, RDSON, CRSS, etc.). The analysis of the physical results has been presented (simulator 2D ATLAS-SILVACO) to explain and observe the physical review of temperature impacts on power RF LDMOS performance. Finally, initial impacts analysis have been discussed.

Similar content being viewed by others

1 Introduction

The huge demand for high performance costs and high effective gives LDMOSFET devices an important place [1]. They have good performances than bipolar and GaAs transistors [1, 2]. Currently, the power RF LDMOS are used in several areas especially on base stations, TV broadcast and in radar systems with high capabilities particularly in terms of output power and Power Added Efficiency (PAE) [3, 4]. Metal Oxide Field Effect Transistors (MOSFETs) are the smost used devices in higher power RF field [3]. They are distinguished many advantages relative to bipolar devices, such as in particular [4, 5]; better linearity, with intermodulation products of smaller amplitude, and these are devices that are better from thermal runaway [1, 6]. The cost of MOSFETs represents a clear advantage over III–V technologies for application rates up to around 4 GHz.

Recently, the characterization, optimization, and reliability of LDMOS devices have drawn much attention [2, 4]. For this purpose, we designed and implemented an innovative reliability bench able to keep monitoring of RF powers, voltages and device basic temperatures where the values correspond to the constraint operating conditions [5, 7, 8]. The duty cycle and pulse length have steadily increased to improve radar performance, from the accession of solid-state power modules in radar system [5]. These important needs for operation have increased the amount of constraint applied to devices and have a direct impact on their lifetime. A study knowledge of temperature impact is important for an improved estimation of modules reliability and of the transistors that compose it [4, 7]. The reliability index was formulated on the assumption basis for reliability calculation [9]. For these reasons, a thorough has initiated to improve new methods for investigating the reliability of RF power devices in pulsed radar operating conditions.

This paper discusses the relationship between the shift of electrical parameters and the subsequently-degraded zone in structure in order to improve the performance at the manufacturer. It also describes how to calculate the device MTTF (Mean Time To Failure) and how to intervene before failure especially in critical applications such as radars or planes.

A full electrical characterization (I–V, C–V and RF) has been performed. Therefore, a full review of these critical electrical parameters is exposed and analyzed.

This manuscript is consisting respectively as follows: reliability pulsed life aging bench; power RF LDMOS structure and simulation; experimental study; results and discussion. At the end, the conclusion and the prospects.

2 Reliability RF pulsed life test bench

This work presents the temperature impact on the reliability of a RF power device submitted to "Life-test RF" on an innovative reliability bench (Figs. 1, 2) dedicated specifically for this purpose. An RF LDMOS device has chosen dedicated to accelerated life tests. All performance degradation of device electrical parameters after accelerated RF pulsed life test at various temperatures are studied and discussed. From the results analysis, we can see that in lower temperature, the drift is greater of significant electrical parameters.

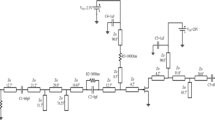

The reliability bench diagram has been implemented is shows in Fig. 1, which will achieve the objective, namely the estimation of the lifetime of the transistors under operational radar conditions [5]. It contains eight "branches" of tests. This choice of eight transistors to be tested results from a compromise between the complication of bench implementation and the samples necessary number for the measurements representativeness.

This bench is able to keep track of many parameters like voltages, currents, base-plate temperature, and peak power. Eight samples is the bench capacity max to test simultaneously. The Fig. 2 represents the devise under test placed on its test fixture, supplied by DC power and connected to RF connector (type N).

The bench is composed of three interdependent subsets:

-

a microwave part,

-

a control/command part piloted by PC,

-

thermal module for each devices.

The DC, RF and thermal conditions applied to the power RF LDMOS device are the following:

-

DC: VDS = 44 V, VGS = 3.79 V, with IDQ≈3 mA at 25 °C.

-

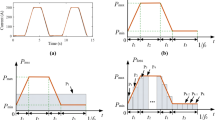

RF: Pulse Width / Cyclic Ratio = 500 μs/50%. Frequency = 2.9 GHz. PIN = 30.5 dBm, POUT = 43-44 dBm.

-

Thermal: Sole temperature of Peltier effect module equal at 25 °C and 150 °C.

The application allows to save temperature, currents and voltages of gate and drain, the reflective values, the input and output powers. After pulsed RF aging, the device behavior shift under test has been characterized at Tam (ambient temperature) and then a parameter set is extracted. The electrical characterization authorize to determine the feedback RF life-tests to any significant parameter shift and better understand the degradation phenomena. The DC conditions correspond to a class B amplification because the source gate voltage is slightly lower than the threshold voltage of the power RF LDMOS (≈ 4–5 V). The amplifier is aged under pulsed CW operation in radar S band, which results in RF conditions. The frequency of 2.9 GHz is the limit value of the civil radar for S band between 2.7 and 2.9 GHz and is in the middle of the military radar (2.7–3.1 GHz). The both conditions of thermal aging that were chosen to accelerate up the tests are provided and regulated by the thermal modules (Peltier effect). The selection of some temperature stress is founded on an industrial property and others come from the experience acquired over the tests course.

3 Simulation and structure of power RF-LDMOS

The physical simulations are investigated by ATLAS-SILVACO [10] for locating and confirming the physical phenomena inside the structure. The physics model Monte Carlo [11] has been used to evaluation the hot electrons and the impact ionization. Through this simulation, can it possible to analyse the static and dynamic characteristics. The physical model based on a precise geometric data, doping, carrier equations and material characteristics.

The ATLAS module of SILVACO [10] used to implant and simulate, a modified device structure of a RF N-channel LDMOS which was analysed by Raman et al. [11]. The recapitulation of technological and geometric data used for simulations, are cited in Table 1. The mesh choice is very important of different regions and it is a primary criterion in a numerical model. This choice is a compromise between accuracy and efficiency of the simulation. The mesh used for the simulation presented in Fig. 3a. Critical zones are situated under the gate (channel region and access) and the Dbody diode [12, 13].

The net doping profile along silicon surface presented in Fig. 3b, with all the cited values are "max" values, or high concentration due to the profiles that are implanted. They are all Gaussian type, except on the epitaxial layer concentration which is uniform (Fig. 3b).

4 Experimental study

This result is founded on the comparison between two components before and after 1500 h of RF aging. Device 1 is aged at room temperature (25 °C) and device 2 at 150 °C. For extract a set of critical electrical parameters, the two transistors have been characterized in static and dynamic area. This work should allow correlating the RF aging for the two different temperatures thanks to the electrical parameter drift. The I–V and C–V measurements were performed at room temperature, respectively by a DC E5270 analyzer and an impedance meter HP 4194, which are driven by Agilent's ICCAP software [14].

4.1 DC measurement

In Fig. 4, present the evolution of the threshold voltage after aging test. The source drain current has been reduced at low source drain voltage level (10 mV) is greater at 25 °C than at 150 °C. This influence is often attributed to charge of mobility and trapping at the oxide / semiconductor interface [1, 6]. For the threshold voltage, it has not shifted significantly by these two temperatures. After an aging of 1500 h, the IDQ quiescent current remained identical, namely 2.79 mA. This current is depends heavily on the threshold voltage level [15]. Therefore, this confirms that the threshold voltage parameter has not substantially drifted and that the integrity of the gate oxide is not affected (no failure catastrophic).

Tables 2 and 3 show that the threshold voltage and transconductance have not practically not varied, regardless of the thermal condition used during the tests. Consequently, this type of "Life-test RF" has no effect in degradation mechanism of these two DC indicators. On the other hand, as the constraint thermal increase, the percentage change of IDSAT and RDSON decreases. In other words, for the temperature 150 °C, IDSAT and RDSON evolve less than 10%. For the temperatures 25 °C, the two DC indicators vary from minus 15%. This can be thought a signature of a notable degradation mechanism.

4.2 AC measurement

In Fig. 5, device 1 exhibited a significant decrease in Miller capacity (CRSS) after aging at 25° C, CRSS is defined by two capacitors in series, the capacity oxide (COX) and drifting region capacity (CSI) (Fig. 6). The mathematical relationship is as follows [16]:

Moreover, the cross-section regarding the power RF LDMOS (Fig. 6) device used in this study was implemented and simulated with ATLAS-SILVACO in order to explain qualitatively electrical parameter shifts [12, 13]. Figure 6 shows the device’s structure with approximate doping wells. The device recommended structure is a Gaussian doping profile model along the channel surface and the LDD area. The doping profile has been optimized with a technological process 2D simulation carried out by SSUPREM3 [12].

For LDMOS power RF devices, the Miller capacitance value at zero volts is mainly caused by the oxide capacity [17]:

The device 1 experienced a strong shift of CRSS profile, in particular at zero VDS (Fig. 5). In the other hand, device 2 exhibited almost two times less CRSS offset at zero VDS (Tables 4 and 5) than device 1.

A summary in table form presents the shifts each AC parameters to conclude in a way quantitative of analysis capacitive state of the samples after aging at 25 °C and 150 °C. Miller capability at 0 V or at 26 V decreased sharply (by at least 15%) regardless of the thermal stress (Tables 4 and 5). The significant decrease is that obtained after the aging test at 25 °C. Two elements notables can also be reported: first, the capacity intrinsic input (CISS) has not varied at all and the values are virtually the same. Second, the intrinsic output capacitance (COSS) is slightly shifted after a test at 25 °C, contrary to 150 °C, where the latter has not practically shifted.

4.3 RF measurement

At low input power value (between 0.4 and 0.6 W), the degradation is not important. When the input power increases, the shift becomes more remarkable. Although the characterization is carried at 25 °C, the variation of POUT (at PIN = 1.1 W, Fig. 7) remains predominant after an RF aging test at 25 °C.

5 Results analysis and discussion

After the characterization step, the devices aged under various thermal stresses show a degradation for the electrical behavior performance (DC, dynamic and microwave). When the temperature constraint is low, the parameters undergo a more consequent variation. The degradation mechanism causes adverse effects even in static and dynamic mode. Because of some parameters that are highly related to a device structure region [14], the degradation can likely locate. Same results proven by several authors like Maanane et al. [7] and Rahmet et al. [18] that have investigated the accelerated aging test effects for these critical electrical parameters of RF LDMOSFETs, specially the VTH, RDSON, CRSS and POUT.

The electrical and physical results of the degradation phenomena allows to deduce that the degradation is related to the hot carriers. To ensure these results, a device physical model was implemented with the ATLAS-SILVACO simulator [10].

During all the life tests, threshold voltage VTH, drain-source current IDS and on-state resistance RDSON are shifted. We noticed that the DC behavior, specially these parameters, are affected by the RF life aging. Vth is increased and has a good interdependence with the IDS current downturn (the RDSON increases due to lower IDS). As a result, numerous electrons are accelerated to high velocities with this peak of higher electric field. They become very energetic and should be accelerated to move away from their ordinary directional flow.

At high voltage VDS bias (44 V) with a 3.8 VGS voltage applied to the device structure. The presence of an intense electric field under gate oxide by a peak in area LDD (Fig. 8) and a high electrons concentration at the SiO2/LDD interface (Fig. 9) contributed to the appearance of hot carriers [5, 19]. The simulation results tend to prove that for these tests conditions (polarization, temperature, etc.) given, all the favors met to a degradation induced by hot carriers. Like the congestion of current lines (Fig. 9) is greater at low temperature at the SiO2/LDD interface, the probability of hot carrier injection is higher at this point at 25 °C than at 150 °C. Consequently, many electrons becomes accelerated to high velocities through this high electric field peak. They become highly energized and should be accelerated away from their normal directional flow.

The origin of the observed shift related to the presence of very high electric field which increase carrier injection into the grown silicon dioxide layer (SiO2) and also into the interface state Si/SiO2 [8, 20]. The hot carrier degradation effect is closely related with current density and with the most number of free electrons in the silicon oxide region, which majority electrons are concentrated deeply inside the drift region [8, 21].

The proven degradation mechanism for power RF LDMOS is, therefore, the creation of interface states by hot carriers (traps) [4, 8, 22]. The current mechanism of degradation is composed of interface states produced by hot carriers (traps) and a some quantity of the hot electrons to be trapped in the later, than results in the accumulation of a negative charge at the Si–SiO2 interface [20, 23]. These negative charges attract load-depleting holes in the device drift region [21, 23] and, therefore, increase the RDSON resistance and reduce the ability of Miller CRSS. Finally, increasing the RDSON resistor, reduces the peak saturation current (IDSS) and related to that, the output power (PSAT) also reduces. Therefore, more interface states are generated in low temperature. All these aspects clearly explain why the drifts of IDSS, POUT and for electrical parameters are more significant at 25 °C than at 150 °C.

6 Conclusion and prospects

In this study, a comparative result has been done to reliability of power RF LDMOS device by two accelerated aging tests. The temperature variation has a repercussion on the electrical parameters and the device behavior; it can also influence its amplification performance. The robustness variations of critical parameters (DC, AC and RF) show that the devices that have been subjected to an RF aging test at 25 °C experience a greater degradation than at 150 °C.

The reliability is shown by monitoring IDS, VTH, RDSON, Pout, T°C and CRSS parameters in order to put in evidence the LDMOS performances. This study highlights that the phenomenon of hot carrier injection is the main degradation mechanism in LDMOS on this defined stress conditions, and that these parameters are sensitive to the electrons injected in gate/SiO2 interface traps. To conclude, the variation of the current during the 1500 h could be due to a hot carrier phenomenon with consequences on device performances.

Other type of aging tests at other conditions is in progress and may be with different technologies such as IGBT and VDMOS.

References

Nayak P, Pramanick SK, Rajashekara K (2018) A High-temperature gate driver for silicon carbide MOSFET. IEEE Trans Ind Electron 65:1955–1964

Ronchi N, Zanon F, Stocco A, Tazzoli A, Zanoni E, Meneghesso G (2009) Reliability analysis of AlGaN/GaN HEMT on SopSiC composite substrate under long-term DC-life test. Microelectron Reliab 49:1207–1210

Du H, Reigosa PD, Iannuzzo F, Ceccarelli L (2019) Impact of the case temperature on the reliability of SiC MOSFETs under repetitive short circuit tests. In: IEEE conference on applied power electronics conference and exposition (APEC), pp 332–337

Cai Y, Zhou H, Mo H et al (2019) Optimization of RF performance and reliability of 28V RF-LDMOS. In: IEEE conference on China semiconductor technology international conference, CSTIC 2019 Shanghai China, pp 19–23

Belaid MA (2018) Symptom reliability: S-parameters evaluation of power laterally diffused-metal–oxide–semiconductor field-effect transistor after pulsed-RF life tests for a radar application. IET Circuits Devices Syst 12:571–578

Belaïd MA, Ketata K, Gares M et al. (2005) Analysis and simulation of self-heating effects on RF LDMOS devices. In: Proceedings of IEEE conference on simulation of semiconductor processes and devices, SISPAD 2005, Tokyo, Japan, pp 231–234

Maanane H, Masmoudi M, Marcon J et al (2005) Study of RF N- LDMOS critical electrical parameter drifts after a thermal and electrical ageing in pulsed RF. Microelectron Reliab 46:415–420

Liu S, Sun W, Qian Q, Wei J et al (2018) A review on hot-carrier-induced degradation of lateral DMOS transistor. IEEE Trans Device Mater Reliab 18:298–312

Ghasemi SH, Nowak AS (2017) Reliability index for non-normal distributions of limit state functions. Struct Eng Mech 62(3):365–372

Silvaco International (1998) Atlas user’s manual-device simulation software. Santa Clara, California

Raman A, Walker DG, Fisher TS (2003) Simulation of non-equilibrium thermal effects in power LDMOS transistors. Solid-State Electron 47:1265–1273

Wang L-S, Xu J-P, Liu L et al (2015) Influences of remote Coulomb and interface-roughness scatterings on electron mobility of InGaAs nMOSFET with high-k stacked gate dielectric. IEEE Trans Nanotechnol 14:854–861

Cortes I, Roig J, Flores D, Urresti J, Hidalgo S (2004) Analysis of hot-carrier degradation in a SOI LDMOS transistor with a steep retrograde drift doping profile. Microelectron Reliab 45:493–498

Sischka F (2002) The IC-CAP characterization and modeling handbook, Munich

Rice J (2002) LDMOS linearity and reliability. Microw J 45(6):64–71

Xu S, Foo P, Wen J, Lui Y, Lin F, Ren C (1999) RF LDMOS with extreme low parasitic feed back capacitance and high hot-carrier immunity. In: IEEE IEDM, pp 201–204

Pritiskutch J, Hanson B (2000) Relate LDMOS device parameters to RF performance, StMicroelectronics

Bilir RA, Altıntaş N, Bilir A, Meşe E, Tosunoğlu Z (2019) A comparative study on power MOSFET reliability and failure modes. In: IEEE conference on symposium INFOTEH-JAHORINA (INFOTEH), pp 20–25

Lin C-Y, Chang T-C, Liu K-J (2017) Analysis of contrasting degradation behaviors in channel and drift regions under hot carrier stress in PDSOI LD N-channel MOSFETs. IEEE Electron Device Lett 18:705–707

Alimin AFM, Hatta SFWM, Soin N (2018) Influence of design considerations on hot carrier injection degradation of STI-based LDMOS transistors. In: IEEE conference on physical and failure analysis of integrated circuits (IPFA), pp 15–19

Hao J, Hahn D, Ghosh A, Rinehimer M, Yedinak J, McGowan B, Choi C, Kopley T (2018) Drift region engineering to reduce hot carrier effects on high voltage MOSFETs. In: IEEE international conference on solid-state and integrated circuit technology (ICSICT), pp 275–279

Belaïd MA, Douad K (2010) Evaluation of hot-electron effects on critical parameter drifts in power RF LDMOS transistors. Microelectron Reliab 50:1763–1767

Hao J, Pelletier M, Murphy R et al (2017) The influence of self heating on the measurement of hot carrier degradation in high voltage n-channel LDMOS. In: Proceedings of international conference on IEEE reliability physics symposium (IRPS), Monterey, CA, USA 2017, pp 41–44

Acknowledgements

The authors wish to thank Dr. Ahmed Almussalam (Umm Al-Qura University) for its helpful discussions, valuable advices, and rich contribution to this paper.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

On behalf of all authors, the corresponding author states that there is no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Belaid, M.A., Tlig, M. Temperature impact on reliability of power RF devices under S-band pulsed-RF test. SN Appl. Sci. 2, 932 (2020). https://doi.org/10.1007/s42452-020-2708-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42452-020-2708-1