Abstract

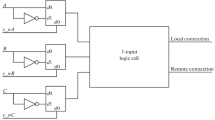

The use of the applicative language (FP) in VLSI design has been advocated, because it provides not only the structure of a circuit, but the planar organization of its components and their interconnections. In this paper, the level of geometric detail implied by the functional programming style is formalized. The notion of ‘planar topology’ of an integrated circuit layout is defined and shown to be the appropriate level of geometric information to infer from an FP specification of a circuit. This definition provides a normal form for the representation of the planar topology of a layout which is not only unique (modulo local operations), but is optimal over all representations of the same planar topology with respect to topological cost measures. This normal form is exploited to improve the wiring of the layouts; it is realized by the application of transformations to the FP specification. The specification of a carry-save array multiplier is used as an example to illustrate how this optimization reduces the effort required to specify an integrated circuit.

Chapter PDF

Similar content being viewed by others

Keywords

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

References

Backus, J., “Can Programming Be Liberated from the Von Neumann Style? A Functional Style and Its Algebra of Programs,” CACM, Turing Award Lecture 21(8), pp.613–641 (August 1978).

Edmonds, J. R., “A combinatorial representation for polyhedral surfaces,” American Mathematical Society Notices(7), p.646 (1960).

Johannsen, D., “Bristle Blocks: A Silicon Compiler,” pp. 310–313 in Proceedings 16th Design Automation Conference, San Diego, California (June 1979).

Leiserson, C. E., “Area-Efficient Graph Layouts (for VLSI),” pp. 270–281 in Proceedings 21st IEEE Symposium on Foundations of Computer Science (1980).

Meshkinpour, F. and M. D. Ercegovac, “A Functional Language for Description and Design of Digital Systems: Sequential Constructs,” pp. 238–244 in Proceedings of the 22nd Design Automation Conference (June 1985).

Newman, M. H. A., “On Theories with a Combinatorial Definition of ‘Equivalence',” Annals of Mathematics 43(2), pp.223–243 (April 1942).

Ousterhout, J. K., “Caesar: An Interactive Editor for VLSI Layouts,” VLSI Design II(4), pp.34–38 (fourth quarter 1981).

Ousterhout, J. K, G. T. Hamachi, R. N. Mayo, W. S. Scott, and G. S. Taylor, “Magic: A VLSI Layout System,” pp. 152–159 in Proceedings of the 21st Design Automation Conference (June 1984).

Patel, D., M. Schlag, and M. Ercegovac, “vFP: An Environment for the Multi-level Specification, Analysis, and Synthesis of Hardware Algorithms,” pp. 238–255 in Functional Programming Languages and Computer Architecture, ed. J.P. Jouannaud, Springer-Verlag Lecture Notes in Computer Science, Nancy, France (September 1985).

Rivest, R. L., “The ‘PI’ (Place and Interconnect) System,” pp. 475–481 in Proceedings 19th Design Automation Conference, Las Vegas, Nevada (June 1982).

Schlag, M., “Extracting Geometry from FP for VLSI Layout,” CSD-840043, University of California, Los Angeles, Los Angeles, California (October 1984).

Schlag, Martine, “Layout from a Topological Description,” PhD Dissertation, Available as Technical Report CSD-860039, University of California, Los Angeles (July 1986).

Sheeran, M., “muFP, a language for VLSI design,” pp. 104–112 in Proceedings ACM Symposium on LISP and Functional Programming (1984).

Siskind, J. M., J. R. Southard, and K. W. Crouch, “Generating Custom High Performance VLSI Designs from Succinct Algorithms,” MIT Conference on Advanced Research in VLSI, pp.28–40 (January 1982).

Valiant, L. G., “Universality Considerations in VLSI Circuits,” IEEE Transactions on Computers C-30(2), pp.135–140 (February 1981).

Youngs, J. W. T., “Minimal Imbeddings and the Genus of a Graph,” Journal of Mathematics and Mechanics 12(2), pp.303–315 (March 1963).

Author information

Authors and Affiliations

Editor information

Rights and permissions

Copyright information

© 1987 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Schlag, M. (1987). The planar topology of functional programs. In: Kahn, G. (eds) Functional Programming Languages and Computer Architecture. FPCA 1987. Lecture Notes in Computer Science, vol 274. Springer, Berlin, Heidelberg. https://doi.org/10.1007/3-540-18317-5_11

Download citation

DOI: https://doi.org/10.1007/3-540-18317-5_11

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-18317-4

Online ISBN: 978-3-540-47879-9

eBook Packages: Springer Book Archive