Abstract

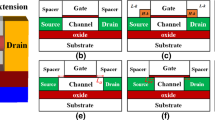

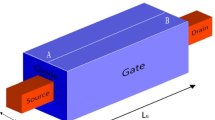

Gate leakage current in lateral GaN wrap-gate nanowire transistors (WG-NWT) was investigated using current density–voltage (Jg–Vg) characteristics at room temperature. We found that the gate leakage current is strongly dependent on the top corner angle of the gate architecture. This leakage current was characterized by considering hopping (Poole–Frenkel emission) and trap-assisted thermionic emission mechanisms. Despite its smaller gate area, the gate leakage current of the lateral GaN WG-NWT without a 2DEG channel was higher than that of the device with a 2DEG channel for all applied gate biases. The reason for this is that the lateral GaN WG-NWT without 2DEG channel has a triangular cross-section with a sharp top corner angle resulting in a strong electric field due to geometrical field enhancement.

Graphic Abstract

Similar content being viewed by others

References

Lieber, C.M., Wang, Z.L.: MRS Bull. 32, 99 (2007)

Yang, P., Yan, R., Fardy, M.: Nano Lett. 10, 1529 (2015)

Calarco, R., Stoica, T., Brandt, O., Geelhaar, L.: J. Mater. Res. 26, 2157 (2011)

Das, P., Jana, S.K., Halder, N.N., Mallik, S., Mahato, S.S., Panda, A.K., Chow, P.P., Biswas, D.: Electron. Mater. Lett. 14, 784–792 (2018)

Jo, Y.J., Jin, H.S., Ha, M.-W., Park, T.J.: Electron. Mater. Lett. 15, 179–185 (2019)

Im, K.-S., Won, C.-H., Jo, Y.-W., Lee, J.-H., Bawedin, M., Crostoloveanu, S., Lee, J.-H.: IEEE Trans. Electron Devices 60, 3012 (2013)

Doyle, B.S., Boyanov, B.S., Datta, S.M., Doczy, M.L., Hareland, S., Jin, B., Kavalieros, J.T., Linton, T.M., Rios, R., Chau, R.: Symposium on VLSI Technology. Digest of Technical Papers, p. 133 (2003)

Im, K.-S., Sindhuri, V., Jo, Y.-W., Son, D.-H., Lee, J.-H., Cristoloveanu, S.: Appl. Phys. Express 8, 066501 (2015)

Vashaee, D., Shakouri, A., Goldberger, J., Kuykendall, T., Pauzauskie, P., Yang, P.: J. Appl. Phys. 99, 054310 (2006)

Motayed, A., Vaudin, M., Davydov, A.V., Melngailis, J., He, M., Mohammad, S.N.: Appl. Phys. Lett. 90, 043104 (2007)

Yu, J.-W., Yeh, P.-C., Wang, S.-L., Wu, Y.-R., Mao, M.-H., Lin, H.-H., Peng, L.-H.: Appl. Phys. Lett. 101, 183501 (2012)

Gacevic, Z., Lopez-Romero, D., Mangas, T.J., Calleja, E.: Appl. Phys. Lett. 108, 033101 (2016)

Im, K.-S., Won, C.-H., Vodapally, S., Caulmione, R., Kim, Y.-T., Lee, J.-H., Cristolovenau, S.: Appl. Phys. Lett. 109, 143106 (2016)

Reddy, M.S.P., Im, K.-S., Lee, J.-H., Caulmione, R., Cristolovenau, S.: Nano Res. 12, 809 (2019)

Im, K.-S., Won, C.-H., Vodapally, S., Son, D.-H., Jo, Y.-W., Park, Y.-H., Lee, J.-H., Lee, J.-H.: J. Cryst. Growth 441, 41 (2016)

Feenstra, R.M., Dong, Y., Lee, C.D., Northrup, J.E.: J. Vac. Sci. Technol. B 23, 1174 (2005)

Wong, B.M., Leonard, F., Li, Q., Wang, G.T.: Nano Lett. 11, 3074 (2011)

Turuvekere, S., Karumuri, N., Rahman, A.A., Bhattacharya, A., DasGupta, A., DasGupta, N.: IEEE Trans. Electron Devices 60, 3157 (2013)

Dutta, G., DasGupta, N., DasGupta, A.: IEEE Trans. Electron Devices 64, 3609 (2017)

Acknowledgements

This work was supported by the National Research Foundation of Korea funded by the Ministry of Science, ICT and Fusion Research (NRF-2018R1D1A1B07040603) and BK21 Plus funded by the Ministry of Education (21A20131600011). Also, partially funded by NRF-2019R1I1A1A01064011.

Author information

Authors and Affiliations

Corresponding authors

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Mallem, S.P.R., Im, KS., Thingujam, T. et al. Gate Architecture Effects on the Gate Leakage Characteristics of GaN Wrap-gate Nanowire Transistors. Electron. Mater. Lett. 16, 433–440 (2020). https://doi.org/10.1007/s13391-020-00229-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13391-020-00229-w