Abstract

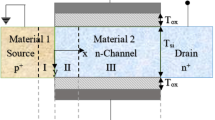

This paper deals with the development of a novel 2-D analytical modeling of heterojunction vertical L-shaped tunnel FET for characterisation of surface potential and drain current. The compact analysis includes the properties of dual modulation effect with the numerous efforts to predict the characteristics of current and to discuss the method of device improvement. The dual modulation effect is used to regulate the biasing voltage at both the junction of source and drain of surface potential to determine the tunneling width. A 2-D Poisson equation is solved for the proposed model by using parabolic approximation method with constant electric field which are used to determine the effect of SiGe mole-fraction, gate-drain biasing potential, dielectric constant of gate oxide, drain doping concentration, metal gate work-function and different binary compound material on the device surface potential. Most importantly, a new channel surface potential expression is derived that can forecast the effect of drain and gate biasing. The derived model results are compared with those of simulated results in order to evaluate the validity of electrical parameter model.

Similar content being viewed by others

References

Koswatta SO, Lundstrom MS, Nikonov DE (2009) Performance comparison between pin tunneling transistors and conventional MOSFETs. IEEE Trans Electron Devices 56(3):456–465. https://doi.org/10.1109/TED.2008.2011934

Kim S, Choi WY (2017) Improved compact model for double-gate tunnel field-effect transistors by the rigorous consideration of gate fringing field. Japanese J Appl Phys 56.8:084301

Choi WY, Park B-G, Lee JD, Liu T-JK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett 28(8):743–745. https://doi.org/10.1109/LED.2007.901273

Yasin Khatami, Kaustav Banerjee, “Steep Subthreshold Slope n- and p-Type Tunnel-FET Devices for Low-Power and Energy- Efficient Digital Circuits,” IEEE Trans Electron Devices, VOL. 56, NO. 11, pp.2752–2760, NOVEMBE R2009https://doi.org/10.1109/TED.2009.2030831

Krishnamohan, Tejas, Donghyun Kim, Shyam Raghunathan, and Krishna Saraswat. "Double-Gate Strained-Ge Heterostructure Tunneling FET (TFET) With record high drive currents and≪ 60mV/dec subthreshold slope." In 2008 IEEE Int Electron Devices Meet, pp. 1–3. IEEE, 2008. https://doi.org/10.1109/IEDM.2008.4796839

Sant S, Schenk A (May 2015) Band-offset engineering for GeSn-SiGeSn hetero tunnel FETs and the role of strain. IEEE J Electron Devices Soc 3(3):164–175. https://doi.org/10.1109/JEDS.2015.2390971

Sun, Min-Chul, Sang Wan Kim, Garam Kim, Hyun Woo Kim, Jong-Ho Lee, Hyungcheol Shin, and Byung-Gook Park. "Scalable embedded Ge-junction vertical-channel tunneling field-effect transistor for low-voltage operation." In 2010 IEEE Nanotechnol Mater Devices Conf, pp. 286–290. IEEE, 2010. https://doi.org/10.1109/NMDC.2010.5652410

Toh E-H et al (2008) Device physics and design of germanium tunneling field-effect transistor with source and drain engineering for low power and high performance applications. J Appl Phys 103.10:104504

Vandenberghe, William G., et al. "Analytical model for a tunnel field-effect transistor." MELECON 2008-The 14th IEEE Mediterranean Electrotech Conf. IEEE, 2008. https://doi.org/10.1109/MELCON.2008.4618555

Boucart K, Ionescu AM (2007) Double-gate tunnel FET with high-$\kappa $ gate dielectric. IEEE Trans Electron Devices 54(7):1725–1733. https://doi.org/10.1109/TED.2007.899389

Wadhera T, Kakkar D, Wadhwa G, Raj B (2019) Recent advances and Progress in development of the field effect transistor biosensor: a review. J Electron Mater 48(12):7635–7646

Badgujjar S et al (2019): 1–9) Design and Analysis of Dual Source Vertical Tunnel Field Effect Transistor for High Performance. Trans Electric Electron Mater. https://doi.org/10.1007/s42341-019-00154-2

Singh S, Raj B (2020) Analytical modeling and simulation analysis of T-shaped III-V heterojunction vertical T-FET. Superlattice Microst 147:106717

Dubey PK, Kaushik BK (2017) T-shaped III-V heterojunction tunneling field-effect transistor. IEEE Trans Electron Devices 64(8):3120–3125. https://doi.org/10.1109/TED.2017.2715853

Singh S, Raj B (2019) Design and analysis of a heterojunction vertical t-shaped tunnel field effect transistor. J Electron Mater 48(10):6253–6260

Singh J, Raj B (2019) Design and Investigation of 7T2M-NVSRAM With Enhanced Stability and Temperature Impact on Store/Restore Energy. IEEE Trans Very Large-Scale Integration (VLSI) Syst 27(6):1322–1328. https://doi.org/10.1109/TVLSI.2019.2901032

Arun Samuel TS, Balamurugan NB, Bhuvaneswari S, Sharmila D, Padmapriya K (2014) Analytical modeling and simulation of single-gate SOI TFET for low-power applications. Int J Electron 101(6):779–788. https://doi.org/10.1080/00207217.2013.796544

Nayfeh OM, Hoyt JL, Antoniadis DA (2009) Strained-$\hbox {Si} _ {1-x}\hbox {Ge} _ {x}/\hbox {Si} $ band-to-band tunneling transistors: impact of tunnel-junction germanium composition and doping concentration on switching behavior. IEEE Transn Electron Devices 56(10):2264–2269. https://doi.org/10.1109/TED.2009.2028055

Wadhwa G, Singh J, Raj B (2020) Design and investigation of doped triple metal double gate vertical TFET for performance enhancement. Silicon:1–11

Wu C, Huang R, Huang Q, Wang C, Wang J, Wang Y (2014) An analytical surface potential model accounting for the dual-modulation effects in tunnel FETs. IEEE Trans Electron Devices 61(8):2690–2696. https://doi.org/10.1109/TED.2014.2329372

Wadhera T, Wadhwa G, Bhardwaj T, Raj DKB (2020) Design and performance analysis of symmetrical and asymmetrical triple gate Dopingless vertical TFET for biorecognition. Silicon,1–9. https://doi.org/10.1007/s12633-020-00686-w

Gholizadeh M, Hosseini SE (2014) A 2-D analytical model for double-gate tunnel FETs. IEEE Trans Electron Devices 61(5):1494–1500. https://doi.org/10.1109/TED.2014.2313037

Prabhat V, Dutta AK (2016) Analytical surface potential and drain current models of dual-metal-gate double-gate tunnel-FETs. IEEE Trans Electron Devices 63(5):2190–2196. https://doi.org/10.1109/TED.2016.2541181

Pandey P, Vishnoi R, Jagadesh Kumar M (2015) A full-range dual material gate tunnel field effect transistor drain current model considering both source and drain depletion region band-to-band tunneling. J Comput Electron 14(1):280–287. https://doi.org/10.1007/s10825-014-0649-x

Sentaurus User’s Manual, Synopsys, Inc., Mountain View, CA, USA,2017.09

Zhang L, He J, Chan M (2012) A compact model for double-gate tunneling field-effect-transistors and its implications on circuit behaviors. Int Electron Devices Meeting. IEEE, 2012. https://doi.org/10.1109/IEDM.2012.6478994

Kane EO (1961) Theory of tunneling. J Appl Phys 32(1):83–91

Semiconductor Industry Association (SIA), International Technology Roadmap for Semiconductors (ITRS), 2015

Acknowledgements

We thank the VLSI design group of NIT Jalandhar for their interest in this work and useful comments to draft the final form of the paper. The support of DST-SERB Project (ECR/2017/000922) is gratefully acknowledged. We would like to thank NIT Jalandhar for lab facilities and research environment to carry out this work.

Data Availability

Not applicable.

Author information

Authors and Affiliations

Contributions

Shailendra Singh: Conceptualization, Methodology, TCAD Software, Data curation, Writing- Original draft preparation, Visualization, Investigation, Software, Validation, Writing and Editing.

Balwinder Raj: Supervision and Reviewing.

Corresponding author

Ethics declarations

All procedures performed in studies involving human participants were in accordance with the ethical standards.

Consent to Participate

Not applicable.

Consent for Publication

The Author transfers his all the copyrights to the publisher.

Conflict of Interest

The authors declare that there are no conflicts of interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Singh, S., Raj, B. Analytical and Compact Modeling Analysis of a SiGe Hetero-Material Vertical L-Shaped TFET. Silicon 14, 2135–2145 (2022). https://doi.org/10.1007/s12633-021-01009-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01009-3