Abstract

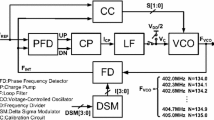

Phase-locked loops (PLLs) serve as core building blocks for communication systems and are often used to synthesize IO clocks for data synchronization and frequency sources for RF conversion. Testing of PLL loop performance is consequently important for guaranteeing the reliability of the underlying communication systems. In this paper, a low cost testing method based on loop triggering and use of built-in analog sensors (small number of transistors) to accurately predict phase-locked loop dynamic parameters is proposed. The sensor responses show strong statistical correlation with the PLL parameters being tested. Accordingly, supervised learning is applied to predict the required PLL parameters from the observed sensor response after “training”. In order to verify analog sensor testing in PLL loop response evaluation, an off-the-shelf PLL and a PLL on printed circuit board (PCB) are tested using this method. The results are analyzed and shown with high correlation to loop parameters. Parameters including charge pump current, voltage-controlled oscillator (VCO) gain, bandwidth, phase margin, and locking time are predicted accurately to prove the viability of the proposed test method.

Similar content being viewed by others

References

Akbay SS, Chatterjee A (2005) “Built-in test of RF components using mapped feature extraction sensors,” in Proc. IEEE VLSI Test Symp., pp. 243–248

Doppler K, Rinne M P, Janis P, Ribeiro C, Hugl K (June 2009) “Device-to-Device Communications; Functional Prospects for LTE-Advanced Networks,” in IEEE International Conference on Communications Workshops, pp.1– 6

Friedman JH (1991) Multivariate adaptive regression splines. The annals of statistics, 1–67

Hsiao S-W, Tzou N, Chatterjee A, (Apr. 2013) “A Programmable BIST Design for PLL Static Phase Offset Estimation and Clock Duty Cycle Detection,” in IEEE VLSI Test Symposium (VTS)

Kim J (Jun. 2009) On-chip measurement of jitter transfer and supply sensitivity of PLL/DLLs. IEEE Trans Circuits Syst II, Exp Briefs 56(6):449–453

Lee JS et al (Nov. 2000) Charge pump with perfect current matching characteristics in phase-locked loops. Electron Lett 36(23):1907–1908

Li MP (2007) Jitter, noise, and signal integrity at high-speed. Prentice-Hall, Westford

Moreira J et al. (2008) “Beyond 10 Gbps? Challenges of Characterizing Future I/0 Interfaces with Automated Test Equipment,” in Proc. IEEE Intl. Test Conf., Lecture 2.3, Santa Clara

Rhee, W (1999) “Design of high-performance CMOS charge pumps in phase locked loops,” in Proc. IEEE Int. Symp. Circuits and Systems, pp. 545–548

Stratigopoulos H-G, Mir S (2012) Adaptive alternate analog test. IEEE Des Test Comput 29(4):71–79

Sunter S, Roy A (1999) “BIST for phase-locked loops in digital applications,” in Proc. Int. Test Conf., pp. 532–540

Sunter S, Roy A. (2007) “Purely digital BIST for any PLL or DLL,” in Proc. Euro. Test Symp., pp. 185–192

USB3.0. [Online]. Available: http://www.usb.org/developers/docs/

Vaughan-Nichols SJ (Nov. 2010) Gigabit wi-fi is on its way. in Comput 43(11):11–14

Veillette BR, Roberts GW (Nov. 1997) “On-chip measurement of the jitter transfer function of charge pump phase-locked loops”. in Proc IEEE Int. Test Conf, Washington, DC, pp 776–785

Voorakaranam R, Cherubal S, Chatterjee A (2002) “A signature test framework for rapid production testing of RF circuits,” in Proc. Des., Autom. Test Eur, pp. 186–191

Yue CP, Jerng A, (June 2009) “RPM-A: Who will win the battle for the Gigabit Wireless in your home: WirelessHD, 802.11n, wireless USB, or UWB?,” in IEEE Radio Frequency Integrated Circuits Symposium

Zorian Y, Dey S, Rodgers MJ (Nov. 2000) “Test of Future Systemon-Chips,” in Proceedings International Conference on ComputerAided Design, 392–400

Acknowledgment

The authors would like to acknowledge Texas Instruments for help on CMOS technology access, and Hittite for the PLL EVB support. Especially the authors want to thank Jeff Galloway, Randy Caplan, and Chung-Chun Chen for advice on circuit design and system operation.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: J.-L. Huang

Rights and permissions

About this article

Cite this article

Hsiao, SW., Wang, X. & Chatterjee, A. Low Cost Built-in Sensor Testing of Phase-Locked Loop Dynamic Parameters. J Electron Test 30, 515–526 (2014). https://doi.org/10.1007/s10836-014-5474-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-014-5474-4