Abstract

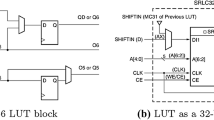

This paper presents Exclusive-OR (XOR)-based decomposition methods to implement XOR-intensive circuits efficiently in field programmable gate arrays (FPGAs). The first proposed method is an extension of the Shannon’s expansion theorem. Such extension enables us to force decomposing the original circuits into the smaller sub-circuits. The second proposed method is based on the Exclusive-or-Sum-Of-Products (ESOP) expression that transforms AND/OR Boolean functions to AND/XOR functions. The XOR relation enables us to find more efficient grouping for the XOR-intensive circuits. The Microelectronics Center of North Carolina (MCNC) benchmark circuits are used to demonstrate the effectiveness of the proposed techniques. The proposed ESOP expression method is superior to the other common techniques in achieving realization efficiency. The proposed ESOP expression method needs 8.08 extra CLBs on average to implement the parity functions of the MCNC benchmark circuits while the typical method needs 14.31 extra CLBs on average. In other words, when using the proposed ESOP expression method, the number of CLBs is reduced by 34% compared to the typical method.