# Formal Aspects of Computing

# A verification-driven framework for iterative design of controllers

Claudio Menghi<sup>1</sup>, Paola Spoletini<sup>2</sup>, Marsha Chechik<sup>3</sup>, and Carlo Ghezzi<sup>4</sup>

<sup>1</sup>University of Luxembourg, Luxembourg, Luxembourg

**Abstract.** Controllers often are large and complex reactive software systems and thus they typically cannot be developed as monolithic products. Instead, they are usually comprised of multiple components that interact to provide the desired functionality. Components themselves can be complex and in turn be decomposed into multiple sub-components. Designing such systems is complicated and must follow systematic approaches, based on recursive decomposition strategies that yield a modular structure. This paper proposes FIDDle-a comprehensive verification-driven framework which provides support for designers during development. FIDDle supports hierarchical decomposition of components into sub-components through formal specification in terms of pre- and post-conditions as well as independent development, reuse and verification of sub-components. The framework allows the development of an initial, partially specified design of the controller, in which certain components, yet to be defined, are precisely identified. These components can be associated with pre- and post-conditions, i.e., a contract, that can be distributed to third-party developers. The framework ensures that if the components are compliant with their contracts, they can be safely integrated into the initial partial design without additional rework. As a result, FIDDle supports an iterative design process and guarantees correctness of the system at any step of development. We evaluated the effectiveness of FIDDle in supporting an iterative and incremental development of components using the K9 Mars Rover example developed at NASA Ames. This can be considered as an initial, yet substantive, validation of the approach in a realistic setting. We also assessed the scalability of FIDDle by comparing its efficiency with the classical model checkers implemented within the LTSA toolset. Results show that FIDDle scales as well as classical model checking as the number of the states of the components under development and their environments grow.

**Keywords:** Distributed development; Controller design; Verification-driven development.

<sup>&</sup>lt;sup>2</sup>Kennesaw State University, Marietta, USA

<sup>&</sup>lt;sup>3</sup>University of Toronto, Toronto, Canada

<sup>&</sup>lt;sup>4</sup>Politecnico di Milano, Milan, Italy

#### 1. Introduction

Software systems are usually comprised of multiple components—portions of the system that provide a desired functionality. In large and complex systems, components themselves can be complex, and decomposed into multiple sub-components. Hence, especially when large systems are considered, system design must follow systematic approaches, based on recursive decomposition strategies that support the development of modular structures. A good decomposition and a careful specification should allow sub-components to be developed in isolation by different members of the development team or be delegated to third parties [Par72a, Par72b]. It should also be possible to reuse off-the-shelf components or delegate development of parts of the system to external service providers [PBKS07, PBvDL05, ABKS16, CH01]. In essence, software development can often be viewed as a distributed endeavor, where different decentralized developers (internal engineers, subcontractors, component and service providers) are coordinated by the organization responsible for the entire system. The main problems of distributed development are in the integration phase, when separately validated components are composed with the other parts of the system and checked for overall correctness. In practice, software failures in the integration phase may lead to expensive and painful changes that may affect the components, the rest of the system, and even lead to changes in the modular structure.

In this article, we focus on the iterative and incremental design of components that abstractly behave as controllers. This term is commonly used to denote components that interact with a complex environment—which may include both physical devices and humans—through events. The controller processes the events generated by the environment and generates events to control it. In particular, we focus on the *provably correct iterative and incremental development of complex, modular controllers*. By this we mean that that component integration is safe and does not require any rework. It guarantees overall correctness by construction.

Recently, several researchers [vBFH+14, tBRdV16] focused on synthesis as a way to obtain correct-byconstruction components. These techniques are tremendously useful for in-house development of small components or development of individual components. Yet, they are not appropriate for many real-world scenarios,

due to their inability to support *iterative and incremental* development which becomes necessary when the problem

is too large to be handled in a single step. In addition, they do not support component reuse. For these reasons,

although significant advances have been made in the direction of synthesis, the fully automated approach based

on synthesis is not yet (and perhaps will never be) able to produce complex components. A more viable solution

is to use synthesis activities in the design process as a *support to human effort* [SL08, SL13]. On the other side

of the spectrum, approaches presented in the literature [BG99, CDEG03, MSG16, MSG17, BMS+17] provide

support for model-checking and top-down refinement of partial models with the goal of preserving correctness.

However, while these techniques guarantee correctness at each development stage, they do not explicitly address

the problem of decentralized development and bottom-up integration, which are needed to support iterative and

incremental development of real-world components. This is the problem we tackle in this work in a detailed and

actionable manner.

We believe that the complete automation of complex components development is both impossible and undesired. Rather, we envision a systematic and formally verified design process where the construction of the overall structure of a complex controller and the various development steps require insight and experience which are human, not machine characteristics [SL08]. This suggests the need for a framework that capitalizes on the synergy between humans and machines for supporting distributed incremental development, by providing tools to enhance (and verify) the human work at each step of the development. In particular, the framework should provide several types of support:

- S1. Modeling support for design activities performed by humans. Novel tools for software development should help humans with modeling formalisms that effectively support components design. This includes support in the contexts in which software components are produced by first creating an initial partial high-level model of a component, where portions of the system that should be later defined are clearly identified, and then developing a detailed model of the behavior of the system for the partially specified portions. The tools should support (i) the description of the environment in which the component will be deployed, (ii) the specification of its required properties, (iii) the creation of the initial (partial) structure of the component, and (iv) the design of the component behavior in the portion of the component that are left unspecified.

- S2. Model analysis support. As developers produce models of their components, they require automatic support to check their designs. Such support should (j) check whether the properties of interest can be satisfied by refining unspecified parts; (jj) check whether the initial partial design satisfies a set of properties of interest. The first check allows developers to verify whether it is possible to refine unspecified parts in a way that guarantees

the satisfaction of the property of interest. This is a necessary requirement for enabling distributed development. The second check is performed after the contracts of the unspecified parts are defined. It allows the verification of whether respecting the given contracts guarantees satisfaction of the properties of interest. If the answer to the latter question is negative, further information that may help the user in fixing the errors, e.g., some form of counterexamples, should be provided.

- S3. Support for iterative and incremental development of unspecified parts. When complex components are considered, it is desirable to first define a high level behavior of the component, leaving some parts temporarily unspecified, and then develop the unspecified parts or reuse existing off-the-shelf sub-components, or even delegate provision of the functionality to an external service provider. To enable this type of development, there is a need for developers to precisely describe what the unspecified parts should do.

- S4. Support for integrating (sub-)components. When (sub-)components associated with the unspecified parts are created and delivered, they must be integrated in the original partially specified design. Integration is a process that replaces the unspecified parts with their actual design. A desired property of the framework we aim to develop is that no work (manual or automatic) should be performed at the integration level.

In this paper, we propose a unified framework called FIDDle (a Framework for Iterative and Distributed Design of components). FIDDle provides a set of tools and techniques for iterative and incremental verification-driven component development. The framework is not based on any specific component models, like the ones commonly adopted by industry (such as Java Beans, Microsoft's COM family, or others). It is positioned at a higher and more abstract level, and assumes components to be fragments of functionality modeled as state machines. The framework supports a formal specification of global properties, a decomposition process and a specification of component interfaces by providing a set of tools to guarantee correctness of the different artifacts produced during the process. The capability of FIDDle to approximate complex designs by contracts and to replace a prototypical implementation with a more sophisticated one at a later stage fosters decomposition of complex designs and component reuse. Specific novel contributions of FIDDle are:

- 1. a new formalism, called *Interface Partial Labeled Transition System (IPLTS)*, for specifying components through a decomposition that encapsulates sub-components into unspecified black-box states;

- 2. an approach to specify *the expected behavior of black-box states* via pre- and post-conditions expressed in Fluent Linear Time Temporal Logic (FLTL); and

- 3. a notion of *component correctness* and a *local verification procedure* that *guarantees preservation of global properties* once the components are composed.

We also report on the evaluation of FIDDle on a realistic case study obtained by reverse-engineering the executive module of the Mars Rover developed at NASA [GPB02, CGP03, GPB05]. Scalability is evaluated by considering randomly-generated examples.

FIDDle was first presented in [MSCG18]. This paper extends the work in [MSCG18] in several directions:

- it presents a complete formal treatment of the work, including proofs of all lemmas and theorems;

- it provides a detailed description of the algorithms;

- it shows how the presented approach can be applied recursively;

- it provides a thorough comparison with related work;

- it describes the FIDDle tool support;

- it provides additional detail of our evaluation.

The rest of the paper is organized as follows. Section 2 describes our running example. Section 3 provides an overview of FIDDle. Section 4 gives the necessary background. Section 5 describes the semantics for FLTL on finite traces. Section 6 presents Interface Partial Labeled Transition Systems. Section 7 defines a set of algorithms for reasoning on partial components and describes their implementation. Section 8 reports on an evaluation of the effectiveness and scalability of the proposed approach. Section 9 compares FIDDle with related approaches, and Sect. 10 concludes the paper.

P1: ship and product info are provided only if a request has been received.

P2: when user requests are processed, offers are considered only after users received information about the desired product.

P3: the furniture service is activated only if the user has decided to purchase.

P4: when a user request is canceled by the p&d system, no user ack precedes the cancellation.

(d) Properties of the p&d system.

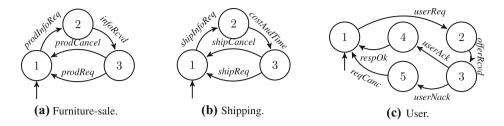

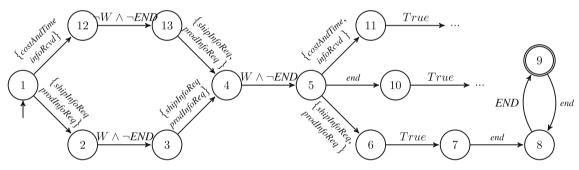

Fig. 1. The p&d environment (Figs. 1a, 1b, 1c) and the properties the p&d system must ensure (Fig. 1d)

# 2. Running example

We illustrate FIDDle using a simple example of *purchase&delivery* (p&d) [PBB+04, DBPU13], shown in Fig. 1. The p&d system supports furniture purchase and delivery. The system allows users to check whether certain items are present, and to order the desired product or cancel the order.

To provide this functionality, the p&d system uses two existing web services, which implement the furniture-sale and the shipping. The behavior of the furniture-sale service is described in Fig. 1a through a simple state machine. The service is initially in the state 1. The transition labeled with the action *prodInfoReq* allows the furniture-sale component to be queried to check the presence of some furniture. The transition labeled with the action *infoRcvd* indicates that the information regarding the furniture is provided. Finally, transitions labeled with *prodReq* and *prodCancel* indicate that the furniture is requested or the order is canceled.

The behavior of the shipping service is described in Fig. 1b. The transition labeled with *shipInfoReq* allows the shipping component to be queried to check the presence of some furniture. The transition labeled with *costAndTime* indicates that the information regarding the cost and time of the delivery is provided. Transitions labeled with *shipReq* and *shipCancel* indicate that the shipping is being requested and that the order is canceled, respectively.

The desired interactions of the users with the yet-to-be-defined component are described in Fig. 1c. The transition labeled with *userReq* indicates that the user performs a request to the system. The transition labeled with *offerRcvd* indicates that the user receives the desired information (furniture presence and shipping information). Based on this information, the user can choose whether to accept or refuse the offer. This is represented through the transitions labeled with the actions *userAck* and *userNack*. The system then has to confirm to the the user that her choice has been correctly processed via transitions labeled with the actions *respOk* and *reqCanc*.

The goal of the development team is to design a component, referred in the following as the p&d component, which acts as a controller interacting with the user and the two services in order to satisfy the user requests. The furniture-sale, the shipping service and the user represent the environment within which the component under development should operate. The final design of the p&d component must ensure that the controller, when plugged into its environment, will satisfy a set of properties of interest, reported in Fig. 1d. For example, in the final system, ship and product info should not be provided to the user if a request has not been issued. The development team decides to adopt a top-down development approach, which first creates an initial, partial and preliminary high-level description of the system where the still-to-be-refined parts of the system are explicitly indicated. The unspecified parts of the component are refined into sub-components, whose design and implementation are delegated to third-party developers, who receive a contract that should be satisfied by the sub-component. It is strongly desired that no rework be performed during the integration phase.

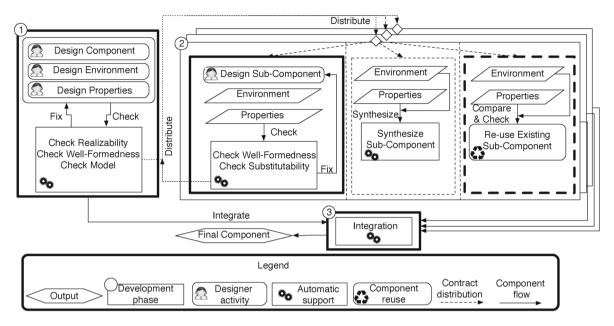

Fig. 2. Overview of the application of FIDDle for developing a component. Thick-bordered components are implemented in FIDDle. Thick-dashed bordered components are currently supported by the theory presented in this paper, but they are still not fully implemented. Thin-dashed bordered components are not discussed in this work

#### 3. Overview

FIDDle is a verification-driven environment supporting iterative and incremental controller developments, as described in Sect. 1. A high-level view of FIDDle is shown in Fig. 2. FIDDle allows controllers to be modularly and incrementally developed in a distributed manner, through a set of development phases in which the human insight and experience are exploited to achieve a verified modular structure (rounded boxes labeled with a designer icon and a recycle symbol indicate design or reuse, respectively) and phases in which automated support is provided (squared boxes labeled with a pair of gearwheels). Automatic support is provided to verify the current state of the design, integrate synthesized or off-the-shelf components, decentralize component development to third parties, and check whether integrated components correctly fit into the overall design. FIDDle structures controller developments according to a set of phases described in the following.

# 3.1. Creating an initial component design

This phase is identified in Fig. 2 with the symbol ①. FIDDle provides modeling support for design activities performed by humans and analysis support for design validation.

FIDDle provides suitable formalisms to specify requirements and to model behavior of the controller and of its (sub-)components (step S1 in Sect. 1). The development team formalizes the component's desired properties through the requirements specification language and designs an initial, high-level structure of the component. Components are modeled using a state-based formalism that can clearly identify sub-components, represented as *black-box* states, whose internal design is delayed to a later stage or split apart for distributed development by other parties. In the following, we refer to other (non black-box) states as "regular". Black-box states are enriched with an *interface* that provides information on the universe of events relevant to the black box. They are also decorated with pre- and post-conditions that allow distributed teams to develop sub-components without the need to know about the rest of the system. The *contract* of a black-box state consists of its interface and the pre- and post-conditions.

```

P1 = (\neg((\neg F\_UserReq) \ \mathcal{U}(F\_ShipInfoReq \lor F\_ProdInfoReq)))

P2 = \Box(F\_UserReq \rightarrow (\neg((\neg F\_InfoRcvd) \ \mathcal{U} \ F\_OfferRcvd)))

P3 = \Box(F\_UsrReq \rightarrow ((\neg((\neg F\_UserAck) \ \mathcal{W} \ F\_ShipReq))

P4 = \Box((F\_UsrReq \land ((\neg F\_UserAck) \ \mathcal{U} \ F\_ReqCanc)) \rightarrow ((\neg F\_UserAck) \ \mathcal{U} \ F\_ReqCanc))

```

(a) FLTL formulation of the p&d properties.

(b) p&d supervisor design-Partial p&d.

(d) Another partial p&d component.

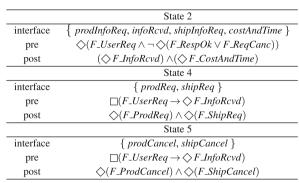

(c) Contracts for black-box states of Figs. 3b, 3d and 3j.

(e) A sub-component for black-box state 2.

(g) A sub-component for black-box state 5.

**(f)** Another sub-component for black-box state 2.

|           | State 5.2                                       |

|-----------|-------------------------------------------------|

| interface | $\{ shipCancel \}$                              |

| pre       | $\Box(F\_UserReq \to \diamondsuit F\_InfoRcvd)$ |

| post      | $\Diamond(F\_ShipCancel)$                       |

(h) Contract for black-box state 5.2.

(i) A sub-component for black-box state 5.2.

(j) Integration of the sub-component of Fig. 3e and the component of Fig. 3d.

Fig. 3. The p&d running example: artifacts produced by FIDDle

In the p&d example, the environment (assumed as given) in which the p&d component will be deployed is composed by the furniture-sale component (Fig. 1a), the shipping component (Fig. 1b) and the user (Fig. 1c). A possible initial design for the p&d component is shown in Fig. 3b. It contains the regular states 1 and 3 and black-box states 2 and 4. State 1 is the initial state. Whenever a userReq event is detected, the component moves from the initial state 1 into the black-box state 2, which represents a sub-component in charge of managing the user request. An event offerRcvd which indicates that an offer is provided to the user labels the transition to state 3. The interface of the black-box states 2 and 4 and their pre- and post-conditions are shown in Fig. 3c. The interface indicates that events prodInfoReq, infoRcvd, shipInfoReq and costAndTime can occur while the component is in the black-box state 2. Pre- and post-conditions need to be provided by the developers. Pre-conditions specify properties that hold up to entering the corresponding black-box state and post-conditions specify properties that should be ensured by black-box states. Both of them can be used in the analysis: whether the finite behaviors reaching the black-box state guarantee satisfaction of the pre-conditions and whether the black-box state can be replaced by their post-conditions to verify the validity of properties of interest. The pre- and post-conditions are discussed in detail in this section.

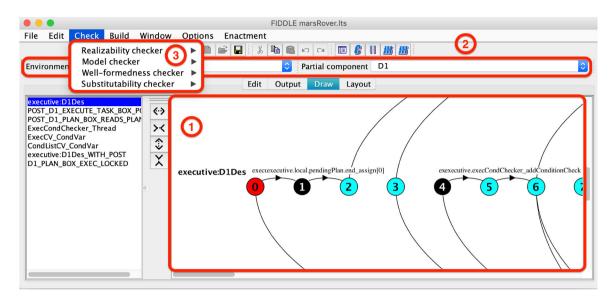

FIDDle supports the designer by checking properties of the design at different stages of development (step S2 in Sect. 1). The *realizability checker* confirms the existence of a realizable component that can be integrated to complete a partially specified component and ensures satisfaction of the properties of interest. If such a component does not exist, the designer needs to redesign the partially-specified component. The *well-formedness checker* verifies that both the pre- and the post-conditions of black-box states are satisfiable. Finally, the *model checker* verifies whether the (partial) component (together with its contract) guarantees satisfaction of the properties of interest.

In the p&d example, the model checker identifies a problem with the partial solution sketched in Fig. 3b. No matter how the black-box state 2 is to be defined, the p&d component cannot satisfy property P4 since every time reqCanc occurs it is preceded by usrAck. This suggests a re-design of the p&d component, which may lead to a new model, shown in Fig. 3d. This model includes two regular states: state 1, in which the component waits for a new user request, and state 3, in which the component has provided the user with an offer and is waiting for an answer. The user might accept (userAck) or reject (userNack) an offer and, depending on this choice, either state 4 or 5 is entered. States 2, 4 and 5 are black-box states, to be refined later.

To support iterative and incremental development of unspecified parts, FIDDle allows designers to specify pre- and post-conditions for the black-box states (steps S3 and S4 in Sect. 1). In the p&d example, pre- and post-conditions of the black-box state 2 specify that there is a pending user request, and that cost, time and product information are collected. Pre- and post-conditions of the black-box state 4 specify that *infoRcvd* has occurred after the user request, and both a product and shipping requests are performed. Finally, pre- and post-conditions of the black-box state 5 specify that *infoRcvd* has occurred after the user request and before entering the state, and both the product and the shipping requests are canceled when leaving the state. This model is checked using the verification tools; since it passes all the checks, it can be used in the next phase of the development.

The design team may choose to refine the component or *distribute* the development of unspecified sub-components (represented by black box states) to other (internal or external) development teams. In both cases, the sub-component can be designed by only considering the contract of the corresponding black-box state. Each team can develop the assigned sub-component or reuse existing components.

#### 3.2. Sub-component development

This phase is identified in Fig. 2 with the symbol ②. During sub-component development, FIDDle provides support to the modeling activities performed by humans (step S1 in Sect. 1). In the p&d example, each team can design the assigned sub-component using any available technique, including manual design (left side), reusing of existing sub-components (right side) or synthesizing new ones from the provided specifications (center).

To support iterative and incremental development of unspecified parts and safe integration of the developed of sub-components, FIDDle requires the developed sub-components to satisfy some constraints, namely,

- 1. given the stated pre-condition, the sub-component has to satisfy its post-condition, and

- 2. the sub-component should operate in the same environment as the overall partially specified component.

Sub-component development can itself be an iterative process (see Sect. 3.4) but neither the model of the environment nor the overall properties of the system can be changed during this process. Otherwise, the resulting sub-component cannot be safely and automatically integrated into the overall system.

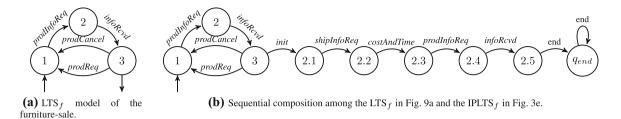

In the p&d example, development of the sub-component for the black-box state 2 is delegated to an external (third-party) contractor. Candidate sub-components are shown in Figs. 3e-3f. In the case of Fig 3e, the component requests shipping info details and waits until the shipping service provides the shipment cost and time. Then it queries the furniture-sale service to obtain the product info. In the case of Fig 3f, the shipping and the furniture services are queried, but the sub-component does not wait for an answer from the furniture-sale. Since these candidates are fully defined, the well-formedness check is not needed. Yet, the *substitutability checking* confirms that of these, only the sub-component in Fig. 3e satisfies the post-condition in Fig. 3c.

#### 3.3. Integration of sub-components

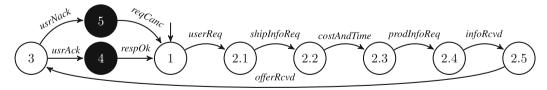

This phase is identified in Fig. 2 with the symbol ③. FIDDle supports integration of the development of sub-components and guarantees that if each sub-component is developed correctly w.r.t. the contract of the corresponding black-box state, the component obtained by integrating the sub-components is also correct (step S4 in Sect. 1). In the p&d example, the sub-component in Fig. 3e passes the substitutability check and can be a valid implementation of the black-box state 2 in Fig. 3d. Integration is shown in Fig. 3i.

# 3.4. Recursive application of FIDDle

FIDDle can be applied recursively, allowing to distribute development of portions of the sub-components (e.g., to third-party vendors). This is indicated in Fig. 2 with the symbol (2).

For example, Fig. 3g shows an initial partial design of the sub-component associated with state 5 of the p&d example. This partially-specified sub-component requires the system to increase the count of canceled orders, enters the black-box state 5.2, and finally cancels the order. FIDDle provides automated support for the sub-component design. The well-formedness confirms that the pre- and the post- conditions of black-box states are satisfiable. The substitutability checking notifies the designer that the sub-component in Fig. 2 does not ensure the satisfaction of its post-condition. Indeed, there is no guarantee that shipping of the product is canceled (i.e., the *ShipCancel* event occurs). The post-condition for the black-box state 5.2, shown in Fig. 3h, which ensures that the shipping is performed before the black-box state 5.2 is exited by the system, guarantees that the sub-component passes the substitutability checking. In turn, the black-box state 5.2 is decomposed into the sub-component represented in Fig. 3i. This component is completely specified. Upon its entry, the counter of the canceled shipping orders is incremented and then the shipping is canceled. When it is entered, the counter of the canceled shipping orders is incremented by one. The substitutability checking confirms that the sub-component is substitutable and can be integrated within the black-box state 5.2. This iterative process can be applied for any partially specified subcomponent.

To conclude, FIDDle allows the iterative and incremental distributed development of controllers and provides the support described in Sect. 1. FIDDle relies on an extension of Labeled Transition Systems (LTS) that allows the representation of incompleteness and offers the possibility of defining an initial modular incomplete structure. It also allows distributing the design of the missing components and offers automatic support for the verification of the different parts and for substitutability analysis of components within a partially defined structure.

# 4. Background

This section contains background knowledge and definitions used in the rest of the paper. Section 4.1 introduces LTS. Section 4.2 provides a high level description of Büchi automata (BA). Section 4.3 introduces Fluent Linear Time Temporal Logic (FLTL). Finally, Sect. 4.4 outlines a procedure for verifying the satisfaction of FLTL properties on LTS.

# 4.1. Labeled transition systems

Labeled Transition Systems are a specific type of state machines commonly used to model software components and their environments.

**Definition 4.1** [Kel76] Let Act be the universal set of observable events and let  $\tau$  be an unobservable local event. A *finite Labeled Transition System* (LTS<sub>f</sub>) is a tuple  $F = \langle Q, q_0, A, \Delta, Q_f \rangle$ , where

- Q is a finite set of states,

- $q_0 \in Q$  is the initial state,

- $A \subseteq Act$  is a finite set of events,

- $\Delta \subseteq Q \times A \cup \{\tau\} \times Q$  is the transition relation, and

- $Q_f \in Q$  is the set of final states.

A Labeled Transition System (LTS)  $L = \langle Q, q_0, A, \Delta \rangle$  is an LTS<sub>f</sub> where the set of final states is not defined.

For example, Fig. 3e contains an LTS<sub>f</sub> with states 2.1, 2.2, 2.3, 2.4 and 2.5, where 2.1 and 2.5 are its initial and final states, respectively. Transitions specify how the LTS<sub>f</sub> evolves by firing transitions labeled with events shipInfoReq, costAndTime, prodInfoReq and infoRcvd.

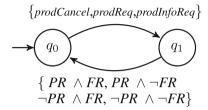

Fig. 1a contains an LTS for modeling a furniture-sale component. The LTS is defined over the states 1, 2 and 3, where state 1 is initial. Transitions specify how the LTS evolves by firing transitions labeled with events prodInfoReq, infoRcvd, prodCancel and prodReq.

Given a state q (of an LTS or an LTS<sub>f</sub>), let  $\Delta(q)^-$  and  $\Delta(q)^+$  denote its incoming and outgoing transitions, respectively, and let  $\Delta(q)$  denote the union of the incoming and outgoing transitions of q. For example, in the LTS in Fig. 1a,  $\Delta(1)^+ = \{(1, prodInfoReq, 2)\}$ . Given a transition  $\delta = (q_1, e, q_2)$ , we use  $\delta^-$  to indicate its source  $q_1, \delta^+$  to indicate its destination  $q_2$ , and  $\delta_e$  for its label e. For example, for the transition  $\delta = (2, infoRcvd, 3)$  of the LTS in Fig. 1a,  $\delta^- = 2$ ,  $\delta^+ = 3$  and  $\delta_e = infoRcvd$ .

**Definition 4.2** Let  $F = \langle Q, q_0, A, \Delta, Q_f \rangle$  be a LTS<sub>f</sub>. A *finite* sequence  $q_0, e_0, q_1, e_1, \ldots, q_n, e_n, q_{n+1}$ , such that for every  $0 \le i \le n$ ,  $(q_i, e_i, q_{i+1}) \in \Delta$  and  $q_{n+1} \in Q_f$ , is a *finite* execution of F, and  $\pi = e_0, e_1, \ldots, e_n$  is a *trace* of F. Let  $L = \langle Q, q_0, A, \Delta \rangle$  be an LTS. An *infinite* sequence  $q_0, e_0, q_1, e_1, \ldots$ , such that for every  $i \ge 0$ ,  $(q_i, e_i, q_{i+1}) \in \Delta$ , is an *infinite* execution of L, and  $\pi = e_0, e_1, \ldots$  is a *trace* of L.

Traces of an LTS<sub>f</sub> are finite and reach final states representing finite computations. For example, *shipInfoReq*, costAndTime, prodInfoReq, infoRcvd is the only finite trace of the LTS<sub>f</sub> in Fig. 3e. LTS traces are infinite, i.e., the system is not designed to stop. For example, prodInfoReq, infoRcv, prodReq repeated infinitely often is an infinite trace of the LTS in Fig. 1a.

**Definition 4.3** Let  $\pi = e_0, e_1, \ldots, e_n$  and  $\pi' = e'_0, e'_1, \ldots, e'_n$  be two sequences of events. We use the notation  $\pi$ ;  $\pi'$  to indicate their concatenation  $e_0, e_1, \ldots, e_n, e'_0, e'_1, \ldots, e'_n$ .

In the rest of this paper, when not specified, we assume that LTS<sub>f</sub> and LTS are *minimized* with respect to bisimulation. Intuitively, given an LTS<sub>f</sub> (respectively, an LTS), the minimization procedure removes  $\tau$  actions and generates a LTS<sub>f</sub> (respectively, an LTS) with the same behavior (for additional information about minimization, refer to [MK99]).

*Parallel composition* is a symmetric operator that takes two LTS $_f$  and computes a resulting one by synchronizing on shared events and interleaving the others.

**Definition 4.4** Let  $M = \langle Q_M, q_{0,M}, A_M, \Delta_M, Q_{f,M} \rangle$  and  $N = \langle Q_N, q_{0,N}, A_N, \Delta_N, Q_{f,N} \rangle$  be LTS<sub>f</sub>. Parallel composition of M and N (denoted by  $M \parallel N$ ) is an LTS<sub>f</sub>  $P = \langle Q_M \times Q_N, \langle q_M^0, q_N^0 \rangle, A_M \cup A_N, \Delta, Q_{f,M} \times Q_{f,N} \rangle$ , where  $\Delta$  is the smallest relation that satisfies the following rules:

(1)

$$\frac{(s, l, s') \in \Delta_M}{(\langle s, t \rangle, l, \langle s', t \rangle) \in \Delta}, l \in A_M \setminus A_N \text{ or } l = \tau$$

(2)

$$\frac{(t, l, t') \in \Delta_N}{(\langle s, t \rangle, l, \langle s, t' \rangle) \in \Delta}, l \in A_N \setminus A_M \text{ or } l = \tau;$$

(3)

$$\frac{(s, l, s') \in \Delta_M, (t, l, t') \in \Delta_N}{(\langle s, t \rangle, l, \langle s', t' \rangle) \in \Delta}, l \in A_N \cap A_M, l \neq \tau;$$

where  $l \in A_M \cup A_N \cup \{\tau\}$ , s and s' are states in  $Q_M$ , and t and t' are states of  $Q_N$ . Parallel composition of two LTS is defined identically, except that final states are excluded.

Rules (1) and (2) indicate that there is an interleaving on non-shared events and Rule (3) that there is a synchronization on shared ones.

Given a set of events H, the *hiding operator* turns all the transitions labeled with events in H into  $\tau$ -labeled, i.e., unobservable events.

**Definition 4.5** Let  $F = \langle Q, q_0, A, \Delta, Q_f \rangle$  be an LTS<sub>f</sub> and  $H \subseteq A$ . \ is a hiding operator such that  $N = F \setminus H$  is an LTS<sub>f</sub>  $N = \langle Q, q_0, A', \Delta', Q_f \rangle$ , where the following conditions hold:

- $A' = A \setminus H$ ;

- $\Delta' = \{(q, e, q') \mid (q, e, q') \in \Delta \text{ and } e \in A \setminus H\} \cup \{(q, \tau, q') \mid (q, e, q') \in \Delta \text{ and } e \in H\}.$

For LTS, hiding is defined identically, except that final states are excluded.

For example, if the hiding operator is applied to the LTS in Fig. 1a w.r.t. the set  $\{prodInfoReq\}$ , the transition from state 1 to state 2 labeled with prodInfoReq is replaced by one labeled with  $\tau$ .

#### 4.2. Büchi automata

Büchi Automata are a reference formalism commonly used in the verification community.

**Definition 4.6** [Büc90] Let AP be a finite set of atomic propositions. A *Büchi automaton* (BA) defined over AP is a tuple  $B = \langle Q, q_0, A, \Delta, Q_a \rangle$  such that:

- Q is a finite set of states;

- $q_0$  is the initial state:

- $A \subseteq AP$  is a finite set of atomic propositions;

- $\Delta \subseteq Q \times A \times Q$  is the transition relation;

- $Q_a \subseteq Q$  is the set of the accepting states.

Given a BA  $B = \langle Q, q_0, A, \Delta, Q_a \rangle$ ,  $\pi = e_0, e_1, \ldots$  is an *infinite trace* of B if there exists an infinite sequence  $q_0, e_0, q_1, e_1, \ldots$ , where, for every  $i \geq 0$ ,  $(q_i, e_i, q_{i+1}) \in \Delta$  and there exists a state  $q_i \in Q_a$  that appears in the sequence infinitely often.

It is possible to check (using a standard procedure described in [Büc90]) whether a given BA has no infinite trace. We indicate this check by a function CHECKEMPTINESS(B) which returns *true* if the automaton accepts no infinite traces and thus is empty, and *false* otherwise.

An LTS can be converted into a BA which accepts exactly the same traces:

**Lemma 4.1** Let  $L = \langle Q, q_0, A, \Delta \rangle$  be an LTS.  $\pi = e_0, e_1, \ldots$  is a trace of L if and only if it is a trace of the BA  $B = \langle Q, q_0, A, \Delta, Q \rangle$ .

The BA contains the same states and transitions as the LTS and all of its states are accepting. This ensures that, if a trace of the LTS is also a trace of the BA, it will enter at least an accepting state of the BA an infinite number of times, since the set of states is finite. Every infinite trace of the BA is an infinite trace of the LTS by construction. We call LTS2BA the procedure for converting an LTS into a BA. This procedure copies all the states and transitions from the LTS to the BA and adds all the states of the LTS in the set of the accepting states of the BA. For example, the BA obtained from the LTS in Fig. 1a has the same states and transitions, and states 1, 2 and 3 are also accepting.

The *intersection operator* computes the synchronous product of two automata: given two BA M and N, it computes a BA whose traces are the intersection of the traces of M and N.

**Definition 4.7** [CGP99] Let  $M = \langle Q_M, q_{0,M}, A, \Delta_M, Q_{a,M} \rangle$  and  $N = \langle Q_N, q_{0,N}, A, \Delta_N, Q_{a,N} \rangle$  be BA defined over the same alphabet A. Their *intersection* is a symmetric operator  $(\cap)$  such that  $P = M \cap N$  is a BA  $P = \langle Q_M \times Q_N \times \{0,1,2\}, \langle q_{0,M}, q_{0,N}, 0 \rangle, A, \Delta, Q_{a,M} \times Q_{a,N} \times \{2\} \rangle$ , where a transition  $(\langle q_m, q_n, x \rangle, A, \langle q'_m, q'_n, y \rangle)$  is in  $\Delta$  if and only if:

- 1.  $(q_m, e, q'_m) \in \Delta_M$  and  $(q_n, e, q'_n) \in \Delta_N$ ;

- 2. if x = 0 and  $q'_m \in Q_{a,M}$  then y = 1;

- 3. if x = 1 and  $q'_n \in Q_{a,N}$  then y = 2;

- 4. if x = 2 then y = 0;

- 5. otherwise, y = x.

The states of the system contain all the possible combinations of the states of the automata M and N and the values  $\{0,1,2\}$ . A transition from a state  $\langle q_m,q_n,x\rangle$  to a state  $\langle q'_m,q'_n,y\rangle$  labeled with e is in the intersection if both M and N can move from  $q_m$  (resp.  $q_n$ ) to  $q'_m$  (resp.  $q'_n$ ) on a transition labeled with e. The third component in each state is responsible for guaranteeing that an infinite trace of the intersection automaton is present if and only if it corresponds to an infinite trace of M (resp. N) in which an accepting state is visited infinitely often. The third component is initially 0, and changes from 0 to 1 and from 1 to 2 whenever an accepting state of M and N is entered, respectively. After an accepting state of N is visited, it is set back to 0. This construction guarantees that every infinite trace of the intersection automaton is an infinite trace of both M and N, i.e., where accepting states of M and N are visited infinitely often.

#### 4.3. Fluent linear time temporal logic

It is often non-trivial to express LTL properties directly in terms of events, especially when the interest is to define intervals among the occurrence of different events and relationships between them. Thus, in this work, we consider FLTL [San95, CDGV02, GM03] as a logic to express properties of the system.

A *fluent* is a property that holds after an event occurs and ceases to hold when it is terminated by another event.

**Definition 4.8** [San95] A fluent Fl is a tuple  $\langle I_{Fl}, T_{Fl}, Init_{Fl} \rangle$  where  $I_{Fl} \subset Act$  is the set of *initiating events*,  $T_{Fl} \subset Act$  with  $I_{Fl} \cap T_{Fl} = \emptyset$  is the set of *terminating events* and  $Init_{Fl} \in \{true, false\}$  is the initial valuation.

A fluent may be *true* or *false*. The initial value of the fluent is specified using the attribute  $Init_{Fl}$  [MS99]. A fluent is *true* if it has been initialized by an event  $e_1 \in I_{Fl}$  at an earlier time point (or if  $Init_{Fl} = true$ , i.e., it was initially *true*) and has not yet been terminated by another event  $e_2 \in T_{Fl}$ ; otherwise, it is *false*. For example, the fluent  $PR = \langle \{prodInfoReq\}, \{prodCancel, prodReq\}, false \rangle$ , representing the fact that the furniture-sale component is processing a request, is initially *false*. It becomes *true* from the moment when the event prodInfoReq occurs, i.e., a request is received, until the moment in which the event prodCancel, which cancels the order request, or the event prodReq, which confirms the order request, occur.

Fluents also implicitly allow developers to specify properties on event occurrence. The occurrence of an event  $e \in Act$  can be considered by defining a fluent where the initial set of actions is the singleton  $\{e\}$  and the terminating set contains all other actions in the alphabet of the system, i.e.,  $Act \setminus \{e\}$ . In the following, we use the notation  $F\_Event$  to indicate a fluent that is *true* when the event with label *event* occurs.

**Definition 4.9** Given a set of fluents  $\Phi$ , an FLTL formula  $\phi$  has the following syntax:

$$\phi := Fl \mid \neg \phi \mid \phi_1 \land \phi_2 \mid \bigcirc \phi \mid \Diamond \phi \mid \square \phi \mid \phi \mathcal{U} \phi \mid \phi \mathcal{W} \phi$$

, where  $Fl \in \Phi$

$\bigcirc$  (next),  $\diamondsuit$  (eventually),  $\square$  (always),  $\mathcal{U}$  (until) and  $\mathcal{W}$  (weak until) are the standard LTL operators.

For example, the FLTL property  $\diamondsuit(PR)$  states that eventually the furniture-sale component will process a request. The FLTL encodings of the properties P1, P2, P3 and P4 are shown in Fig. 3a. Note that, for completeness, Definition 4.9 provides the complete syntax of FLTL formulae, including the operators  $\diamondsuit$  (eventually),  $\square$  (always) and  $\mathcal{W}$  (weak until), but all the FLTL formulae can be expressed using only the operators  $\bigcirc$  and  $\mathcal{U}$ .

The semantics of FLTL formulae is given by considering infinite sequences of fluents associated with *infinite* traces of an LTS. We begin by constructing an FLTL interpretation of an infinite trace.

**Definition 4.10** Let  $Act_{\tau} = Act \cup \{\tau\}$ . Given a set of fluents  $\Phi$  and an infinite trace  $\pi = e_0, e_1, \ldots$  over  $Act_{\tau}$ , an FLTL *interpretation* of  $\pi$  is an infinite sequence  $f_0, f_1, \ldots$  over  $2^{\Phi}$  which assigns to each index i of  $\pi$  the set of fluents that hold in position i. Formally,  $\forall i \in \mathbb{N}, \forall Fl \in \Phi, Fl \in f_i$  if and only if either of the following conditions hold:

- $Init_{Fl} = true$  and  $(\forall k \in \mathbb{N}, k \leq i, e_k \notin T_{Fl});$

- $\exists j \in N$  such that  $(j \leq i)$  and  $(e_j \in I_{Fl})$  and  $(\forall k \in \mathbb{N}, j < k \leq i, e_k \notin T_{Fl})$ .

Consider an infinite trace of the LTS in Fig. 1a, in which the events prodInfoReq, infoRev, prodReq are repeated infinitely often, and a set of fluents  $\{PR\}$ . The infinite interpretation of this trace is an infinite sequence in which the set  $\{PR\}$  is assigned to each index i where events prodInfoReq or infoRev occur and the set  $\{\}$  is assigned to each index j where the event prodReq occurs. In this sequence, the fluent PR holds from the time of occurence of the event prodInfoReq until occurence of prodReq (that time point itself is excluded).

The FLTL infinite semantics specifies when a formula  $\phi$  is satisfied by the FLTL interpretation of an infinite trace.

**Definition 4.11** Let  $\pi = e_0, e_1, \ldots$  be an infinite trace,  $\rho = f_0, f_1, \ldots$  be its FLTL interpretation and  $\phi$  be an FLTL formula. The FLTL infinite semantics of  $\phi$  over  $\rho$  is defined as follows:

```

\begin{array}{lll} \rho_{i} \models Fl & \Leftrightarrow & Fl \in \rho_{i} \\ \rho_{i} \models \neg \phi & \Leftrightarrow & \rho_{i} \not\models \phi \\ \rho_{i} \models \phi_{1} \land \phi_{2} & \Leftrightarrow & \rho_{i} \models \phi_{1} \text{ and } \rho_{i} \models \phi_{2} \\ \rho_{i} \models \bigcirc(\phi) & \Leftrightarrow & \rho_{i+1} \models \phi \\ \rho_{i} \models (\phi_{1})\mathcal{U}(\phi_{2}) & \Leftrightarrow & \exists k \geq i \text{ such that } \rho_{k} \models \phi_{2}, \text{ and } \forall j \text{ such that } i \leq j < k, \text{ it holds that } \rho_{j} \models \phi_{1}, \end{array}

```

where  $\rho_i$  indicates the infinite sub-trace of  $\rho$  starting at position i.

The semantics of  $\diamondsuit$  (eventually),  $\square$  (always) and  $\mathcal{W}$  (weak until) is not presented since it is standard and can be deduced from the semantics of the operators  $\bigcirc$  and  $\mathcal{U}$ .

Given an infinite trace  $\pi$  and a formula  $\phi$ , we say that  $\pi$  satisfies  $\phi$  (denoted  $\pi \models \phi$ ) if and only if the FLTL interpretation  $\rho$  of  $\pi$  satisfies  $\phi$  (i.e.,  $\rho \models \phi$ ). For example, the infinite trace of the LTS in Fig. 1a in which the events  $\operatorname{prodInfoReq}$ ,  $\operatorname{infoRev}$ ,  $\operatorname{prodReq}$  are repeated infinitely often satisfies the FLTL property  $\Diamond(PR)$ . Note that since FLTL is a natural extension of LTL, it is closed under negation. The proof can be obtained, for example, by applying the procedure described in [YPA06].

# 4.4. Verifying FLTL properties on LTS

Verification of an FLTL property  $\phi$  on an LTS L aims at checking whether  $\phi$  holds on L. We first define the notion of satisfaction of an FLTL  $\phi$  on an LTS L and then review a procedure for checking an FLTL  $\phi$  on an LTS L.

**Definition 4.12** Let L be an LTS and  $\phi$  be an FLTL formula. We say that the LTS L satisfies the FLTL formula  $\phi$ , i.e.,  $L \models \phi$ , if for every infinite trace  $\pi$  of L, it holds that  $\pi \models \phi$ .

Consider the LTS in Fig. 1a and the fluent PR. The FLTL formula  $\Diamond$  PR holds on this LTS.

We now recall a procedure to check an FLTL formula  $\phi$  on an LTS L. Note that the infinite traces of the LTS are defined over the set of events A, while the formula is defined over the set of fluent propositions  $\Phi$ . This gap has been handled by introducing fluent automata and synchronizer automata. These automata are used in the verification procedure to bind event occurrence with the fluent satisfaction. We first present fluent automata and synchronizer automata and then describe how they are used in the verification procedure.

A fluent automaton relates the occurrence of events with the satisfaction of a given fluent.

**Definition 4.13** Let  $\Phi$  be a set of fluents and  $Fl = \langle I_{Fl}, T_{Fl}, Init_{Fl} \rangle$  be a fluent in  $\Phi$ . Its *fluent automaton* is an LTS  $F = \langle Q, q_0, A, \Delta \rangle$ , where:

```

\begin{array}{l} \bullet \ \ Q = \{q_t, q_f\}; \\ \bullet \ \ A = I_{Fl} \cup T_{Fl} \cup 2^\Phi; \\ \bullet \ \ \Delta = \{(q_f, e, q_t) \mid e \in I_{Fl}\} \cup \\ \{(q_t, e, q_t) \mid e \in I_{Fl}\} \cup \\ \{(q_t, e, q_f) \mid e \in T_{Fl}\} \cup \\ \{(q_f, e, q_f) \mid e \in T_{Fl}\} \cup \\ \{(q_f, e, q_f) \mid x \in 2^\Phi \ \text{and} \ Fl \not\in x\}; \\ \bullet \ \ q_0 = q_t \ \text{if initially} \ Init_{Fl} = true, \ \text{else} \ q_0 = q_f. \end{array}

```

The automaton has two states:  $q_t$ , where the fluent holds, and  $q_f$ , where it does not. The automaton moves from  $q_t$  (resp.  $q_f$ ) to  $q_f$  (resp.  $q_t$ ) if an event from its initiating (resp. terminating) set occurs. Fluent satisfaction is represented by self-transitions labeled with the fluent propositions from  $2^{\Phi}$ . For example, consider the set of fluents  $\Phi = \langle PR, FR \rangle$ , where  $PR = \langle \{prodInfoReq\}, \{prodCancel, prodReq\}, \{flse\}, \}$ , and fR is an additional arbitrary fluent. The fluent automaton associated with the fluent PR is represented in Fig. 4.

Fig. 4. Fluent automaton associated with the fluent PR

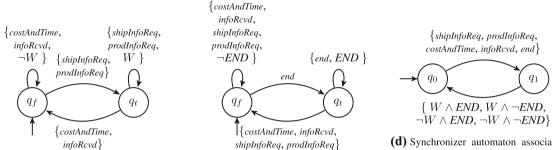

Fig. 5. Synchronizer automaton associated with the fluent PR and FR and the set of events  $A = \{prodInfoReq, prodCancel, prodReq\}$

In Fig. 4, multiple transitions with the same source and destination states are represented by a single transition, where the atomic propositions that label the different transitions are separated by commas. For example, the transition labeled with the atomic propositions {prodInfoReq,  $PR \land FR$ ,  $PR \land \neg FR$ } indicates three different transitions, labeled with prodInfoReq,  $PR \land FR$  and  $PR \land \neg FR$ . If a transition labeled with PR is fired, the fluent PR does not hold. As expected, infinite traces of the automaton indicate that PR holds only after an event prodInfoReq and before events {prodCancel, prodReq}. Furthermore, PR does not hold initially and becomes false after occurrence of either of the events prodCancel, prodReq and before a transition labeled with prodInfoReq is fired.

While the fluent automaton allows taking a transition labeled with a fluent (e.g., PR in Fig. 4) or its negation (e.g.,  $\neg PR$  in Fig. 4), nothing forces these transitions to actually take place. Instead, we aim to generate an automaton that is forced to alternate the execution of transitions labeled with events and fluents. This automaton is obtained by combining the fluent automaton with a special *synchronizer* automaton, which we define below.

**Definition 4.14** Let  $\Phi$  be a set of fluents and Act be a set of events, such that for all  $Fl \in \Phi$ ,  $I_{Fl} \subseteq Act$  and  $T_{Fl} \subseteq Act$ , the *synchronizer automaton* is an LTS  $Sync = \langle Q, q_0, A, \Delta \rangle$ , where

- $Q = \{q_0, q_1\};$

- $A = Act \cup 2^{\Phi}$ ;

- $\Delta = \{(q_1, Fl, q_0) \mid Fl \in 2^{\Phi}\} \cup \{(q_0, e, q_1) \mid e \in Act\}.$

The synchronizer automaton has two states:  $q_0$  and  $q_1$ . It moves from  $q_0$  to  $q_1$  by firing a transition labeled with an event, and from  $q_1$  to  $q_0$  by firing a transition labeled with a fluent. Thus, it alternatively executes transitions labeled by events and by fluents. For example, the synchronizer automaton associated with the fluents PR and FR and the set of events  $A = \{prodInfoReq, prodCancel, prodReq\}$  is shown in Fig. 5.

#### Algorithm 1 Checks an FLTL formula on an LTS.

- 1: **function** CHECKFLTLONLTS $(L, \phi, F_1, F_2, \dots F_n, Sync)$

- 2:  $B \Leftarrow LTL2BA(\neg \phi)$

- 3:  $P \Leftarrow (L \parallel F_1 \parallel F_2 \parallel \dots F_n \parallel Sync)$

- 4:  $P' \Leftarrow LTS2BA(P)$

- 5:  $B' \Leftarrow ADDEVENTS(B, Act)$

- 6:  $\mathcal{I} \Leftarrow B' \cap P'$

- 7: **return** CHECKEMPTINESS( $\mathcal{I}$ )

The synchronizer and the fluent automata are used to verify FLTL formulae on LTS via a procedure described in Algorithm 1, in which the classical model checking algorithm presented in [CGP99] is enriched to deal with

FLTL instead of LTL and the combination of LTS and BA. The procedure takes as parameters the LTS L, the formula  $\phi$ , the fluent automata  $F_1, F_2, \dots F_n$ , and the synchronizer Sync. It returns true if the property  $\phi$  is satisfied, and false and a counterexample if it is not. The algorithm translates the negation of the formula into a BA B by using a standard LTL2BA procedure [VW94] (Line 2). Then, it computes the parallel composition between the LTS L, the fluent automata  $F_1, F_2, \ldots F_n$  and the synchronizer Sync (Line 3). In the traditional automata-based approach, the next step is to compute the intersection between the BA representing the system and the BA representing the negation of the LTL property to check. Since in our case, the model is an LTS, it needs to be converted in a BA via the function LTS2BA (Line 4). Moreover, as the transitions of the obtained BA are labeled with fluents and transitions of the model obtained in Line 3 alternate fluents and events, to correctly compute the intersection between the model and the formula (Line 6), we need to add a self-loop labeled with the events in Act to all the states in B (Line 5). The reason is that the intersection that is computed in the next step of the algorithm (Line 6) synchronously fires transitions of the automata B' and P'. Thus, transitions labeled with events of P' can only fire if the BA obtained from the property also contains transitions labeled with events. Essentially, the BA P' fires its transitions depending on the behavior of the system and on the relation between events and fluents. The intersection extracts from those behaviors the ones that also satisfy the property of interest as specified by the fluent-labeled transitions present in the automaton B'. The function CHECKEMPTINESS is then used to verify whether the automaton  $\mathcal{I}$  is empty.

**Theorem 4.1** Algorithm 1 returns true if and only if there exists an infinite trace of the LTS L which satisfies the FLTL formula.

# 5. Fluent linear time temporal logic and finite traces

Section 4 described how FLTL formulae are evaluated on infinite traces. However, it might be necessary to evaluate satisfaction of formulae on finite traces, e.g., recall that pre- and post-conditions introduced in Sect. 3 specify properties over traces that reach unspecified components. In this section,

- we define finite semantics of FLTL formulae, referred to as  $FLTL_f$  (Sect. 5.1);

- we present a procedure for checking  $FLTL_f$  formulae on  $LTS_f$  (Sect. 5.2). Our procedure reuses the algorithm for checking the satisfaction of FLTL formulae on LTS presented in Sect. 4.4;

- we present a procedure for taking an  $FLTL_f$  formula  $\phi$  and synthesizing from it an  $LTS_f$  that exhibits exactly those finite traces that satisfy  $\phi$  (Sect. 5.3). This procedure forms one of the main tools used in FIDDle for providing automatic support for iterative design of components, as described in Sect. 7.

# 5.1. $FLTL_f$ semantics on finite traces

Interpretation of FLTL formulae on finite traces is denoted by  $FLTL_f$ .  $FLTL_f$  syntax is the same as FLTL and its semantics is inspired by [DGV13].

We begin by defining the interpretation of a fluent Fl on a finite trace.

**Definition 5.1** Let  $\Phi$  be a set of fluents, and  $\pi = e_0, e_1, \ldots, e_n$  be a finite trace over Act. An FLTL<sub>f</sub> interpretation of  $\pi$  is a finite sequence  $f_0, f_1, \ldots, f_n$  over  $2^{\Phi}$  which assigns to each index i of  $\pi$  the set of fluents that hold in position i for  $0 \le i \le n$ , by following the same rules as specified in Definition 4.10.

Consider the finite trace shipInfoReq, costAndTime, prodInfoReq, infoRcvd of the LTS $_f$  in Fig. 3e and the fluent  $W = \langle \{shipInfoReq, prodInfoReq\}, \{costAndTime, infoRcvd\}, false \rangle$ , which is true when the system is waiting for some information. The fluent W becomes true when a request is performed by the component, i.e., a shipInfoReq or a prodInfoReq event occur, and becomes false when some information is received (costAndTime or infoRcvd occurs). The FLTL $_f$  interpretation of the trace shipInfoReq, costAndTime, prodInfoReq,  $infoRcvd \text{ is } \{W\}$ ,  $\{\}$ ,  $\{W\}$ ,  $\{\}$ . We now use the interpretation of a finite trace to define the FLTL $_f$  semantics.

**Definition 5.2** Let  $\pi = e_0, e_1, \ldots, e_n$  be a finite trace,  $\rho = f_0, f_1, \ldots, f_n$  be its FLTL<sub>f</sub> interpretation, and  $\phi$  be a FLTL<sub>f</sub> formula. The FLTL<sub>f</sub> finite semantics of  $\phi$  over  $\rho$  is as defined by Definition 4.11, with the exception of the operators  $\bigcirc$  and  $\mathcal{U}$  defined as follows:

$$\begin{array}{lll} \rho_i \models \bigcirc(\phi) & \Leftrightarrow & i < n \land \rho_{i+1} \models \phi \\ \rho_i \models (\phi_1) \mathcal{U}(\phi_2) & \Leftrightarrow & \exists \, i \leq k \leq n \text{ such that } \rho_k \models \phi_2 \text{ and } \forall \, i \leq j < k, \, \, \rho_j \models \phi_1, \end{array}$$

where  $\rho_i$  refers to the finite sub-trace of  $\rho$  starting at position i.

Intuitively, a formula preceded by the operator  $\bigcirc$  does not hold in the last position of the interpretation, since the operator  $\bigcirc$  forces the existence of the next position of the interpretation. A formula of the type  $(\phi_1)U(\phi_2)$  forces the fluent  $\phi_2$  to occur before reaching the position n of the interpretation. For example, the formula  $\bigcirc(W)$ , where W is the fluent previously defined, does not hold on the finite trace shipInfoReq, costAndTime, prodInfoReq, infoRevd. Given a finite trace  $\pi$  its  $FLTL_f$  interpretation  $\rho$  and a formula  $\phi$ , we say that  $\pi \models \phi$  if and only if  $\rho \models \phi$ .

# **5.2.** Verifying $FLTL_f$ properties on $LTS_f$

We begin by defining what it means for an LTS<sub>f</sub> L to satisfy an FLTL<sub>f</sub> formula, and then present a verification procedure that checks the satisfaction of an FLTL<sub>f</sub> formula  $\phi$  on an LTS<sub>f</sub> L. We reduce this problem to checking an FLTL formula  $\phi'$  on an LTS L', where  $\phi'$  and L' are obtained from  $\phi$  and L. We begin by showing that checking whether an FLTL<sub>f</sub> formula  $\phi$  holds on a finite trace  $\pi$  can be done by evaluating whether an equivalent FLTL formula  $\phi'$  holds on the *infinite extension*  $e(\pi)$  of the trace  $\phi$ .

**Definition 5.3** Let  $\pi = e_0, e_1, \ldots, e_n$  be a finite trace defined over the set of events  $Act_{\tau}$  such that  $end \notin Act_{\tau}$ . Its infinite extension,  $e(\pi) = e_0, e_1, \ldots, e_n$ ,  $\{end\}^{\omega}$ , is obtained by concatenating an infinite number of occurences of the event end to the trace  $\pi$ .

**Definition 5.4** Let F be an LTS<sub>f</sub> and  $\phi$  be an FLTL<sub>f</sub> formula. We say that the LTS<sub>f</sub> F satisfies the FLTL<sub>f</sub> formula  $\phi$ , i.e.,  $F \models \phi$ , if for every finite trace  $\pi$  of F, it holds that  $\pi \models \phi$ .

Consider the LTS<sub>f</sub> in Fig. 3e and the fluent W. The FLTL<sub>f</sub> formula  $\diamondsuit W$  holds on this LTS<sub>f</sub>.

**Definition 5.5** Let  $\Phi$  be a set of fluents defined over the alphabet  $Act_{\tau}$ , such that  $end \notin Act_{\tau}$ ,  $\Phi'$  be a set of fluents defined over the alphabet  $Act_{\tau} \cup \{end\}$ ,  $\phi$  be an  $FLTL_f$  formula defined over  $\Phi$ , and  $\phi'$  be an FLTL formula defined over  $\Phi'$ .  $\phi'$  is *equivalent* to  $\phi$  if for every finite trace  $\pi$ ,  $\pi \models \phi \Leftrightarrow e(\pi) \models \phi'$ .

We now want to define an operator  $FLTL_f 2FLTL$  that, given an  $FLTL_f$  formula  $\phi$ , generates an equivalent FLTL formula  $\phi'$ .

**Definition 5.6** Let  $\Phi$  be a set of fluents defined over the alphabet  $Act_{\tau}$ , such that  $end \notin Act_{\tau}$ , END be the fluent  $\langle \{end\}, Act_{\tau}, false \rangle$ , and  $\phi$  be an  $FLTL_f$  formula defined over  $\Phi$ . The operator  $FLTL_f$  2FLTL converts  $\phi$  into an FLTL by applying the following rules:

```

\begin{split} \operatorname{FLTL}_f & \operatorname{2FLTL}(Fl) \to Fl', \text{ where } Fl = \langle I_{Fl}, T_{Fl}, \operatorname{Init}_{Fl} \rangle \text{ and } Fl' = \langle I_{Fl}, T_{Fl} \cup \{end\}, \operatorname{Init}_{Fl} \rangle; \\ & \operatorname{FLTL}_f \operatorname{2FLTL}(\neg \phi) \to \neg \operatorname{FLTL}_f \operatorname{2FLTL}(\phi); \\ & \operatorname{FLTL}_f \operatorname{2FLTL}(\phi_1 \wedge \phi_2) \to \operatorname{FLTL}_f \operatorname{2FLTL}(\phi_1) \wedge \operatorname{FLTL}_f \operatorname{2FLTL}(\phi_2); \\ & \operatorname{FLTL}_f \operatorname{2FLTL}(\bigcirc \phi) \to \bigcirc (\operatorname{FLTL}_f \operatorname{2FLTL}(\phi) \wedge \neg END); \\ & \operatorname{FLTL}_f \operatorname{2FLTL}(\phi_1 \mathcal{U} \phi_2) \to \operatorname{FLTL}_f \operatorname{2FLTL}(\phi_1) \mathcal{U}(\operatorname{FLTL}_f \operatorname{2FLTL}(\phi_2) \wedge \neg END). \end{split}

```

Let  $\phi = \bigcirc \neg W$  be an FLTL $_f$  formula, and  $\pi = e_0, e_1, \ldots, e_n$  be a finite trace. We discuss the evaluation of the formula in the final position n of the trace. The formula  $\bigcirc \neg W$  is false in position n by Definition 5.2, as i < n is not satisfied. Let us consider the extension  $e(\pi)$  of  $\pi$ . The FLTL $_f$  formula  $\bigcirc ((\neg W) \land \neg END)$  obtained from  $\phi$  by applying the function FLTL $_f$ 2FLTL is false in position n, as intended. This formula evaluates to true in position n only after adding the event end to the set of the terminating events of the fluent W.

Consider a finite trace  $\pi$  defined over the set of events  $Act_{\tau}$ , such that  $end \notin Act_{\tau}$ , its infinite extension  $e(\pi)$ , and an  $FLTL_f$  formula  $\phi$ . We show that the problem of checking the satisfaction of  $\phi$  can be reduced to checking its equivalent formula  $\phi'$  on  $e(\pi)$ .

**Theorem 5.1** Let  $\Phi$  be a set of fluents, where  $END \notin \Phi$ ,  $\phi$  be an  $FLTL_f$  formula defined over the set  $\Phi$ , and  $\phi'$  be the formula constructed using the  $FLTL_f$  2FLTL procedure. The FLTL formula  $\phi'$  is equivalent to  $\phi$ .

*Proof Sketch* We show that  $\pi \models \phi \Leftrightarrow e(\pi) \models \phi'$  holds in the base case, when  $\phi$  is a fluent, and that it also holds when temporal operators are considered.

Consider the finite interpretation  $\rho$  of  $\pi = e_0, e_1, \ldots, e_n$  and the infinite interpretation  $\rho'$  of  $e(\pi)$ . For every  $Fl \in \Phi$  and position i such that  $i \leq n$ , where n is the length of the finite trace,  $\rho_i \models Fl \Leftrightarrow \rho'_i \models Fl'$  by construction. Furthermore, for every  $Fl \in \Phi$  and position i such that i > n,  $\rho_i \not\models Fl$  and  $\rho'_i \not\models Fl'$ .

For operators  $\neg$  and  $\land$ ,  $\rho \models \neg \phi \Leftrightarrow \rho'_i \models \neg \text{FLTL}_f 2\text{FLTL}(\phi)$  and  $\rho \models \phi_1 \land \phi_2 \Leftrightarrow \rho'_i \models \text{FLTL}_f 2\text{FLTL}(\phi_1) \land \text{FLTL}_f 2\text{FLTL}(\phi_2)$  by construction.

Consider the operator  $\bigcirc$ . If i < n,  $\rho_i \models \bigcirc \phi$  if and only if  $\rho_i' \models \bigcirc$  (FLTL $_f$ 2FLTL( $\phi$ )), since *END* is *false* if i < n. If  $i \ge n$ , then, by Definition 5.2,  $\rho_i \not\models \bigcirc \phi$ , but also  $\rho_i' \models \bigcirc false$  by Definition 5.6 and the fact that *END* is *true*. Consider the operator  $\mathcal{U}$ . If i < n,  $\rho_i \models \phi_1 \mathcal{U} \phi_2$  if and only if  $\rho_i' \models \text{FLTL}_f 2\text{FLTL}(\phi_1) \mathcal{U}(\text{FLTL}_f 2\text{FLTL}(\phi_2))$  by Definition 5.6 and the fact that *END* is *false*. If  $i \ge n$ , then, by Definition 5.2,  $\rho_i \not\models \phi_1 \mathcal{U} \phi_2$ . However,  $\rho_i' \models \text{FLTL}_f 2\text{FLTL}(\phi_1) \mathcal{U} false$ , is also always *false*, since *END* is *true*.

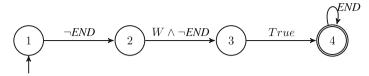

Consider the finite trace shipInfoReq, costAndTime, prodInfoReq, infoRcvd, of the LTS<sub>f</sub> shown in Fig. 3e and its infinite extension shipInfoReq, costAndTime, prodInfoReq, infoRcvd,  $end^{\omega}$ . The satisfaction of the FLTL<sub>f</sub> formula  $\phi = \bigcirc(W)$ , where  $W = \langle \{shipInfoReq, prodInfoReq\}, \{costAndTime, infoRcvd\}, false \rangle$ , on the finite trace can now be checked by evaluating the satisfaction of the formula  $\phi = \bigcirc(W \land \neg END)$  on its infinite extension.

We show that checking satisfaction of an  $FLTL_f$  formula on  $LTS_f$  can be reduced to checking the corresponding FLTL formula on an LTS.

**Theorem 5.2** Let  $\phi$  be an FLTL $_f$  formula and  $F = \langle Q, q_0, A, \Delta, Q_f \rangle$  be an LTS $_f$  model. If  $\phi'$  is the FLTL formula equivalent to  $\phi$  and  $F' = \langle Q, q_0, A \cup \{end\}, \Delta' \rangle$  is an LTS such that  $\Delta' = \Delta \cup \{(q, end, q) \mid q \in Q_f\}$ , then  $F \models \phi \Leftrightarrow F' \models \phi'$ .

Intuitively, F' is replaced by adding a self-loop labeled with the event *end* to all of the final states of the LTS<sub>f</sub>. Consider for example the LTS<sub>f</sub> presented in Fig. 3e. The FLTL<sub>f</sub> formula  $\phi = \bigcirc(W)$  can be checked by verifying that the formula  $\phi = \bigcirc(W \land \neg END)$  holds on the LTS obtained by an *end* self-loop to the state 2.5. In the rest of this paper, we refer to this procedure as CHECKFLTL<sub>f</sub>ONLTS<sub>f</sub>.

We now provide the proof of Theorem 5.2.

*Proof Sketch* The infinite traces of the LTS F' are the infinite extensions of the finite traces of F; thus, by Theorem 5.1, the proposed procedure is correct.

# 5.3. Synthesizing LTS $_f$ from FLTL $_f$ formulae

Given an  $FLTL_f$  formula  $\phi$ , we show how to construct an  $LTS_f$  such that its finite traces are exactly those that satisfy formula  $\phi$ .

**Definition 5.7** We define an FLTL *end formula*  $\phi_{end}$  as  $\Diamond(END) \wedge \Box(END \rightarrow \bigcirc(END))$ .

**Lemma 5.1** Let  $\pi$  be an infinite trace and  $\phi_{end}$  be an FLTL formula defined via Definition 5.7. If  $\pi \models \phi_{end}$ , then  $\pi$  has the form  $e_0, e_1, \ldots, e_n, \{end\}^{\omega}$ .

*Proof Sketch* The subformula  $\diamondsuit(END)$  forces the END fluent to eventually hold. The subformula  $\square(END) \to \bigcirc(END)$ ) specifies that globally if the END fluent holds, it must hold in the next position. Since the set of the initiating events of the END fluent only contains the event end and the set of the terminating events is  $Act_{\tau}$ , event end must occur at some position n+1, and in any position  $i \geq n+1$ .

We also define an operator that converts a BA into an LTS<sub>f</sub> and a procedure that removes  $\tau$ -labeled transitions from a LTS<sub>f</sub>.

**Definition 5.8** Let  $B = \langle Q, q_0, A, \Delta, Q_a \rangle$  be BA. The LTS<sub>f</sub>  $F = \langle Q, q_0, A, \Delta, Q_f \rangle$  is the *conversion* of the BA B, denoted  $F = \text{BA2LTS}_f(B)$ , if  $Q_f = Q_a$ .

**Definition 5.9** Let  $F = \langle Q, q_0, A, \Delta, Q_f \rangle$  be an LTS<sub>f</sub>.  $F' = \text{REMOVE}_{\tau}(F)$  is an LTS<sub>f</sub>  $\langle Q, q_0, A, \Delta', Q_f \rangle$ , such that any transition  $(q_i, e, q_j) \in \Delta'$  satisfies one of the following conditions: (i)  $e \neq \tau$ ; or (ii)  $(q_i, \tau, q_{i+1}), (q_{i+1}, \tau, q_{i+2}), \dots (q_{j-2}, \tau, q_{j-1}), (q_{j-1}, e, q_j)$  and  $e \neq \tau$ .

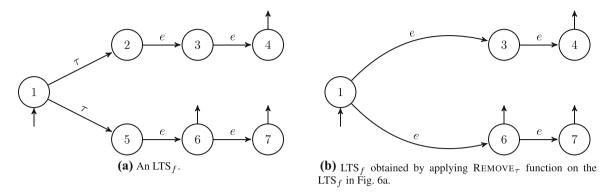

**Fig. 6.** An example usage of the procedure REMOVE<sub> $\tau$ </sub>

In essence, sequences of  $\tau$ -labeled transitions that connect a state  $q_i$  to a state  $q_{j-1}$  followed by a transition to a state  $q_j$  labeled with some symbol  $e \neq \tau$  are replaced by a transition from  $q_i$  to  $q_j$  labeled with e. Consider, for example, the LTS in Fig. 6a. The procedure REMOVE $_{\tau}$  generates the LTS in Fig. 6b. The transitions  $(1, \tau, 2), (2, e, 3)$  are replaced by the single transition (1, e, 3), and  $(1, \tau, 5), (5, e, 6)$  are replaced by (1, e, 6).

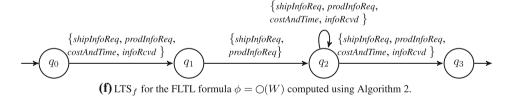

Algorithm 2 describes a procedure for computing an LTS<sub>f</sub> model F whose finite traces satisfy the FLTL<sub>f</sub> formula  $\phi$ . We discuss the steps of our algorithm using an example FLTL<sub>f</sub> formula  $\phi = \bigcirc(W)$ , where  $W = \langle \{shipInfoReq, prodInfoReq\}, \{costAndTime, infoRcvd\}, false \rangle$ . The algorithm begins by transforming  $\phi$  to FLTL via the procedure FLTL<sub>f</sub>2FLTL (Definition 5.6). For example, the FLTL<sub>f</sub> formula  $\phi = \bigcirc(W)$  is transformed into the FLTL formula  $\phi' = \bigcirc(W \land \neg END)$ . The algorithm then constructs a BA by conjoining the FLTL formula and the end formula  $\phi_{end}$  and applying the procedure LTL2BA (Line 3). In our example, the BA in Fig. 7a is computed from the FLTL formula  $\bigcirc(W \land \neg END) \land \bigcirc END \land \square(END \rightarrow \bigcirc(END))$ . Then the algorithm computes the parallel composition of the BA obtained from the formula  $\phi' \land \phi_{end}$  and the BA obtained by applying the function LTS2BA to the parallel composition of the fluent and the synchronizer automata (Line 4), resulting in an automaton whose infinite traces satisfy the FLTL<sub>f</sub> formula, and interleaves the occurrence of the fluents and the events. In our example, the fluent automata associated with the fluents W and END are shown in Figs. 7b and 7c, and the synchronizer is shown in Fig. 7d. A portion of the intersection between their parallel composition and the BA obtained from the FLTL formula  $\phi' \land \phi_{end}$  is shown in Fig. 7e. Then, Algorithm 2 converts the parallel composition into an LTS (see Definition 5.8) and hides transitions labeled with fluents and the event end. In our example, the transitions from 2 to 3, from 4 to 5, from 6 to 7, from 7 to 8, from 8 to 9, from 9 to 8 and from 12 to 13 in Fig. 7e are hidden, i.e., they are relabeled using the  $\tau$  symbol. The final step, on Line 7, removes  $\tau$ -transitions and returns. In our example, the LTS<sub>f</sub> for the FLTL formula  $\phi = \bigcirc(W)$  is shown in Fig. 7f.

**Theorem 5.3** Let  $\phi$  be an FLTL<sub>f</sub> formula. Algorithm 2 generates an LTS<sub>f</sub> such that its finite traces are exactly those that satisfy the formula  $\phi$ .

*Proof Sketch* We prove the correctness by construction. Line 3 forces each infinite trace of A to finish with an infinite sequence of END fluents (Lemma 5.1). Thus, the BA reaches an accepting state from which only transitions labeled with the END fluent can be fired. By Theorem 5.1,  $\phi'$  is equivalent to  $\phi$ , so for every infinite trace extension  $e(\pi)$ , if  $\pi \models \phi \Leftrightarrow e(\pi) \models \phi'$ . Thus, the BA generated in Line 3 contains infinite traces that are extensions of finite traces  $\pi$  that satisfy the formula  $\phi$ . Line 4 computes an automaton that interleaves fluents and events and ensures that the traces generated by the sequences of events satisfy the property  $\phi$ , as described in Sect. 4.4. Then, the BA is converted into an LTS<sub>f</sub> (Line 5). Transitions labeled with fluents and the event *end* are hidden (Line 6). This procedure ensures, by construction, that the traces reaching the final states of the returned LTS<sub>f</sub> are exactly those traces that satisfy the formula  $\phi$ .

<sup>1</sup> For simplicity of presentation, we presented only states 8 and 9, but Algorithm 4.7 generates three copies of these states, for labels {0, 1, 2}.

(a) BA generated from the FLTL formula  $\bigcirc(W \land \neg END) \land \Diamond END \land \Box(END \rightarrow \bigcirc(END))$ .

(b) Fluent automaton associated with the fluent (c) Fluent automaton associated with the flu- foReq, pr ent END.

(d) Synchronizer automaton associated with and the set of events *shipInfoReq*, *prodInfoReq*, *costAndTime*, *infoRcvd*, *end* and the fluents *END* and *W*.

(e) A portion of the automaton  $\mathcal{I}^{1}$ .

**Fig. 7.** Application of the steps of Algorithm 2 over the formula  $\bigcirc(W)$

# **Algorithm 2** Transforms an $FLTL_f$ formula into an equivalent $LTS_f$ .

```

1: function \operatorname{FLTL}_f 2 \operatorname{LTS}_f(\phi, Fl_1, Fl_2, Fl_3, \dots, Fl_n, Sync)

2: \phi' \Leftarrow \operatorname{FLTL}_f 2\operatorname{FLTL}(\phi)

3: A \Leftarrow \operatorname{LTL2BA}(\phi' \land \phi_{end})

4: B \Leftarrow A \cap \operatorname{LTS2BA}(Fl_1 \parallel Fl_2 \parallel Fl_3 \dots \parallel Fl_n \parallel Sync)

5: C \Leftarrow \operatorname{BA2LTS}_f(B)

6: D \Leftarrow C \setminus \{\Phi \cup \{END, end\}\}

7: return \operatorname{REMOVE}_r(D)

```

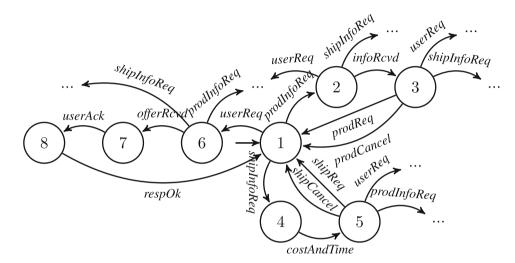

Fig. 8. The environment  $\mathcal{E}$  obtained by computing the parallel composition of the LTS in Figs. 1a, 1b and 1c

#### 6. Modeling notation

This section presents the modeling notation proposed in FIDDle to support the modular, distributed, and iterative development of software controllers. Section 6.1 describes how to model the environment in which the components under development will eventually be deployed. Section 6.2 describes how to provide a high-level model of the components. Section 6.3 describes how pre- and post-conditions can be added to the high level model to facilitate distributed development. Section 6.4 describes how unspecified components can be refined into sub-components by exploiting their pre- and post-conditions.

In the rest of this section, we capitalize generic entities specified in a given modeling formalism and denote specific software development entities using caligraphic fonts. For example, a generic LTS can be indicated by L, while the LTS modeling the behavior of the environment is denoted by  $\mathcal{E}$ .

# 6.1. Modeling the environment

The development workflow proposed in FIDDle (Sect. 3) assumes that a model of the environment is initially designed by developers (or provided by a third party) and is not changed during the iterative refinement rounds. FIDDle receives the model of the environment specified through an LTS. The LTS of the environment ( $\mathcal{E}$ ) can be obtained by composing several LTS using the parallel composition operator (Definition 4.4). Each of these LTS models is a component of the environment. For example, the LTS of the environment of the p&d example is obtained via the parallel composition of the LTS described in Figs. 1a, 1b and 1c. The complete model of the environment has 45 states and 174 transitions. A portion of the parallel composition is shown in Fig. 8. Since the alphabets of the three LTS are disjoint, all the transitions are interleaved.

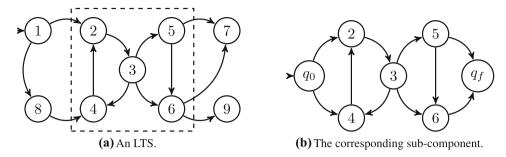

# 6.2. Initial component design

We propose partial (finite) LTS (PLTS) as a formalism to support the high level design of a component under development. A Partial (finite) Labeled Transition System is an LTS (resp. LTS<sub>f</sub>) where some states are "regular" and others are "black-box". Black-box states model portions of the component whose behavior still has to be specified. Each black-box state is augmented with an interface that specifies the universe of events that can occur in the black-box. Partial LTS are used to design an initial component model, partial finite LTS—to define sub-components (see Sect. 6.4).

**Definition 6.1** Let  $F = \langle Q, q_0, A, \Delta, Q_f \rangle$  be an LTS<sub>f</sub>. A Partial Finite Labeled Transition System (PLTS<sub>f</sub>) is a structure  $P = \langle F, R, B, \sigma \rangle$ , where:

- R is the set of regular states;

- B is the set of black-box states;

- $Q = R \cup B$  and  $R \cap B = \emptyset$ ;

- $\sigma: B \to 2^A$  is the *interface*.

Let  $L = \langle Q, q_0, A, \Delta \rangle$  be an LTS. A Partial Labeled Transition System (PLTS) is a structure  $P = \langle L, R, B, \sigma \rangle$  defined as above.

LTS (resp. LTS<sub>f</sub>) are PLTS (resp. PLTS<sub>f</sub>), where the set of black-box states is empty. For example, the initial design of a component that interacts with the furniture-sale, the shipping service and the user is represented in Fig. 3d. The interfaces of its black-box states are documented in Fig. 3c. The component is defined over the regular states 1 and 3, and the black-box states 2, 4 and 5. When a user request is received (event userReq), the black-box state 2 is entered. This black-box state represents an unspecified functionality for computing an offer to the user. The interface specifies that events prodInfoReq, infoRcvd, shipInfoReq and costAndTime can occur while the component is in the black-box state 2. The system exits this black-box state via a transition labeled with the event offerRcvd. After leaving the unspecified component, the system enters one of the black-box states: 4, if the user accepts the offer (event userAck) or 5, if it refuses it (event userNack). In turn, these black-box states represent unspecified components that are executed in response to a user request. The interfaces of the black-box states 4 and 5 specify that the events prodReq, shipReq and prodCancel, shipCancel can occur while the component is in the black-box states 4 and 5, respectively.

**Definition 6.2** Let  $L = \langle Q, q_0, A, \Delta \rangle$  be an LTS,  $P = \langle L, R, B, \sigma \rangle$  be a PLTS, and  $D = \langle Q_D, q_{0,D}, A_D, \Delta_D \rangle$  be an LTS. The *parallel composition*  $P \parallel D$  is an LTS  $S = \langle Q \times Q_D, \langle q_0, q_{0,D} \rangle, A \cup A_D, \Delta_S \rangle$ , where  $\Delta_S$  is defined as follows:

(i)

$$\frac{(q, e, q') \in \Delta}{(\langle q, t \rangle, e, \langle q', t \rangle) \in \Delta_S}$$

, and  $e \in A \setminus A_D$  or  $e = \tau$ ;

- (ii)  $\frac{(t, e, t') \in \Delta_D}{(\langle q, t \rangle, e, \langle q, t' \rangle) \in \Delta_S}$ , and one of the following is satisfied:

- (a)  $e \in A_D \setminus A$ ;

- (b)  $e = \tau$ ;

- (c)  $q \in B$  and  $e \in \sigma(q)$ .

$$(iii) \ \frac{(q,\,e,\,q') \in \Delta, (t,\,e,\,t') \in \Delta_D}{(\langle q,\,t\rangle,\,e,\,\langle q',\,t'\rangle) \in \Delta_S} \ \text{and} \ e \in A \cap A_D, \, e \neq \tau.$$