Abstract

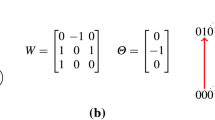

The behavior of sequential gate networks can be represented mathematically by using a binary model of gates. Unfortunately, the analysis algorithms in such a model grow exponentially with the number of gates. In this paper we describe an analysis method based on a ternary model of gates, which leads to algorithms that grow linearly with the number of gates.

It is also shown that the ternary model is ‘less accurate’ in the sense that some information may be lost.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

M. Yoeli and S. Rinon, ‘Application of Ternary Algebra to the Study of Static Hazards’, J. Assoc. Comp. Mach. 11 (1964), 84 - 97.

E. B. Eichelberger, ‘Hazard Detection in Combinational and Sequential Switching Circuits’, IBM J. Res. Dev. 9 (1965), 90 - 99.

M. A. Breuer, ‘A Note on Three-Valued Logic Simulation’, IEEE Trans. Comp. C-21 April (1972), 399 - 402.

J. A. Brzozowski and M. Yoeli, ‘Models for Analysis of Races in Sequential Networks’, in “Mathematical Foundation of Computer Science” (A. Blikle, ed.), pp. 26-32, Lecture Notes in Computer Science, vol. 28, Springer-Verlag, Berlin, 1975.

J. A. Brzozowski and M. Yoeli, Digital Networks, Prentice-Hall Inc., Englewood Cliffs, N. J., 1976.

J. A. Brzozowski and M. Yoeli, ‘A Practical Approach to Asynchronous Gate Net-works’, Proc. IEE 123 (1976), 495 - 498.

J. A. Brzozowski and M. Yoeli, ‘On a Ternary Model of Gate Networks’, Research Report CS-76-40, Dept. of Computer Science, University of Waterloo, Waterloo, Ont., Canada, September 1976.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 1977 D. Reidel Publishing Company Dordrecht-Holland

About this chapter

Cite this chapter

Yoeli, M., Brzozowski, J.A. (1977). Ternary Simulation of Binary Gate Networks. In: Dunn, J.M., Epstein, G. (eds) Modern Uses of Multiple-Valued Logic. Episteme, vol 2. Springer, Dordrecht. https://doi.org/10.1007/978-94-010-1161-7_3

Download citation

DOI: https://doi.org/10.1007/978-94-010-1161-7_3

Publisher Name: Springer, Dordrecht

Print ISBN: 978-94-010-1163-1

Online ISBN: 978-94-010-1161-7

eBook Packages: Springer Book Archive