Abstract

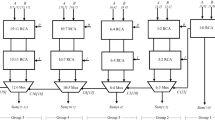

In electronic applications, better performance of the digital systems can be achieved using a faster adder circuit. This paper shows a modified carry-select adder (CSA) architecture which has low power and reduced area compared to the regular CSA. This high speed CSA is achieved by replacing the existing binary to excess-1 converter (BEC-1) with D-latch enabled CSA. Regular square-root CSA (SQRT CSA) architectures have also been developed and compared with the proposed BEC-1 D-latch enabled CSA. This work evaluates the performance of delay, area, power, and their products for existing and proposed CSA designs. This shows that proposed D-latch CSA structure is better than the regular and modified SQRT CSA and existing Ripple CSA. The proposed CSA architecture requires approximately 86 % fewer gates and 77 % shorter delay than the original CSA designs.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Mugilvannan, L., Ramasamy, S.: Low-power and area-efficient Carry Select Adder using modified BEC-1 converter. In: IEEE 4th ICCCNT 2013, 4–6 July 2013, Tiruchengode, India

Yasmeen, W., Sandhya Rani, M.: Area efficient Carry Select Adder using binary excess code. In: International Conference on Advances in Computer Theory and Engineering, 04 Aug 2013, Bengaluru. ISBN: 978-93-83060-08-5

Hemima, R., Chrisjin Gnana Suji, C.: Design of 4 bit low power Carry Select Adder. In: Proceedings of 2011 International Conference on Signal Processing, Communication Computing and Network Technologies (ICSCCN 2011)

Edison, A.J., Manikandababu, C.S.: An efficient CSLA architecture for VLSI hardware implementation. In: International Conference of Management, IT and Engineering, vol. 2, issue 5, May 2012

Ramkumar, B., Kittur, H.M.: IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 20(2) (2012)

Rama Krishna Reddy, J., Rakesh Chowdary, G., Venkata Rama Krishna, T.: High speed Carry Select Adder for ALU blocks. Int. J. Eng. Technol. 5(3) (2013)

Paradhasaradhi, D., Anusudha, K.: An area efficient enhanced SQRT Carry Select Adder. Int. J. Eng. Res. Appl. 3(6), 876–880 (2013). ISSN: 2248-9622

Saxena, P., Purohit, U., Joshi, P.: Analysis of low power, area efficient and high speed fast adder. Int. J. Adv. Res. Comput. Commun. Eng. 2(9) (2013)

Devi, P., Girdher, A., Singh, B.: Improved Carry Select Adder with reduced area and low power consumption. Int. J. Comput. Appl. 3(4) (2010)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2016 Springer India

About this paper

Cite this paper

Sakshi Bhatnagar, Harsh Gupta, Swapnil Jain (2016). Modified D-Latch Enabled BEC1 Carry-Select Adder with Low Power-Delay Product and Area Efficiency. In: Afzalpulkar, N., Srivastava, V., Singh, G., Bhatnagar, D. (eds) Proceedings of the International Conference on Recent Cognizance in Wireless Communication & Image Processing. Springer, New Delhi. https://doi.org/10.1007/978-81-322-2638-3_51

Download citation

DOI: https://doi.org/10.1007/978-81-322-2638-3_51

Published:

Publisher Name: Springer, New Delhi

Print ISBN: 978-81-322-2636-9

Online ISBN: 978-81-322-2638-3

eBook Packages: EngineeringEngineering (R0)