Abstract

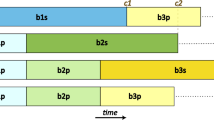

In this paper, a new dynamic Parallel Execution Architecture, DEAL, which can execute the dynamic parallel threads and handle the dynamically incorrect data access caused by parallel execution threads efficiently, is proposed. DEAL combines the concept of multi-thread speculation with the transactional memory into a new model and then threads can be efficiently executed in parallel in it. DEAL can detect incorrect parallel data access immediately and resolve them to keep data consistent among threads and ensure the threads do not violate the data dependences during parallel execution dynamically. Based on experimental results, we find that the performance of parallel applications running in DEAL can be significantly faster, 1.4 speed-ups at least, than those running in sequential, which demonstrated that the DEAL can execute parallel threads and manage data and resolve incorrect data access among them efficiently.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Moore, K.E., Bobba, J., Moravan, M.J., Hill, M.D., Wood, D.A.: LogTM: Log-based Transactional Memory. In: The proceedings of the 12th Annual International Symposium on High Performance Computer Architecture (HPCA 12), Austin, TX, February 11-15 (2006)

Yen, L., Bobba, J., Marty, M.R., Moore, K.E., Volos, H., Hill, M.D., Swift, M.M., Wood, D.A.: LogTM-SE: Decoupling Hardware Transactional Memory from Caches. In: The Proceedings of the 13th Annual International Symposium on High Performance Computer Architecture (HPCA 13), Phoenix, AZ, February 10-14 (2007)

Bobba, J.: Hardware Support For Efficient Transactional and Supervised Memory Systems. Ph.D. Thesis, The University of Wisconsin - Madison (2010)

Lupon, M., Magklis, G., González, A.: Version Management Alternatives for Hardware Transactional Memory. In: Proceedings of the 9th Workshop on Memory Performance: Dealing with Applications, Systems and Architecture (MEDEA 2008), Toronto, Canada (October 2008)

Hammond, L., Wong, V., Chen, M., Carlstrom, B.D., Davis, J.D., Hertzberg, B., Prabhu, M.K., Wijaya, H., Kozyrakis, C., Olukotun, K.: Transactional Memory Coherence and Consistency. In: Procs. of the 31st Intl. Symp. on Computer Architecture (June 2004)

Cao Minh, C., Chung, J., Kozyrakis, C., Olukotun, K.: STAMP: Stanford Transactional Applications for Multi-Processing. In: Procs. of the IEEE Intl. Symp. on Workload Characterization (September 2008)

Dice, D., Shalev, O., Shavit, N.N.: Transactional Locking II. In: Dolev, S. (ed.) DISC 2006. LNCS, vol. 4167, pp. 194–208. Springer, Heidelberg (2006)

Herlihy, M., Moss, J.E.B.: Transactional Memory: Architectural Support for Lock-Free Data Structures. In: Procs. of the 20th Intl. Symp. on Computer Architecture (May 1993)

Bobba, J., Moore, K.E., Yen, L., Volos, H., Hill, M.D., Swift, M.M., Wood, D.A.: Performance Pathologies in Hardware Transactional Memory. In: Procs. of the 34th Intl. Symp. on Computer Architecture (June 2007)

Sohi, G.S., Roth, A.: Speculative multithreaded processors. Computer 34(4), 66–73 (2001)

Shaogang, W., Weixia, X., et al.: DTM: Decoupled Hardware Transactional Memory to Support Unbounded Transaction and Operating System. In: International Conference on Parallel Processing, ICPP 2009 (2009)

Bellard, F.: QEMU, a Fast and Portable Dynamic Translator. In: Proceeding of USENIX Annual Technical Conference, pp. 41–46 (2005)

Tomic, S., Perfumo, C., et al.: EazyHTM: EAger-LaZY hardware Transactional Memory. In: IEEE/ACM International Symposium on Microarchitecture, MICRO 42 (2009)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2013 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Huang, S., Jou, JM., Hsieh, CH., Lin, DY. (2013). Design of a Dynamic Parallel Execution Architecture for Multi-core Systems. In: Pan, JS., Yang, CN., Lin, CC. (eds) Advances in Intelligent Systems and Applications - Volume 2. Smart Innovation, Systems and Technologies, vol 21. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-35473-1_72

Download citation

DOI: https://doi.org/10.1007/978-3-642-35473-1_72

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-35472-4

Online ISBN: 978-3-642-35473-1

eBook Packages: EngineeringEngineering (R0)