Abstract

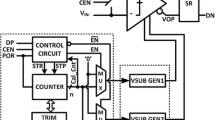

In this paper, we have modified a low-voltage, low- power VT (Threshold Voltage) extractor circuit, and by doing this we have obtained results with greater accuracy. At the same time, the output generated from this circuit is found to be robust enough against supply voltage variations. This scheme is based on the most popular extraction algorithm which essentially starts with Id versus VGS characteristics of any MOS transistor operating in saturation. Here the VT extractor block is followed by an offset generator and a feedback block. Now, for the purpose of modification, we have mainly changed the architecture of the offset generator block, keeping rest of the basic blocks unaltered. While doing this we have achieved more accurate results at low supply voltage ranging from 1.2 to 1.8V. In this range, for almost all the cases we found results with excellent accuracy. Whereas, considering the worst case scenario, the maximum deviation from the SPICE-VT value is found to be only 2.9%. Low power consumption, self-compensation for any second-order effect etc. are the key features for this modified architecture. The paper describes the VT extraction scheme, as well as, illustrates the techniques and circuit architecture required for the purpose. The results are supported by SPICE simulations.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Wang, Z.: Automatic V T Extractors Based on An nxn2 MOS Transistor Array and Their Application. IEEE J. Solid-State Circuits, 1277–1285 (1992)

Kang, S.M., Leblebici, Y.: CMOS Digital Integrated Circuits. Tata McGraw Hill Education Private Limited, New Delhi (2010)

Yu, C.G., Geiger, R.L.: An Accurate and Matching-free Threshold Voltage Extraction Scheme for MOS Transistors. In: Proc. IEEE International Symposium on Circuits and Systems, vol. 4, pp. 115–118 (1994)

Johnson, M.G.: An Input-Free V T Extractor Circuit Using a Two Transistor Differential Amplifier. IEEE J. Solid-State Circuits 28(6), 704–705 (1993)

Filanovsky, I.M.: An Input-Free V T Extractor Circuit Using a Series Connection of Three Transistors. Int. J. Electron. 82(5), 527–532 (1997)

Cilingiroglu, U., Hoon, S.K.: An Optimally Self-Biased Threshold-Voltage Extractor. IEEE Transactions on Instrumentation and Measurement 52(5) (2003)

Fikos, G., Siskos, S.: Low-Voltage, Low-Power, Accurate CMOS V T Extractor. IEEE Transactions on Circuits Systems II 48(6), 626–628 (2001)

Cilingiroglu, U., Hoon, S.K.: An Accurate Self-Bias Threshold Voltage Extractor Using Differential Difference Feedback Amplifier. In: Proc. IEEE International Symposium on Circuits and Systems, vol. 5, pp. 209–212 (2000)

Hoon, S.K., Chen, J.: Threshold Voltage Extraction Circuit. Texas Instruments incorporated, United States patent, patent no. US 6844772B2 (2005)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2012 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Dasgupta, R., Saha, D., Samanta, J., Chatterjee, S., Sarkar, C.K. (2012). Implementation of a New Offset Generator Block for the Low-Voltage, Low-Power Self Biased Threshold Voltage Extractor Circuit. In: Rahaman, H., Chattopadhyay, S., Chattopadhyay, S. (eds) Progress in VLSI Design and Test. Lecture Notes in Computer Science, vol 7373. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-31494-0_18

Download citation

DOI: https://doi.org/10.1007/978-3-642-31494-0_18

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-31493-3

Online ISBN: 978-3-642-31494-0

eBook Packages: Computer ScienceComputer Science (R0)