Abstract

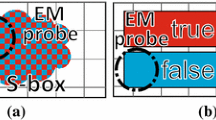

Early propagation effect (EPE) is a critical problem in conventional dual-rail logic implementations against Side Channel Attacks (SCAs). Among previous EPE-resistant architectures, PA-DPL logic offers EPE-free capability at relatively low cost. However, its separate dual core structure is a weakness when facing concentrated EM attacks where a tiny EM probe can be precisely positioned closer to one of the two cores. In this paper, we present an PA-DPL dual-core interleaved structure to strengthen resistance against sophisticated EM attacks on Xilinx FPGA implementations. The main merit of the proposed structure is that every two routing in each signal pair are kept identical even the dual cores are interleaved together. By minimizing the distance between the complementary routings and instances of both cores, even the concentrated EM measurement cannot easily distinguish the minor EM field unbalance. In PA-DPL, EPE is avoided by compressing the evaluation phase to a small portion of the clock period, therefore, the speed is inevitably limited. Regarding this, we made an improvement to extend the duty cycle of evaluation phase to more than 40 percent, yielding a larger maximum working frequency. The detailed design flow is also presented. We validate the security improvement against EM attack by implementing a simplified AES co-processor in Virtex-5 FPGA.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Kocher, P., Jaffe, J., Jun, B.: Differential Power Analysis. In: Wiener, M. (ed.) CRYPTO 1999. LNCS, vol. 1666, pp. 388–397. Springer, Heidelberg (1999)

Suzuki, D., Saeki, M.: Security Evaluation of DPA Countermeasures Using Dual-Rail Pre-charge Logic Style. In: Goubin, L., Matsui, M. (eds.) CHES 2006. LNCS, vol. 4249, pp. 255–269. Springer, Heidelberg (2006)

He, W., De La Torre, E., Riesgo, T.: A Precharge-Absorbed DPL Logic for Reducing Early Propagation Effects on FPGA Implementations. In: 6th IEEE International Conference on ReConFigurable Computing and FPGAs, Cancun (2011)

Guilley, S., Chaudhuri, S., Sauvage, L., Graba, T., Danger, J.-L., Hoogvorst, P., Vong, V.-N., Nassar, M.: Place-and-Route Impact on the Security of DPL Designs in FPGAs. In: HOST, pp. 29–35. IEEE Computer Society (2008)

Guilley, S., Chaudhuri, S., Sauvage, L., Graba, T., Danger, J.-L., Hoogvorst, P., Vong, V.-N., Nassar, M.: Shall we trust WDDL? In: Future of Trust in Computing, Berlin, vol. 2 (2008)

Chen, Z., Zhou, Y.: Dual-Rail Random Switching Logic: A Countermeasure to Reduce Side Channel Leakage. In: Goubin, L., Matsui, M. (eds.) CHES 2006. LNCS, vol. 4249, pp. 242–254. Springer, Heidelberg (2006)

Popp, T., Kirschbaum, M., Zefferer, T., Mangard, S.: Evaluation of the Masked Logic Style MDPL on a Prototype Chip. In: Paillier, P., Verbauwhede, I. (eds.) CHES 2007. LNCS, vol. 4727, pp. 81–94. Springer, Heidelberg (2007)

Popp, T., Mangard, S.: Masked Dual-Rail Pre-charge Logic: DPA-Resistance Without Routing Constraints. In: Rao, J.R., Sunar, B. (eds.) CHES 2005. LNCS, vol. 3659, pp. 172–186. Springer, Heidelberg (2005)

Nassar, M., Bhasin, S., Danger, J.-L., Duc, G., Guilley, S.: BCDL: a High Speed Balanced DPL for FPGA with Global Precharge and No Early Evaluation. In: Proc. Design, Automation and Test in Europe, pp. 849–854. IEEE Computer Society, Dresden (2010)

Bhasin, S., Guilley, S., Flament, F., Selmane, N., Danger, J.-L.: Countering Early Evaluation: an Approach towards Robust Dual-Rail Precharge Logic. In: WESS. ACM, Arizona (2010)

Tiri, K., Verbauwhede, I.: A Logic Level Design Methodology for a Secure DPA Resistant ASIC or FPGA Implementation. In: Proc. Design, Automation and Test in Europe, pp. 246–251. IEEE Computer Society (2004)

Velegalai, R., Kaps, J.-P.: DPA Resistance for Light-Weight Implementations of cryptographic Algorithms on FPGAs. In: IEEE (FPL) Field Programmable Logic and Applications, pp. 385–390 (2009)

Velegalati, R., Kaps, J.-P.: Improving Security of SDDL Designs Through Interleaved Placement on Xilinx FPGAs. In: 21st IEEE International Conference on Field Programmable Logic and Applications, Crete, Greece (2011)

Yu, P., Schaumont, M.: Secure FPGA circuits using Controlled Placement and Routing. In: 5th IEEE International Conference on Hardware/Software Codesign and System Synthesis, pp. 45–50 (2007)

Kaps, J.-P., Velegalati, R.: DPA Resistant AES on FPGA using Partial DDL. In: IEEE FCCM, Symposium on Field-Programmable Custom Computing Machines, pp. 273–280 (2010)

Lavin, C., Padilla, M., Lamprecht, J., Lundrigan, P., Nelson, B., Hutchings, B.: RapidSmith: Do-It-Yourself CAD Tools for Xilinx FPGAs. In: 21st IEEE International Conference on Field Programmable Logic and Applications, pp. 349–355 (2011)

Lavin, C., Padilla, M., Lamprecht, J., Lundrigan, P., Nelson, B., Hutchings, B.: HMFlow: Accelerating FPGA Compilation with Hard Macros for Rapid Prototyping. In: 18th IEEE Symposium on Field-Programmable Custom Computing Machines, Salt Lake City, USA (2011)

Kulikowski, K., Karpovsky, M., Taubin, A.: Power Attacks on Secure Hardware Based on Early Propagation of Data. In: IEEE, IOLTS, pp. 131–138. Computer Society (2006)

Suzuki, D., Saeki, M.: An Analysis of Leakage Factors for Dual-Rail Pre-charge Logic style. IEICE, Transactions on Fundamentals of Electronics, Communications and Computer Sciences E91-A(1), 184–192 (2008)

Soares, R., Calazans, N., Lomné, V., Maurine, P.: Evaluating the Robustness of Secure Triple Track Logic through Prototyping. In: 21st Symposium on Integrated Circuits and System Design, pp. 193–198. ACM, New York (2008)

Stine, B., Boning, D., Chung, J.: Analysis and Decomposition of Spatial Variation in Integrated Circuit Processes and Devices. IEEE Tran. on Semiconductor Manufacturing, 24–41 (1997)

Sedcole, P., Cheung, P.: Within-die Delay Variability in 90nm FPGAs and Beyond. In: Proc. IEEE International Conference on Field Programmable Technology (FPT 2006), pp. 97–104 (2006)

Maiti, A., Schaumont, P.: Improved Ring Oscillator PUF: An FPGA-friendly Secure Primitive. J. Cryptology 24, 375–397 (2010)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2012 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

He, W., de la Torre, E., Riesgo, T. (2012). An Interleaved EPE-Immune PA-DPL Structure for Resisting Concentrated EM Side Channel Attacks on FPGA Implementation. In: Schindler, W., Huss, S.A. (eds) Constructive Side-Channel Analysis and Secure Design. COSADE 2012. Lecture Notes in Computer Science, vol 7275. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-29912-4_4

Download citation

DOI: https://doi.org/10.1007/978-3-642-29912-4_4

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-29911-7

Online ISBN: 978-3-642-29912-4

eBook Packages: Computer ScienceComputer Science (R0)