Abstract

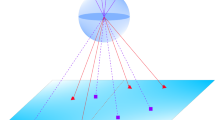

We study 3-dimensional layouts of the hypercube in a 1-active layer and a general model. The problem can be understood as a graph drawing problem in 3D space and was addressed at Graph Drawing 2003 [5]. For both models we prove general lower bounds which relate volumes of layouts to a graph parameter called cutwidth. Then we propose tight bounds on volumes of layouts of N-vertex hypercubes. Especially, we have \( {\rm VOL}_{1-AL}(Q_{\log N})= \frac{2}{3}N^{\frac{3}{2}}\log N +O(N^{\frac{3}{2}}), \) for even log N and \({\rm VOL}(Q_{\log N})=\frac{2\sqrt{6}}{9}N^{\frac{3}{2}}+O(N^{4/3}\log N),\) for log N divisible by 3. The 1-active layer layout can be easily extended to a 2-active layer (bottom and top) layout which improves a result from [5].

This research was partially supported by the VEGA grant No. 2/3164/23.

Chapter PDF

Similar content being viewed by others

References

Bel Hala, A.: Congestion optimale du plongement de l’hypercube H(n) dans la chaine P(2n). ITA 27, 465–481 (1993)

Bezrukov, S., Chavez, J.D., Harper, L.H., Röttger, M., Schroeder, U.-P.: The congestion of n-cube layout on a rectangular grid. Discrete Mathematics 213, 13–19 (2000)

Brebner, G.: Relating routing graphs and two-dimensional grids. In: Proc. VLSI: Algorithms and Architectures. North Holland, Amsterdam (1985)

Biedl, T., Thiele, T., Wood, D.R.: Three-dimensional orthogonal graph drawing with optimal volume. In: Marks, J. (ed.) GD 2000. LNCS, vol. 1984, pp. 284–295. Springer, Heidelberg (2001)

Calamoneri, T., Massini, A.: Nearly optimal three-dimensional layout of hypercube networks. In: Liotta, G. (ed.) GD 2003. LNCS, vol. 2912, pp. 247–258. Springer, Heidelberg (2004)

Calamoneri, T., Massini, A.: Optimal three-dimensional layout of interconnection networks. Theoretical Computer Science 255, 263–279 (2001)

Yeh, C.-H., Varvarigos, E.A., Parhami, B.: Multilayer VLSI layout for interconnection networks. In: Proc. Intl. Conf. on Parallel Processing, pp. 21–24 (2000)

Yeh, C.-H., Varvarigos, E.A., Parhami, B.: Efficient VLSI Layouts of hypercubic networks. In: Proc. Frontiers of Massivelly Parallel Computation, pp. 98–105 (1999)

Eades, P., Symvonis, A., Whitesides, S.: Two algorithms for three-dimensional graph drawing. In: North, S.C. (ed.) GD 1996. LNCS, vol. 1190, pp. 139–154. Springer, Heidelberg (1997)

Even, S., Kupershtok, R.: Layout area of the hypercube. Journal of Interconnection Networks 4, 395–417 (2003)

Greenberg, R.I., Lee, G.: On the area of hypercube networks. Information Processing Letters 41, 41–46 (2002)

Leighton, F.T., Rosenberg, A.L.: Three-dimensional circuit layouts. SIAM Journal on Computing 15, 793–813 (1986)

Leiserson, C.E.: Area-efficient graph layouts (for VLSI). In: Proc. 21st Annual IEEE Symposium on Foundation of Computer Science, pp. 270–281. IEEE Computer Science Press, Los Alamitos (1980)

Patel, A., Kusalik, A., McCroskey, C.: Area-efficient layouts for binary hypercubes. IEEE Transactions on Computers 49, 160–169 (2000)

Preparata, F.P.: Optimal three-dimensional VLSI layouts. Mathematical Systems Theory 16, 1–8 (1983)

Raspaud, A., Sýkora, O., Vrt’o, I.: Cutwidth of the de Bruijn graph. RAIRO 26, 509–514 (1995)

Rosenberg, A.L.: Three-dimensional VLSI: A case study. Journal of the ACM 30, 397–416 (1983)

Thompson, C.D.: Area-time complexity for VLSI. In: Proc. 11th Annual ACM Symposium on Theory of Computing, pp. 81–88 (1979)

Ullman, J.D.: Computational Aspects of VLSI. Comp. Sci. Press, Rockville (1983)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2005 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Torok, L., Vrt’o, I. (2005). Layout Volumes of the Hypercube. In: Pach, J. (eds) Graph Drawing. GD 2004. Lecture Notes in Computer Science, vol 3383. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-31843-9_42

Download citation

DOI: https://doi.org/10.1007/978-3-540-31843-9_42

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-24528-5

Online ISBN: 978-3-540-31843-9

eBook Packages: Computer ScienceComputer Science (R0)