Abstract

The design of low impedance power distribution networks is a key element in achieving high performance integrated circuits. The inductance of the power grid is a primary obstacle to achieving this goal. Proper allocation of the decoupling capacitors can significantly reduce the network impedance. The effective series resistance and inductance of a decoupling capacitor are key factors in reducing the effectiveness of the decoupling capacitor. The resonant circuit formed within the power network increases the impedance of the network near the resonant frequency. The network impedance can be reduced by a variety of power grid structures, based on area, resistance, and inductance tradeoffs. The package impedance also needs to be considered when designing a power distribution network for high performance integrated circuits.

You have full access to this open access chapter, Download chapter PDF

Similar content being viewed by others

Keywords

- Power Grid Structure

- Effective Series Resistance

- Inductance Tradeoffs

- Power Distribution Network

- Impedance Software

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

The design of low impedance power distribution networks is a key element in achieving high performance integrated circuits. The inductance of the power grid is a primary obstacle to achieving this goal. Proper allocation of the decoupling capacitors can significantly reduce the network impedance. The effective series resistance and inductance of a decoupling capacitor are key factors in reducing the effectiveness of the decoupling capacitor. The resonant circuit formed within the power network increases the impedance of the network near the resonant frequency. The network impedance can be reduced by a variety of power grid structures, based on area, resistance, and inductance tradeoffs. The package impedance also needs to be considered when designing a power distribution network for high performance integrated circuits.

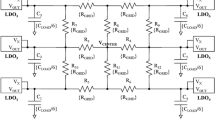

Centralized power delivery systems have recently been used to dynamically manage power in heterogeneous high performance multicore systems, requiring a long feedback path from the individual power domains to a single power management controller. Additional power is dissipated in centralized power delivery systems due to unnecessary data transport. The slow response from the long feedback path limits real-time control over the energy budget, and all of the power management functions located in one or a few places may not scale. Distributed, locally intelligent power management approaches should therefore be considered to efficiently manage the power budget in real-time. On-chip power networks with locally intelligent power routers and specialized microcontrollers are therefore reviewed in this part.

Author information

Authors and Affiliations

Rights and permissions

Copyright information

© 2016 Springer International Publishing Switzerland

About this chapter

Cite this chapter

P.-Vaisband, I., Jakushokas, R., Popovich, M., Mezhiba, A.V., Köse, S., Friedman, E.G. (2016). Conclusions. In: On-Chip Power Delivery and Management. Springer, Cham. https://doi.org/10.1007/978-3-319-29395-0_10

Download citation

DOI: https://doi.org/10.1007/978-3-319-29395-0_10

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-29393-6

Online ISBN: 978-3-319-29395-0

eBook Packages: EngineeringEngineering (R0)