Abstract

This chapter presents a computational methodology for the design optimization of ultra-low-power CMOS radio-frequency front-end blocks. The methodology allows us to explore MOS transistors in all regions of inversion. The power level is set as an input parameter before we begin the computational process involving other aspects of the design performance. The approach consists of trade-offs between power consumption and other radio-frequency performance parameters. This can help designers to seek quickly and accurately the initial sizing of the radio-frequency building blocks while maintaining low levels of power consumption. A design example shows that the best trade-offs between the most important low-power radio-frequency performances occur in the moderate inversion region.

Similar content being viewed by others

Keywords

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

1 Introduction

The design of low-power, low-cost wireless transceivers has become more significant due to the explosion of portable and ubiquitous wireless applications such as personal area networks and wireless sensor networks. These applications need to limit power consumption at microwatt level [1]. The IEEE 802.15.4 standard is introduced to satisfy this specification of low-power, low-cost, and short-range wireless communications but has relative flexibility in terms of noise, linearity, and bandwidth requirements [2].

The design of high-performance radio-frequency (RF) analog CMOS integrated circuit is still a complicated activity. Many reasons contribute to this complicity:

-

The design specifications are varied and numerous. In addition to the power consumption and bandwidth, there are some concepts which come from the circuit analysis such as gain, image rejection, signal distortion, signal-to-noise ratio (SNR), phase margin, and input/output impedance.

-

The performances of the analog circuit depend on the physical phenomena of the transistor and the passive components (resistors, capacitances and inductors) particularly in the RF domain, such as the channel length modulation, nonlinearity, and noise. The issue is the ability of transistor models to accurately express actual electrical characteristics.

These problems justify the difficulty for developing an efficient design methodology. The most used methodology is based on an intuitive approach for the behavior of the circuit and a simple model of the transistor biased in the weak or strong inversion region, while the moderate inversion is taking a high importance particularly for low-power wireless applications. On the other hand, other methodologies do not care about the physical behavior and are based on powerful computing software to reach the design specifications after multiple attempts and simulations with different transistor parameters.

Many questions remain open for these methodologies, namely uniqueness, the quality of the found solution, the choice of the defaults values, the computing time, and the accuracy of the used MOS transistor models. In these conditions, the experience of the designer is the key to success for such methodologies.

This chapter is organized as follows: Sect. 17.2 will present some related works concerning low-power design techniques. The approach and the design description of the proposed computational design methodology will be presented in Sects. 17.3 and 17.4. To validate our approach, Sect. 17.5 will describe the design steps to follow using the proposed methodology for the design of a low-noise amplifier (LNA) at 2.4-GHz operating frequency with two different CMOS technologies (0.13 and 0.18 µm). Finally, Sect. 17.6 will present the conclusion.

2 CMOS Low-Power Design Methodologies and Techniques Review

Thanks to the development of CMOS technology, it is possible to implement gigahertz RF and microwave circuits with submicron technologies. The CMOS technology has a merit to be combined with digital circuits. The gate length, which is directly related to the effective channel length, is a main feature controlling the MOSFET performance. As CMOS technology is scaled into the nanometer range, the transit frequency (f T) and the maximum frequency of oscillation (f max) of transistors have been increased. Currently, from 50- to 100-nm gate-length MOSFETs, the transit frequency can reach 200 GHz, which allows the design of integrated circuits to operate at up to 20 GHz [3, 4].

In the literature, many researches try to reduce power consumption for different RF building blocks of the transceiver. In this context, different methods and techniques have been proposed [5–9]. In the most case, transistors for high-frequency applications are operating in strong inversion to take advantage of the high device transit frequency (f T) in this regime. Subthreshold operation is one of the low-power design approaches available. In this region, the gate source voltage is below the threshold voltage leading to a lower saturation voltages (≈100 mV), which allows the use of low supply voltage. Another advantage of this region is the high gain obtained compared to the strong inversion. However, there are some unwanted issues which make this region not attractive:

-

The tight bandwidth.

-

The high noise at the output.

-

The large transistor size increases the parasitic components which degrades some device performances such as linearity and noise.

In the design level, there are no structured or computational methodologies which can help designers during the design process when working in this region. The most published works show tentative to optimize power consumption using a large transistor width and low bias voltage. However, the rest of circuit performances are adjusted through intuitive experience or tuning process until attain some acceptable values.

In the past few years, the g m /I d method has been developed to explore the MOS transistor in all regions of operation [5]. This design method takes into account the transconductance and drain current ratio g m /I d and the normalized current I n = I d/(W/L) as the basic design parameters [6]. The value of g m /I d ratio is maximum in the weak inversion. The main advantage of this method is that the g m /I d versus I n curve is technology independent, which reduce the number of electrical device parameters related to the used process. In spite of the relevance of this method, it is less used for the design of RF building blocks.

3 Approach of the Computational Design Methodology

The design complexity of RF circuits always requires a trade-off between the different parameters that come into play in the design in order to achieve the necessary performances. On the architectural level, the current-reused technique is utilized to overcome the limitation on the supply voltage and transistor overdrive [7]. Other techniques combine RF microelectronic mechanical systems (MEMS) technology and weak inversion standard CMOS to reduce power consumption and increase the integration level [8].

Reducing power consumption while maintaining acceptable performances remains a challenge for CMOS RF circuits. Designers use their own experience to achieve these objectives by carrying out several simulation exercises and optimizations. Consequently, developing an efficient design methodology for CMOS RF building blocks has become necessary. The concept of inversion coefficient has been studied more in detail in the few last years [9]. It is a pertinent tool which provides a link between design intuition and simulation. The challenge of the designer consists in evaluating the available trade-offs in order to found the optimal circuit. The inversion coefficient method provides several simulations data which present all the device performances in all inversion regions. These data help designers to compare and make the right decision for a specific case.

The general principle of the proposed design methodology consists of four main steps:

-

1.

Fixing the three freedom parameters: the inversion coefficient (IC), the drain current I d, and channel length L, as described in Ref. [9], to find the optimum biasing point for all used MOS transistors in the circuit.

-

2.

Plotting all transistor parameters (C gs, C gd, f T, g m /I d, I d, g ds, V gs) as a function of IC to determine the performance of all used transistors at the fixed point. Where C gs is the gate source capacitance, C gd is the gate drain capacitance, f T is the transistor bandwidth, g m /I d is the transconductance efficiency, g ds represents the output conductance, and V gs is the gate source voltage.

-

3.

Extracting the analytical equations from the circuit which defines the performance key parameters (expressions of gain, matching condition, bandwidth, linearity, noise figure, etc.). In this step, the parasitic elements of passive components must be also taken into account in order to have the most accurate results.

-

4.

In parallel with these steps, a trade-off between the power consumption and the rest of the performance key parameters can be found depending on the target application and the wireless standard requirements. This trade-off can be reached by creating a design flow relaying RF block equations, target specifications, transistors parameters, and the final decision.

4 Hand Calculation and Automated Process Combination for Design Optimization

The design steps, developed before, can be summarized in three phases during the design process:

-

The first phase consists of SPICE simulation, of the used PMOS or NMOS transistor, with a CAD tool performed by sweeping the bias voltage V gs. The objective is to show the performances of the device as a function of IC.

-

The second phase consists of an analytical study of the whole circuit. Generally, the expression of the design performances such as gain, noise, distortion, and matching conditions can be determined through a small-signal equivalent circuit. This last takes into account the most parasitic components. This method compensates the inaccuracy which is not supported in the SPICE model used by the CAD simulation generated in the first phase. Short-channel effect, gate resistance, and other parasitic elements in MOS model or passives components (i.e., series resistance of integrated inductor) can be introduced in the extracted equations. This methodology provides the possibility to determine the design performances by hand calculation, and some developed automated program or combination between the two ways. The calculated results will be compared to the fixed specifications and objectives. This choice between hand calculation or automated tool depends on the nature of the studied RF block. For a simple RF block where only one node and a few number of passive components are integrated, hand calculation can be an optimal choice. For other RF blocks, which use a complicated architecture with many nodes and passives component, a generic program is helpful to increase productivity and saving time. In some cases, the combination of two methods can be a solution, and designer can calculate one performance (i.e., gain) with hand calculation and other figures of merit with automated process (i.e., distortion).

-

The third phase consists of the creation of a design flow for the studied RF block to determine sequentially the figure of merit priority. It is the first step of the trade-off.

Depending on the role of the RF block, the priority can be determined. For a LNA, the gain and the noise figure are the most important figures of merit because they affect the entire receiver. According to our approach, the power consumption is the high priority. The drain current Id appears as a predefined parameter in the design flow. The simulation of the RF block can be started with the defaults calculated sizing values. In the most cases, a small tuning adjustment must be done to eliminate some deviations. Figure 17.1 illustrates the approach of the proposed design methodology.

As previously reported, this method defines three degrees of design freedom: the inversion coefficient, the channel length, and the drain current. By selecting these three parameters, channel width W is easily found. In addition to channel width, the passive components and the architecture of the RF circuit affect also the key performances such as gain, bandwidth, linearity, and noise. Combining the inversion coefficient and the extracted circuit equations, an optimum trade-off can be found especially for ultra-low-power design. To show the effectiveness of the proposed methodology, the design of an important RF building block is demonstrated in the next section.

5 A Design Example: Ultra-Low-Power LNA

As described earlier, the first step in this methodology is the simulation of the MOS transistor parameters as a function of IC. For this study, two CMOS processes based on the BSIM3 model (TSMC RF 0.18 µm and TSMC RF 0.13 µm) are used in all regions of transistor operation: weak inversion for IC < 0.1, moderate inversion for 1 < IC < 10, and strong inversion for IC > 10. The objective of this comparison is to find the adequate regions and subregions of inversion, which satisfies the fixed low-power RF design specifications.

The inversion coefficient is a normalized measure of MOS inversion independent of technology parameters [9]. Equation (17.1) gives the expression of the IC:

where µ 0 is the low-field mobility, n 0 is the substrate factor, C ox is the gate oxide capacitance, U T is the thermal voltage, and I 0 is a process-dependent current equal to \( 2n_{0} \mu_{0} C_{\text{ox}} U_{\text{T}}^{2} \). From Eq. (17.1), it is shown that once I 0 is known, the IC can be easily extracted from the bias current and W/L ratio.

5.1 MOS Performances Versus IC

The evolution of the gate source voltage V gs versus IC is very interesting. Indeed, this voltage must be maintained at sufficiently low values to ensure bias compliance, especially in low-voltage designs.

Figure 17.2 shows the variation of the gate source voltage V gs versus IC for both used CMOS 0.13 and 0.18-µm technologies. This curve is very important since it defines the voltage across each region. In the weak inversion, V gs is very low (65 mV below the threshold voltage V T). In the moderate region (0.1 < IC < 10), this value varies from 60 mV below V T and 200 mV above V T. In weak and moderate inversions, the drain–source saturation voltage V DSat is very low, which allows the use of low-voltage design. In strong inversion, V gs is 210 mV above V T and V ds is high.

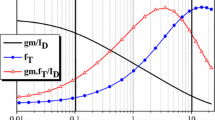

The transconductance represents the variation in the drain current I d divided by the small variation in the gate–source voltage V gs with a constant drain–source voltage V ds (∂V gs/∂V ds). Figure 17.3 shows the simulation of the transconductance g m versus IC for the two used technologies. This parameter is very important to determine the intrinsic voltage gain, the bandwidth, and the transconductance efficiency g m /I d.

Another important MOS performance parameter is the transconductance efficiency. It is the quality factor describing the production of desired transconductance for a given level of drain bias current. It is almost process-independent except for the substrate factor n.

The bandwidth is the frequency where gate-to-drain current I d gain is unity. Figure 17.5 shows f T as function of IC. Equation (17.2) gives the expression of f T:

where C gs is the gate source capacitance and C gd is the gate drain capacitance. The C gs can also be evaluated in terms of IC. The expression of the gate–source capacitance in all regions of operation is given by [9]:

where C ox is the gate oxide capacitance.

The transconductance is maximum in weak inversion, and it decreases modestly in moderate inversion and drops in strong inversion as shown in Fig. 17.4.

The expression of g m /I d in all regions of operation is given by:

where U T is equal to 25.9 mV.

In the weak inversion, the drain current is proportional to the exponential of the effective gate–source (V eff = V gs − V T):

Then

Using Eq. (17.5), the substrate factor n can be easily calculated and used for extracting the technology current I 0.

A maximum bandwidth is obtained when operating in the strong inversion. This bandwidth decreases in the moderate inversion and drops in the weak inversion. The curves in Fig. 17.5 shows also the increase of the bandwidth by technology downscaling from CMOS 0.18 µm to CMOS 0.13 µm.

The intrinsic voltage gain is defined as the ratio of transconductance g m and drain–source conductance g ds:

Figure 17.6 shows the simulated voltage gain versus the coefficient inversion IC. This parameter is maximum in weak inversion (IC < 0.1) and decreases as the inversion coefficient increases.

From the previous results, it is interesting to note that the weak inversion (IC < 0.1) is characterized by a low power consumption, a good gain and a maximum transconductance efficiency, but it suffers from a low bandwidth. The region of strong inversion (IC > 10) is characterized by high power consumption, a low g m /I d, a low gain, and an excellent bandwidth. However, the moderate inversion region (0.1 < IC < 10) is characterized by a low power consumption, a good gain, a good transconductance efficiency, and a moderate bandwidth, this will allow a low-voltage design. This last region is attractive choice for the design of ultra-low-power RF circuits.

5.2 LNA Architecture Study

The most used techniques to optimize the power consumption for CMOS LNA design are the subthreshold and current reuse. In Refs. [10–12], authors use the subthreshold region to design a low-power LNA with inductive degeneration. Despite the good reached performances in terms of power consumption, the design process is different for all three references. In Ref. [11], the transistors are biased in the subthreshold region with a low supply voltage (0.6 V). In Ref. [10], the degeneration and load inductors are removed to reduce chip area. However, in Ref. [12], the authors use an unrestrained bias technique to improve linearity and gain. The unique used transistor is biased in the weak inversion with a very large width of 600 µm which increases the parasitic capacitance C gs. Another disadvantage of the proposed design in [12] is the use of three big inductors which increase the chip area. The current reuse technique is used in Refs. [13, 14] to allow a low-voltage design. The g m /I d method is explored in Ref. [15] to design a low-power LNA at 2.4 GHz. The optimum biasing point is found by using computational routines to obtain numerically the optimum noise figure for the available range of g m /I d versus a wide range of I d.

In this chapter, the proposed design methodology has been used for the design of a low-noise amplifier. This interesting RF building block is the first stage of a receiver; its main function is to provide enough gain to overcome the noise of subsequent stages (such as mixers). The LNA should provide a good linearity and should also present specific impedance, such as 50 Ω, both to the input source and to the output load. Besides, the LNA should provide low power consumption especially when it is used for wireless and mobile communication systems. Moreover, the LNA must have a good reverse isolation to prevent self-mixing.

Figure 17.7 shows the most popular topology of the LNA with inductive degeneration. This architecture has the advantage to achieve good input matching with power gain and noise for minimum power consumption [16]. Figure 17.8 shows the small-signal equivalent circuit of the proposed topology which will be used to calculate the LNA performances.

Small-signal equivalent circuit of the proposed topology [15]

As can be seen, the selected topology uses three integrated inductors. Those inductors affect the performance of the LNA especially the noise factor and the input impedance due to losses caused by the parasitic series resistances, the substrate capacitance, and the substrate resistances. To overcome this problem, a high-quality factor integrated inductor will be used. Figure 17.9 shows the inductance value and the quality factor for the used model from the design kit TSCM RF CMOS 0.13 µm.

Based on the small-signal equivalent circuit in Fig. 17.8, the expression of the input impedance can be determined by:

where R g in Eq. (17.9) represents the gate resistance. It depends on the layout of the transistor M1 and the sheet resistance of the polysilicon. \( R_{{L_{\text{g}} }} \) is the series resistance of the gate inductor L g.

Equation (17.10) shows the effective transconductance of the input stage:

where the quality factor of the input stage Q in is given by:

where

And C gs = C gs1 + C m where C gs1 is the gate–source capacitance of transistor M1. The output load is an LC resonator at the operating frequency f 0.

Taking into account all noise sources, the expression of noise figure is given by [17, 18]:

where \( \omega_{t} = \frac{{g_{m} }}{{C_{{{\text{gs}}1}} + C_{\text{gd}} }} \), \( Q_{{L_{\text{g}} }} \) is the quality factor of the gate inductor L g, \( \gamma \) is the thermal noise coefficient, and δ is the gate noise coefficient. This expression takes into account the channel gate resistance R g and the parasitic gate inductor resistance \( R_{{L_{\text{g}} }} \). These two last parameters affect directly the noise and matching performance of the LNA.

However, Eq. (17.14) presents the expression of the LNA gain [10]:

The nonlinear behavior of the MOS transistor contributes to the degradation of the quality of the signal transmission in the transceiver. Nonlinearity enables the generation of new frequencies in form of harmonics which can be mixed with the fundamental frequency causing intermodulation and distortion. There are two important performance parameters to evaluate the linearity of a RF system.

The first parameter is the 1-dB compression point which is the point where the gain falls by 1 dB. The second parameter is the third-order intercept point which measures the effect of the intermodulation. The main source of nonlinearity, but not exclusive, in the studied LNA architecture is the transistor in the first stage. The power series of the transconduction of the MOS transistor is given as follows [19]:

where

According to many investigations concerning the harmonic distortion, the coefficient g 3 in Eq. (17.15) determines the value of IIP3:

Equations (17.15) and (17.17) suppose that the MOS transistor is working in the strong inversion regime, and the variation of the drain–source voltage is neglected. In other inversion regimes, the voltage V ds must be taken into account. In our proposed methodology, the parameter IIP3 must be kept near the specified value. The performance of IIP3 must be evaluated during the trade-off phase. Many techniques are investigated to improve the linearity of the LNA. Some techniques propose changes of the used LNA architecture which is not suitable for our case. The gate biasing technique tries to improve the linearity by controlling the V gs and biasing the MOS transistor in the moderate inversion [20]. This technique is helpful while the transistor M1 will be biased in the moderate inversion near the center IC = 1. Figure 17.10 shows the variation of the three power series coefficients g 1, g 2, and g 3 versus the biasing voltage V gs. The technique reported in [20] is based on the polarization of the input transistor of the LNA in the region of moderate inversion where IIP3 maximum is reached. Thus, to optimize the linearity means reducing g 3 to a minimum value.

On the other hand, another parameter which affects the linearity in the inductive degeneration topology is the inductive feedback caused by the source inductor [21].

5.3 Step by Step LNA Design

To design a LNA using the proposed methodology for ultra-low-power applications, the designer should follow a procedure. Figure 17.11 shows the design flow.

All LNA performances parameters are computed with the help of small excel program using the extracted technology parameters of the BSIM3 model.

However, the descriptions of the different design steps of the LNA are explained thereafter:

Step 1: Choosing the optimum RF architecture for low-power design. This step is very important to avoid explicit power consumption drop. A LNA with inductive degeneration is chosen for this study.

Step 2: Fixing the desired performances: NFmax (maximum noise figure), G min (minimum power gain), IIP3min (minimum linearity), and P max (maximum power consumption). Table 17.1 shows of the desired performances for the LNA design.

Step 3: Extracting the active components which affect directly the LNA power consumption. The contribution of the second stage (M2) in terms of power consumption is very low. For this reason, this transistor is biased in the strong inversion region. Only the biasing of the transistor M1 determines the dc drain current I d .

Step 4: Extracting the passive components which affect directly the LNA performances. For the inductive degeneration architecture, the integrated inductors and particularly the series resistances of the inductors affect directly the noise figure and the 50 Ω matching input impedance of the LNA. The use of a high-quality factor \( Q_{{L_{\text{g}} }} \) of the inductor is required. However, the value of the inductance L should be kept smaller than the supported maximum value of the used technology (about 11 nH).

Step 5: Simulation of the IC and selection of the three design parameters: IC, I d , and L. The values of the chosen parameters depend on the desired performances fixed in step 2. Two parameters are already known, the channel length L = L min to provide high f T and I d = P max/V dd, where V dd is the supply voltage. For V dd = 1 V, the current drain is equal to 550 µA. From the performance of MOS transistor, the region near the center of the moderate inversion (IC = 1) represents good trade-offs in power consumption, gain, noise figure, and bandwidth. For this reason, the IC is set equal to 1.

Step 6: Setting the values of the parameters fixed in step 5 in Eqs. (17.1), (17.9), (17.12), (17.13), and (17.17). The initial sizing of the LNA can be reached.

Step 7: Seeking for optimum trade-offs in power consumption and other LNA performances through a series of simulations of various IC near the selected value (IC = 1). Table 17.2 shows the optimum sizing of the LNA for both used CMOS technologies 0.13 and 0.18 µm.

5.4 Obtained Results

In order to show the importance of the moderate region in low-power design, the LNA is simulated in the three operation regions with the adequate passive components value for only 550 µW of power consumption. Table 17.3 shows the performances of the LNA in different regions of operation using 0.18-µm CMOS process. In the weak inversion region (IC < 0.1), the power gain is dropped to 4.2 dB since the noise figure is equal to 4.2 dB. In strong inversion (IC > 10), the gain reaches 8 dB with a noise figure of 3.5 dB since the supply is set to the nominal value 1.8 V for 0.18 µm. However, in the center of moderate inversion (IC = 1), the power gain reaches 13.5 dB with 1.5 dB of noise figure. Figure 17.12 shows the simulation of the power gain and noise figure versus IC in moderate inversion region. In the subregion near the week inversion, the power gain drops to 1 dB and the noise figure drops to 5 dB. The maximum power gain and minimum noise figure are reached in the subregion near the strong inversion. Figure 17.13 shows the performance of the linearity parameter IIP3 versus IC in the moderate inversion region. The maximum value is reached for IC = 0.9 which is compatible with the analysis done in Sect. 5.2.4.

As it can be deduced from Table 17.3, the moderate inversion represents a good region for low-power design. Since the inversion coefficient IC varied from 0.1 to 10, the optimum value of IC could be determined by the simulation of IC as a function of the main required performances of the LNA. Table 17.4 shows the simulation results obtained by using 0.18-µm CMOS process for different values of IC near the center of moderate inversion region. This table shows that the obtained gain reaches 10.7 dB with 1.89 dB of noise figure for only 360 µW of power consumption, while the other performances such as the third-order input intercept point (IIP3) and inductance value are respected. These performances continue to improve by increasing the inversion coefficient value but for more power consumption. The power gain reaches 15.34 dB with 1.4 dB of noise figure for only 750 µW of power consumption. Figure 17.14 shows the simulated S parameters of the LNA using 0.13-µm CMOS process. The reflection coefficients S11 and S22 are both equal to −20 dB at 2.4 GHz industrial, scientific, and medical (ISM) frequency band for 13.5 dB of power gain and 1.5 dB of noise figure.

Figure 17.15 shows the simulated S parameters using 0.18-µm CMOS process. The power gain reaches 13.5 dB since the input matching reflection coefficient S11 is improved to −30 dB and S22 is equal to −15 dB. The simulated performance of the linearity defined by the 1-dB compression point (P 1dB) is shown in Fig. 17.16 for 0.13-µm CMOS technology. The LNA provides P 1dB = −18 dBm and IIP3 = −9.5 dBm for both used technologies.

Table 17.5 shows the LNA obtained performances in 0.18- and 0.13-µm CMOS processes compared to the state of the art. The LNA provides P 1dB = −18 dBm and IIP3 = −9 dBm for both used technologies. In this work, interesting performances of noise figure and power gain are achieved for two different technologies by comparing with other researches using different low-power RF design techniques.

6 Conclusion

In this chapter, a design methodology for ultra-low-power RF circuits has been described. The sizing of the circuit components is performed by the use of the inversion coefficient. The main advantage of the proposed methodology is the exploration of the MOS transistor in all regions of operation from weak to strong inversion. The studied example shows that the best trade-off between the most importance low-power RF performances occurs in the moderate region. This methodology contributes also for time reduction by seeking the initial sizing of the RF building blocks. The use of 0.13- and 0.18-µm CMOS technologies proves that this methodology is process-independent and can be used for other CMOS standard technologies. The moderate inversion region represents an attractive choice especially the subregion around the center of the inversion level (IC = 1) for the design of ultra-low-power RF circuits. The trade-off between power consumption and the most RF performances can be achieved in this region as it is demonstrated in this work through the example of LNA. The obtained simulation results are acceptable for low-power RF standards especially for the IEEE 802.15.4. Therefore, this methodology can be used in the design of other building blocks of a RF transceiver to ensure optimized power consumption without dropping other performances.

References

Wang, A., Calhoun, B.H., Chandrakasan, A.P., Vittoz, E.A.: Sub-Threshold Design for Ultra Low-Power Systems, pp. 7–46. Springer, Berlin (2006)

Alliance: www.zigbee.orgzigbee

Liou, J.J., Schwierz, F.: RF MOSFET: recent advances, current status and future trends. Solid State Electron. 47(11), 1881–1895 (2003)

International technology roadmap for semiconductors.: Radio frequency and analog/mixed-signal technologies summary (2013)

Silveira, F., Flandre, D., Jespers, P.G.A.: A gm/ID based methodology for the design of CMOS analog circuits and its application to the synthesis of a silicon-on-insulator micropower OTA. IEEE J. Solid State Circuits 31(9), 1314–1319 (1996)

Jespers, P.: The gm/ID Methodology a Sizing Tool for Low-Voltage Analog CMOS Circuits: The Semi-Empirical and Compact Model Approaches, 1st edn. Springer, Berlin (2009)

Hsieh, H.-H., Lu, L.-H.: Design of ultra-low-voltage RF frontends with complementary current-reused architectures. IEEE Trans. Microwave Theory Tech. 55(7), 1445 (2007)

Otis, B.P., Rabaey, J.: Ultra-Low Power Wireless Technologies for Sensor Networks. Springer, Berlin (2007)

Binkley, D.M.: Tradeoffs and Optimization in Analog CMOS Design. University of North Carolina at Charlotte, Wiley, USA (2008)

Do, A.V., Boon, C.C., Do, M.A., Yeo, K.S., Cabuk, A.: A subthreshold low-noise amplifier optimized for ultra-low-power applications in the ISM band. 286 IEEE Trans. Microwave Theory Tech. 56(2), 286 (2008)

Lee, H., Mohammadi, S.: A 3 GHz subthreshold CMOS low noise amplifier. In: Proceedings of Radio Frequency Integrated Circuits (RFIC) Symposium, Jun 2006

Perumana, B.G., Chakraboty, S., Lee, C.-H., Laskar, J.: A fully monolithic 260 µW, 1 GHz subthreshold low noise amplifier. IEEE Microw. Wireless Compon. Lett. 15(6), 428–430 (2005)

Cornetta, G., Santos, D.J.: Low-power multistage low noise amplifiers for wireless sensor networks. Int. J. Electron. 96(1), 63–77 (2009)

Rastegar, H., Hakimi, A.: A high linearity CMOS low noise amplifier for 3.66 GHz applications using current-reused topology. Microelectron. J. 44, 301–306 (2013)

Fiorelli, R.: All-inversion-region gm/ID based design methodology for radiofrequency blocks in CMOS nanometer technologies. University of Seville, Spain and Instituto de Microelectrect de Sevilla, Spain, PhD thesis, p. 124 (2011)

Tiebout, M., Paparisto, E.: LNA design for a fully integrated CMOS single chip UMTS transceiver. In: IEEE European Solid State Circuits Conference (ESSCIRC2002), Florence, Italia, pp. 825–828 (2002)

Sheaffer, D.K., Lee, T.H.: A 1.5-V, 1.5 GHz CMOS low noise amplifier. IEEE J. Solid State Circuit 32, 745 (1997)

Shaeffer, D.K., Lee, T.H.: Corrections to a 1.5-V, 1.5-GHz CMOS low noise amplifier. IEEE J. Solid State Circuits 40(6), 1397–1398 (2005)

Alvarado, U., Bistué, G., Adín, I.: Low Power RF Circuit Design in Standard CMOS Technology. Springer, Berlin (2011)

Aparin, V., Larson, L.E.: Linearization of CMOS LNA’s via optimum gate biasing. In: IEEE International Symposium on Integrated Circuit and System (ISCAS), pp. 748–751, Vancouver, CA (2004)

Toole, B., Plett, C., Cloutier, M.: RF circuit implications of moderate inversion enhanced linear region in MOSFETs. IEEE Trans. Circuits Syst. I 51(2), 319–328 (2004)

Ho, D., Mirabbasi, S.: Design considerations for sub-mW RF CMOS low-noise amplifiers. In: Vancouver Electrical and Computer Engineering, British Columbia University (2007)

Baimei, L.I.U., Wang, C., Minglin, M.A., Shengqiang, G.U.O.: An ultra-low voltage and ultra-low-power 2.4 GHz LNA design. Radioeng. 18(4), 527 (2009)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2015 Springer International Publishing Switzerland

About this chapter

Cite this chapter

Ouali, A.I., Oualkadi, A.E., Moussaoui, M., Laaziz, Y. (2015). Optimization Methodology Based on IC Parameter for the Design of Radio-Frequency Circuits in CMOS Technology. In: Fakhfakh, M., Tlelo-Cuautle, E., Siarry, P. (eds) Computational Intelligence in Analog and Mixed-Signal (AMS) and Radio-Frequency (RF) Circuit Design. Springer, Cham. https://doi.org/10.1007/978-3-319-19872-9_17

Download citation

DOI: https://doi.org/10.1007/978-3-319-19872-9_17

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-19871-2

Online ISBN: 978-3-319-19872-9

eBook Packages: Computer ScienceComputer Science (R0)