Abstract

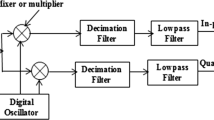

The high performance of FPGA devices allows moving traditionally analog stages into the digital world. This article introduces the implementation of a Digital Up-Converter, which is part of a broadband system. This system uses polyphase decomposition to achieve 5GSPS sampling rates. The transmitter uses 7 data channels each divided into 16 phases of 312.5 MHz. The model implements a DDS suitable to the specific needs of the system, keeping the frequencies of carrier’s constant, which reducing resource utilization and simplifying the architecture of the DDS. The model is coded in Verilog and simulated at RTL and Gate level. In order to validate the output, it is compared to a finite precision model in Matlab. The maximum clock frequency is measured using time analysis, obtaining adequate results in the operation and utilization of hardware resources.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Rittner, F., Glein, R., Thomas, K., Benjamin, B.: Broadband FPGA payload processing in a harsh radiation environment. In: Conference on Adaptive Hardware and Systems (AHS), vol. 1, no. 1, pp. 151–158 (2014)

Patil, R., Gawande, G.S.: Efficient design of a digital up converter using Xilinx system generator. Int. J. Eng. Res. Technol. (IJERT) 3(1), 2284–2286 (2014)

Yin, Y., Liao, Y.: Design and implementation micro-broadband radar signal source. In: Xing, S., Chen, S., Wei, Z., Xia, J. (eds.) Unifying Electrical Engineering and Electronics Engineering, vol. 238, pp. 1391–1398. Springer, New York (2014)

Castro, C., Gordon, C., Encalada, P., Cumbajin, M.: Multiband broadband modulator implementation on field-programmable gate array. In: International Conference on Applied Technologies (ICAT), Quito (2019)

de Figueiredo, F.A.P., Filho, J.A.B., Lenzi, K.G.: FPGA design and implementation of Digital Up-Converter using quadrature oscillator. In: 2013 IEEE Jordan Conference on Applied Electrical Engineering and Computing Technologies (AEECT), Amman, pp. 1–7 (2013). https://doi.org/10.1109/AEECT.2013.6716423

Vanka, J.: Direct Digital Synthesizers: Theory, Design and Applications. Department of Electrical and Communications Engineering - Helsinki University of Technology, Helsinki (2000)

Denis, D.C., Cordeiro, R.F., Oliveira, A.S., Viera, J., Silva, T.O.: A fully parallel architecture for designing frequency-agile and real-time reconfigurable FPGA-based RF digital transmitters. IEEE Trans. Microw. Theory Tech. 66(3), 1489–1499 (2018)

Fontes Pupo, E., Diaz Hernandez, R., Martinez Alonso, R., Hernandez Sanchez, Y., Guillen Nieto, G.: Direct to RF up-converter for DTMB modulator. In: IEEE International Symposium on Broadband Multimedia Systems and Broadcasting (BMSB), vol. 1, no. 1, pp. 1–15 (2016)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 The Editor(s) (if applicable) and The Author(s), under exclusive license to Springer Nature Switzerland AG

About this paper

Cite this paper

Castro, C., Zapata, M. (2021). Efficient FPGA Implementation of Direct Digital Synthesizer and Digital Up-Converter for Broadband Multicarrier Transmitter. In: Ahram, T. (eds) Advances in Artificial Intelligence, Software and Systems Engineering. AHFE 2020. Advances in Intelligent Systems and Computing, vol 1213. Springer, Cham. https://doi.org/10.1007/978-3-030-51328-3_57

Download citation

DOI: https://doi.org/10.1007/978-3-030-51328-3_57

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-030-51327-6

Online ISBN: 978-3-030-51328-3

eBook Packages: Intelligent Technologies and RoboticsIntelligent Technologies and Robotics (R0)