Abstract

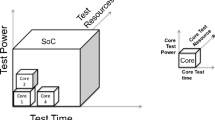

This paper considers the scheduling problem of core tests in a system. Our objective is to minimize the total system test time while respecting system constraints in terms of power consumption and test resource sharing. A simple and effective scheduling heuristic is proposed based on a no sessions based scheme for better overall test time optimisation.

The original version of this chapter was revised: The copyright line was incorrect. This has been corrected. The Erratum to this chapter is available at DOI: 10.1007/978-0-387-35597-9_40

Chapter PDF

Similar content being viewed by others

Key words

References

H.J. Wunderlich, “BIST for systems-on-a-chip”, Integration, the VLSI journal, 26, pp 55–78, 1998.

I. Ghosh, N. K. Jha, S. Dey, “A low overhead design for testability and test generation technique for core-based systems”, Proc. Int. Test Conf., pp 50–59, 1997.

E.J. Marinissen, R. Arendsen, G. Bos, H. Dingemanse, M. Lousberg, C. Wouters, “A structured and scalable mechanism for test access to embedded reusable cores”, Proc. Int. Test Conf., pp 130–143, 1998.

P Varma, S Bhatia, “A structured test re-use methodology core-based system chips”, Proc. Int. test Conf., pp 294–302, 1998.

K. Chakrabarty, “Design of system-on-a-chip test access architectures using integer linear programming”, Proc. VLSI Test Symp., pp 127–134, 2000.

R. Chou, K. Saluja, V. Agrawal, “Scheduling Tests for VLSI Systems under Power Constraints”, IEEE Trans. on VLSI Systems, Vol. 5, No. 2, pp 175–185, June 1997.

M.R. Garey, D. Jonhson: “Computers and Intractability: guide to the theory of NP-completeness”, W.H. Freeman and Company, San Francisco.

C.P. Ravikumar, A. Verma, G. Chandra, “A Polynomial-Time Algorithm for Power Constrained Testing of Core Based Systems”, ATS 99, pp 107–112.

V. Muresan, X. Wang, M. Vladutiu, “List scheduling and Tree Growing Technique in Power-Constrained Block-Test Scheduling”, ETW 99, pp 27–32.

V. Muresan, X. Wang, M. Vladutiu, “A comparison of classical Scheduling Approaches in Power-Constrained Block-Test Scheduling ”, ITC 2000, pp 882–891.

V.Yengar, K. Chakrabarty, “Precedence-Based, Preemptive and Power-Constrained Test Scheduling for System-on-a-Chip”, Proc. VTS ‘01, pp:368–374.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2002 IFIP International Federation for Information Processing

About this chapter

Cite this chapter

Flottes, ML., Pouget, J., Rouzeyre, B. (2002). Power-constrained Test Scheduling for SoCs under a “no session” scheme. In: Robert, M., Rouzeyre, B., Piguet, C., Flottes, ML. (eds) SOC Design Methodologies. IFIP — The International Federation for Information Processing, vol 90. Springer, Boston, MA. https://doi.org/10.1007/978-0-387-35597-9_34

Download citation

DOI: https://doi.org/10.1007/978-0-387-35597-9_34

Publisher Name: Springer, Boston, MA

Print ISBN: 978-1-4757-6530-4

Online ISBN: 978-0-387-35597-9

eBook Packages: Springer Book Archive