Abstract

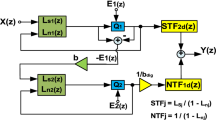

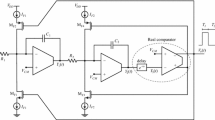

An operational amplifier designed with 0.35um CMOS technology is presented. All the transistors are realized with minimum or near-minimum channel length. As the short channel length causes performance degradation, a proper operational amplifier structure is selected to compensate the performance degradation. The op amp is designed to meet the requirement of high-speed high-resolution sigma delta modulators. It has a folded-cascode first stage and a class-A output stage. It features a DC gain of 78dB, an open-loop unity-gain frequency of 266MHZ, a slew rate of 650V/us, and consumes 10.2mW from a +/−1.5V power supply. High level simulation is used to evaluate the OTA performance in sigma delta modulators.

The original version of this chapter was revised: The copyright line was incorrect. This has been corrected. The Erratum to this chapter is available at DOI: 10.1007/978-0-387-35498-9_57

Chapter PDF

Similar content being viewed by others

References

A. M. Marques, V. Peluso, M. S. J. Steyaert and W. Sansen, “A 15-b Resolution 2-MHz Nyquist Rate DS ADC in a 1-um CMOS Technology”, IEEE J. Solid-State Circuits, vol. 33, Jul. 1998, pp. 1065–75

A. R. Feldman, B. E. Boser and P. Gray, “A 13-bit, 1.4-MS/s Sigma-Delta Modulator for RF Baseband Channel Applications”, IEEE J. Solid-State Circuits, vol. 33, Oct. 1998, pp. 1462–69

http://www.ams.co.at/corporate/profile.html

S. Ingalsuo, T. Ritoniemi & H. Tenhunen, “New Differential Amplifier for High Speed Switched Capacitor Circuits”, in proc. of European Conference on Circuit Theory and Design (ECCTD-91), Copenhagen, Denmark, September 1991.

A. M. Abo and P. Gray, “A 1.5-V, 10-bit, 14.3-MS/s CMOS Pipeline Analog-to-Digital Converter”, IEEE J. Solid-State Circuits, vol. 34, May. 1999, pp. 599–606

S. R. Northworthy, R. Schreier and G. C. Ternes, Delta -Sigma Data Converters, Theory, Design, and Simulation, IEEE press, 1997

B. E. Boser and B. A. Wooley, “The Design of Sigma-Delta Modulation Analog-toDigital Converters”, IEEE J Solid-State Circuits, vol. SC-23 Dec. 1988, pp. 1298–1308

B. K. Ahuja, “An improved Frequency Compensation Technique for CMOS Operational Amplifier”, IEEE J. Solid-State Circuits, vol. SC-18, Dec. 1983, pp. 629–633

D. B. Ribner and M. A. Copeland, “Design Techniques for Cascoded CMOS Op Amps with Improved PSRR and Common-Mode Input Range”, IEEE J. Solid-State Circuits, vol. sc-19, Dec. 1984, pp. 919–625

K. Nakamura, M. Hotta, L. R. Carley and D. J. Allstot, “An 85 mW, 10b, 40 Msample/s CMOS Parallel-Pipelined ADC”, IEEE J. Solid-State Circuits, vol. 30, Mar. 1995, pp. 173–183

S. Rabii and B. A. Wooley, The Design cf Low-Voltage, Low-Power Sigma-Delta Modulators, Kluwer Academic Publishers, 1999

B.X. Li and H. Tenhunen, “Hierarchical Modeling of Sigma Delta Modulators for Noise Coupling Analysis”, in proc. of 1999 Southwest Symposium on Mixed-Signal Design, Apr., 1999, pp. 58–62

S. Brigati, F. Francesconi, P. Malcovati, D. Tonietto, A. Baschirotto and F. Maloberti, “Modeling Sigma-Delta Modulator Non-idealities in Simulink”, in proc. of IEEE International Symposium on Circuits and Systems, May, 1999, pp. I I 384–387

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2000 IFIP International Federation for Information Processing

About this chapter

Cite this chapter

Li, B., Tenhunen, H. (2000). A Design of Operational Amplifiers for Sigma Delta Modulators using 0.35um CMOS Process. In: Silveira, L.M., Devadas, S., Reis, R. (eds) VLSI: Systems on a Chip. IFIP — The International Federation for Information Processing, vol 34. Springer, Boston, MA. https://doi.org/10.1007/978-0-387-35498-9_3

Download citation

DOI: https://doi.org/10.1007/978-0-387-35498-9_3

Publisher Name: Springer, Boston, MA

Print ISBN: 978-1-4757-1014-4

Online ISBN: 978-0-387-35498-9

eBook Packages: Springer Book Archive