Abstract

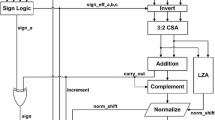

In this paper1. we present a new architecture for low power floating point multiply — accumulate (MAC) fusion. The proposed architecture supports IEEE and non IEEE rounding modes. The functional partitioning of the adder segment of the MAC into three distinct, clock gated data paths allows activity reduction. The switching activity function of the adder is represented as a three state FSM. During any given operation cycle, only one of the data paths is active, during which occasion, the logic assertion status of the circuit nodes of the other data paths are maintained at their previous states. Critical path delay and latency are reduced by incorporating speculative rounding and data path simplifications. The proposed scheme offers a worst case power reduction of around 25%, in contrast to a comparable scheme reported in literature.

The original version of this chapter was revised: The copyright line was incorrect. This has been corrected. The Erratum to this chapter is available at DOI: 10.1007/978-0-387-35498-9_57

Chapter PDF

Similar content being viewed by others

Key words

References

Erdem Hokenek, Robert K. Montoye and Peter W. Cook, “Second generation RISC floating point with multiply–add fused”. IEEE Journal of Solid Stare Circuits, Vol. 15, pp. 1207–1213, October 1990.

IEEE Standard for Binary Floating - Point Arithmetic“, ANSI/IEEE Std 754–1985, New York, The Institute of Electrical and Electronics Engineers Inc.,August 12, 1985.

Israel Koren, “Computer Arithmetic Algorithms”, Prentice Hall, Englewood Cliffs, 1993.

W. Kahan, “Lecture Notes on the Status of IEEE Standard 754 for Binary F loatingPoint Arithmetic”, (http://http.cs.berkcley.eduhwkahan/ieee754statusiiee754.ps) Elect. Eng. and Computer Science, University of California, Berkeley.

Kurt Keutzer and Peter Vanbekbergen, “The Impact of CAD on the Design of Low Power Digital Circuits,” in Proceedings of the 1994 IEEE Symposium on Low Power Electronics,pp. 42–45.

Anantha P. Chandrakasan, Randy Allmon, Anthony Stratakos, and Robert W. Brodersen, “Design of Portable Systems,” in Proceedings of the 1994 IEEE Custom Integrated Circuits Conference,pp. 259–266.

R. V. K. Pillai, D. Al - Khalili and A. J. Al - Khalili, “A Low Power Approach to Floating Point Adder Design”. in Proceedings of the 1997 International Con/èrence on Computer Design,pp. 178–186.

R. V. K. Pillai, “On Low Power Floating Point DSP Data Path Architectures”, Ph. D Thesis (under preparation) - Department of Electrical and Computer Engineering, Concordia University, Montreal, Quebec.

R. W. Hamming, “On the Distribution of Numbers”, Bell System Technical Journal, Vol. 49, No. 8, pp. 1609–1625, October 1970.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2000 IFIP International Federation for Information Processing

About this chapter

Cite this chapter

Pillai, R.V.K., Al-Khalili, D., Al-Khalili, A.J. (2000). An IEEE Compliant Floating Point MAF. In: Silveira, L.M., Devadas, S., Reis, R. (eds) VLSI: Systems on a Chip. IFIP — The International Federation for Information Processing, vol 34. Springer, Boston, MA. https://doi.org/10.1007/978-0-387-35498-9_14

Download citation

DOI: https://doi.org/10.1007/978-0-387-35498-9_14

Publisher Name: Springer, Boston, MA

Print ISBN: 978-1-4757-1014-4

Online ISBN: 978-0-387-35498-9

eBook Packages: Springer Book Archive