Abstract

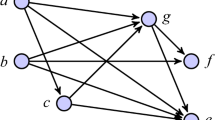

This paper shows several new perspectives of partitioning circuits into clusters for the implementation into programmable devices. The partitioning algorithm is based on a probabilistic node movement and is able to consider different optimization goals. Special clustering strategies based on the max flow theorem before the partitioning allow the handling of large circuits, a retiming approach following the partitioning improves the overall system performance. Several large benchmark circuits could be implemented into FPGAs with low computational costs.

This research is supported by the Esprit LINK project 6855

Chapter PDF

Similar content being viewed by others

References

Brglez, F., Brayan, F. and Krzysztof, D. (1989) Combinational Profiles of Sequential Benchmark Circuits. Technical Report TR89, Microelectronics Center of North Carolina.

Ford, L.R. and Fulkerson, D.R. (1962) Flows in Networks. Princton University Press.

Kernighan, K.H. and Lin, S. (1970). An Efficient Heuristic Procedure for Partitioning Graphs. Bell System Technical Journal, vol. 49, no. 2.

Kuznar, R., Brglez, E and Kozminski, K. (1993) Cost Minimization of Partitions into Multiple Devices. Proceedings of DAC 93, 315–20.

Leiserson, C. E., Rose, F. M. and Saxe, J. B. (1993) Optimizing synchronous circuitry by retiming. Proc. Third Caltech Conf. on VLSI.

Murgai, R., Brayton, R. and Sangiovanni-Vincentelli, A. (1991) On Clustering for Minimum Delay/Area. Proceedings of DAC 91, 6–10.

Weinmann, U. (1993) FPGA Partitioning under Timing Constraints. Int. Workshop on Field Programmable Logic and Applications, Oxford.

Weinmann, U. and Rosenstiel, W. (1993) Technology Mapping for Sequential Circuits based on Retiming Techniques. Proceedings of the EURO-DAC 93, 318–23.

Weinmann, U. and Rosenstiel, W. (1994), Module Independent Mapping into TLU-FPGAs. 2nd ACM/SIGDA FPGA Workshop, Berkeley.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 1995 IFIP International Federation for Information Processing

About this chapter

Cite this chapter

Weinmann, U., Rosenstiel, W. (1995). Circuit clustering and partitioning for system implementations. In: Saucier, G., Mignotte, A. (eds) Logic and Architecture Synthesis. IFIP Advances in Information and Communication Technology. Springer, Boston, MA. https://doi.org/10.1007/978-0-387-34920-6_8

Download citation

DOI: https://doi.org/10.1007/978-0-387-34920-6_8

Publisher Name: Springer, Boston, MA

Print ISBN: 978-1-5041-2923-7

Online ISBN: 978-0-387-34920-6

eBook Packages: Springer Book Archive