Abstract

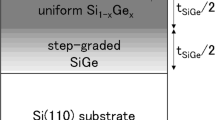

Junctions were formed in thin SiGe/strained Si substrates with a thickness of 250-350 nm to assess the effect of different buffer layer parameters (bandgap, dislocations, thickness) on the junction leakage density that can be expected in MOSFET devices. The implantations used are standard well, channel and Highly Doped Drain (HDD) implants. Both p+/n and n+/p junctions were evaluated. The total thickness of the buffer layers was varied to compare the effect of different structural layers on the diode leakage. This investigation shows that the effect of an increased defect density is dominant at room temperature for the strained Si samples, resulting in 4-5 orders of magnitude increase in leakage. However, there is a different gradation in leakage dependence for thick and thin buffer layers, especially at higher temperatures.

Similar content being viewed by others

References

K. Rim et al., 2001 Symposium on VLSI technology, p. 59

J. Hoyt et al., IEDM Techn. Dig. p. 23 (2002)

H.C.-H. Wang et al., IEDM Techn. Dig. p. 61 (2003)

J.-S. Goo et al., IEEE Electr. Dev. Lett. 24, p. 351 (2003)

L. M. Giovane et al., Appl. Phys. Lett. 78, p. 541 (2001)

R. Delhougne et al., Proc. of the ISTDM 2003, Applied Surface Science 224, p. 91 (2004)

R. Delhougne et al, accepted for publication in Solid State Electronics-Special Issue Strained-Si Heterostructures and Devices

R. Loo et al., to be presented at MRS 2004 Spring Meeting

J. Weber, M.I. Alonso, Phys. Rev. B 40, p. 5683, (1989)

Acknowledgments

The authors would like to thank Alessandro Benedetti for providing the TEM picture of the SiGe/strained Si layers.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Eneman, G., Simoen, E., Lauwers, A. et al. Analysis of junctions formed in strained Si/SiGe substrates. MRS Online Proceedings Library 809, 64 (2003). https://doi.org/10.1557/PROC-809-B6.4

Published:

DOI: https://doi.org/10.1557/PROC-809-B6.4