Abstract

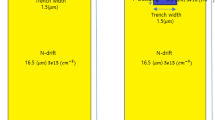

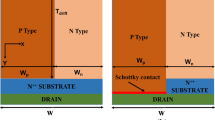

The long-term reliability of gate insulator under high field stress of either polarity presents a constraint on the highest electric field that can be tolerated in a 4H-SiC UMOSFET under on or off condition. A realistic performance projection of 4H-SiC UMOSFET structures based on electric field in the gate insulator (1.5 MV/cm under on-condition and 3 MV/cm under off-condition) consistent with long-term reliability of insulator is provided for the breakdown voltage in the range of 600 to 1500 V. The use of P+ polysilicon gate allows us to use a higher field of 3 MV/cm in the insulator under off-condition and leads to a higher breakdown voltage as the Fowler Nordheim (FN) injection from the gate electrode is reduced. FN injection data is presented for p type 4H-SiC MOS capacitor under inversion at room temperature and at 325°C. It is concluded that the insulator reliability, and not the SiC, is the limiting factor and therefore the high temperature operation of these devices may not be practical.

Similar content being viewed by others

References

M. Bhatnagar and B. J. Baliga, “Comparison of 6H-S1C, 3C-SiC and Si power devices,” IEEE Trans, on Electron Devices, 40, pp. 645–655, 1993.

J. W. Palmour and L. A. Lipkin, “High temperature power devices in silicon carbide,” Trans. Second International High Temperature Electronics Conference, p. XI–3, June 1994.

N. Tokura, K. Hara, T. Miyajima, H. Fuma and K. Hara, “Current-Voltage and capacitance-voltage characteristics of metal/oxide/6H-silicon carbide structure,” Jpn. J. Appl. Phys., 34, pp. 5567–5573, 1995.

V. V. Afanas ev, M. Bassler, G. Pensl, E. Stein von Kamienski and M. J. Schulz, “Band offsets and electronic structure of SiC/SiO2 interfaces,” unpublished.

Dr. Alvin M. Goodman, private communication.

Prof. T. Paul Chow, private communication.

Afanasev, M. Bassler, G. Pensl and M. J. Schulz, “Energy distribution of electron states at SiC/SiO2 interfaces,” IEEE Semiconductor Interface Specialist Conference, Dec. 1995.

L. A. Lipkin and J. W. Palmour, “Improved oxidation procedures for reduced SiO2/SiC defects,” IEEE Semiconductor Interface Specialist Conference, Dec. 1995.

Acknowledgments

This work was supported in part by US Air Force (WPAFB, Dayton Ohio) and Office of Naval Research, Arlington, Virginia. Authors wish to thank Mr. Clarence Severt of Wright Laboratory and Dr. Alvin M. Goodman of ONR for helpful technical discussions. The entire AESL staff at Northrop Grumman STC is acknowledged for their contributions to this work.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Agarwal, A.K., Siergiej, R.R., Seshadri, S. et al. Critical Materials, Device Design, Performance and Reliability Issues in 4H-SiC Power Umosfet Structures. MRS Online Proceedings Library 423, 87–92 (1996). https://doi.org/10.1557/PROC-423-87

Published:

Issue Date:

DOI: https://doi.org/10.1557/PROC-423-87