Abstract

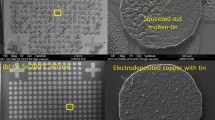

Cu interconnects have decreased in width and are at around 100 nm. A decrease in interconnect width have led to a predominately bamboo structured Cu lines. In Cu interconnects, void formation during high temperature is a reliability issue, and this study looks at the void formation behavior in damascene Cu interconnects with a predominately bamboo microstructure. First, the crystal texture and grain morphology of the Cu interconnects was observed. Then to determine the void formation behavior, in-situ Transmission Electron Microscopy (TEM) was performed. Voids that formed as a result of in-situ heating were analyzed in terms of preferential void formation sites and crystal orientation where voids formed. In bamboo structured lines, voids formed at the triple junction of grain boundary and Cu/diffusion barrier interface. The crystal orientation where voids nucleated was studied to identify diffusion paths during void nucleation and growth.

Similar content being viewed by others

References

The National Technology Roadmap for Semiconductors, Semiconductor Industry Association, 2003

Dongwen Gan, Guotao Wang, Paul S. Ho, “Effects of Dielectric Material and Linewidth on Thermal Stresses of Cu line Structures”, IITC 2002 p271–273

J.H. An, P.J. Ferreira, “In Situ TEM Studies of Nanoscale Cu Interconnects Under Thermal Stress”, in Stability of Thin Films and Nanostructures, edited by R.P. Vinci, R. Schwaiger, A. Karim, and V. Shenoy (Mater. Res. Soc. Symp. Proc. 854E, Warrendale, PA, 2005), U11.13

M.A. Korhonen, P. Borgesen, Che-Yu Li, “Mechanisms of Stress-Induced and Electromigration-Induced Damage in Passivated Narrow Metallizations on Rigid Substrates”, MRS Bulleting July (1992) p61–68

J. A. Nucci, R.R. Keller, D.P. Field, Y. Shacham-Diamand, “Grain Boundary Misorientation Angles and Stress-Induced Voiding in Oxide Passivated Copper Interconnects”, Appl. Phys. Lett. V70 (1997) p1242–1244

R.R. Keller, J.A. Nucci, D.P. Field, “Local Texture and Grain Boundaries in Voided Copper Interconnecdts”, J. of Electronic Materials, V26 (1997) p996–1001

H. Okabayashi, “Stress-Induced Void Formation in Metallization for Integrated Circuits”, Materials Science and Engineering R11 (1993) p191–241

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

An, J.H., Ferreira, P.J. In-situ TEM Study of Thermally Induced Voids in 180 nm Cu Interconnects. MRS Online Proceedings Library 907, 303 (2005). https://doi.org/10.1557/PROC-0907-MM03-03

Received:

Accepted:

Published:

DOI: https://doi.org/10.1557/PROC-0907-MM03-03