Abstract

We report a novel nanocrystal-embedded-insulator (NEI) ferroelectric field-effect transistor (FeFET) with very thin unified-ferroelectric/dielectric (FE/DE) insulating layer, which is promising for low-voltage logic and non-volatile memory (NVM) applications. The ferroelectric nature of the NEI layers comprising orthorhombic ZrO2 nanocrystals embedded in amorphous Al2O3 is proved by polarization voltage measurements, piezoresponse force microscopy, and electrical measurements. The temperature dependent performance and endurance behavior of a NEI negative capacitance FET (NCFET) are investigated. A FeFET with 3.6 nm thick FE/DE achieves a memory window larger than 1 V, paving a pathway for ultimate scaling of FE thickness to enable three-dimensional FeFETs with very small fin pitch.

Background

Field-effect transistors with a ferroelectric gate insulator layer (FeFETs) have attracted considerable interest for a variety of integrated circuit applications. Due to its inherent negative capacitance (NC) properties, a FeFET can achieve steeper switching behavior than a conventional MOSFET, enabling lower voltage operation [1]. Various channel structures [2,3,4] and materials [5,6,7] have obtained sub-60 mV/decade subthreshold swing (SS). Also, hysteresis in the current-voltage (I-V) characteristic due to remnant polarization (Pr) can be used for non-volatile memory (NVM) application [8]. Material development for FeFETs recently has focused on polycrystalline-doped HfO2 due to its better thickness scalability [9] and CMOS process compatibility [2]. However, there still exists a fundamental limit for HfO2 thickness scaling to avoid undesired gate leakage current; this in turn limits the FinFET [2]. Inspired by the nanocrystal MOS and memory device concept [10, 11], an insulating dielectric (DE) layer with embedded ferroelectric (FE) nanocrystals is introduced in this work. The resulting new device design illustrated in Fig. 1 is called the “Nanocrystal-Embedded-Insulator” (NEI) FeFET. The main advantage of this design is a thinner unified-FE/DE layer that meets the low-gate-leakage requirement.

In this work, NEI FeFETs are reported. Physical properties and ferroelectricity of the NEI layers with different physical thicknesses are characterized. Electrical performance of NEI FeFETs is investigated for low-voltage logic and NVM applications.

Methods

Key process steps for NEI FeFETs fabrication are shown in Fig. 1a. Four-inch n-type Ge(001) wafers with a resistivity of 0.088–0.14 Ω cm were used as the starting substrates. After pregate cleaning using diluted HF, Ge(001) wafers were loaded into an atomic layer deposition (ALD) chamber for the deposition of the NEI layer comprising ZrO2 nanocrystals embedded in amorphous Al2O3 matrix. NEI layers with the various thicknesses were utilized in this work. TaN metal gate was deposited on the NEI FeFETs using the reactive sputtering. After the gate patterning and etching, BF2+ ions were implanted into the source/drain regions at an energy of 20 keV and a dose of 1 × 15 cm−2. Thirty-nanometer nickel (Ni) was deposited in source/drain regions using the lift-off process. Finally, device fabrication was completed with rapid thermal annealing (RTA). Control metal-oxide-semiconductor field-effect transistors (MOSFETs) with a purely dielectric Al2O3 gate insulating layer also were fabricated.

Figure 1b shows the 3D schematic of the fabricated NEI FeFET, which comprises FE nanocrystals embedded in an amorphous DE gate insulating layer. Although the volume of FE material is small, it is sufficient for NCFET and NVM applications. The insulating DE material is key to achieving low gate leakage and low operating voltage; it should have both a large bandgap energy and high dielectric permittivity (κ). It also should provide for a high coercive field (Ec) of the embedded FE nanocrystals.

The cross-sectional transmission electron microscope (XTEM) image in Fig. 2a shows the source/drain, channel, and gate edge regions of a fabricated FeFET. Figures 2b and c indicate the thicknesses of the NEI layers studied in this work to be 3.6 and 2.1 nm, respectively. Note that an interfacial layer of GeOx exists between the NEI layer and Ge, although it cannot be seen.

High-resolution TEM (HRTEM) images in Fig. 3 demonstrate the ZrO2 nanocrystals embedded in amorphous Al2O3 on Ge(001) in the NEI samples with thicknesses of 3.6 and 6 nm. In our previous work, we have shown that the atomic percentage of Zr in the NEI layer is less than 0.5% [12]. Based on the diffraction patterns, the interplanar spacing d within the nanocrystals is calculated to be 0.173 nm, which corresponds to (111)-oriented orthorhombic ZrO2 phase [13].

Polarization vs. voltage (P-V) and piezoresponse force microscopy (PFM) measurements were carried out on the NEI samples with the different thicknesses. To characterize the ferroelectricity of the NEI layer, P-V curves of TaN/NEI (3.6 nm)/Ge, TaN/NEI (6 nm)/Si0.7Ge0.3, and TaN/NEI (10 nm)/TaN capacitors are shown in Fig. 4a, b, and c, respectively. The NEI layer exhibits a lower P than the reported values of HfZrO2 (HZO) [14], which is due to the fact that the volume ratio of ZrO2 nanocrystal in Al2O3 matrix is quite low. It is seen that the remnant polarization Pr of the NEI film increases with the increasing of film thickness. P-V curves in Fig. 4c indicate that the ferroelectricity of the NEI layer degenerates while the annealing temperature increases from 450 to 550 °C. It is noted that the reason for the unclosed P-V loops is because a leakage indeed exists. It was reported that the resultant offset at zero electric field diminishes as the voltage sweeping range is reduced [3, 15, 16]. The amplitude (upper) and phase (lower) images of 3.6 nm, 6 nm, and 10 nm NEI were measured, as shown in Fig. 5a, b, and c, respectively. As shown in Fig. 6, patterns indicating the opposite polarity written onto the surface of NEI on TaN exhibit the clearer contrast with the increasing of film thickness.

Results and Discussion

NEI NCFET

Figure 7a shows measured IDS-VGS curves of the NEI NCFETs with a NEI thickness of 3.6 nm annealed at 450 °C and 500 °C. The NCFETs exhibit little hysteresis indicating the good matching between the ferroelectric capacitance and the MOS capacitance in the transistors. The NCFETs show the NC effect induced clockwise I-V loops, which is in contrast to the counterclockwise ones by charge trapping/detrapping [17]. The gate leakage IG as a function of VGS of the same pair of devices demonstrates that the formation of nanocrystals in Al2O3 does not increase the gate leakage. Figure 7b shows that the NCFETs achieve the sub-60 mV/decade steep SS points for the forward and reverse sweepings. The SS fluctuations in the NEI NCFET, also observed in NC FinFETs [2, 18], might be due to the polarization switching by the different ferroelectric nanocrystals or domains. The measured IDS-VDS curves for the same pair of devices in Fig. 7c show that at ∣VGS − VTH ∣ = ∣ VDS ∣ = 1.0 V, the NCFET with RTA at 500 °C achieves 29% larger IDS in comparison with the transistor annealed at 450 °C. This is attributed to the fact that the carrier mobility in channel and contact resistance characteristics can be improved with the increasing of annealing temperature [19]. The typical characteristic induced by the ferroelectric layer, negative differential resistance (NDR), is observed in the IDS-VDS curves for the NCFETs annealed at the different temperatures.

a Measured IDS-VGS and IG-VGS curves of NCFETs with 3.6-nm NEI annealed at 450 °C and 500 °C. b NEI NCFETs has the sub-60 mV/decade points for a VDS value of − 0.05 V. c IDS-VDS curves for the NEI NCFETs showing the obvious NDR phenomena. NC transistor annealed at 500 °C achieves a 29% IDS improvement compared to the device with RTA at 450 °C at a supply voltage of 1.0 V

Figure 8a shows measured IDS-VGS curves of a NEI NCFET and a control MOSFET with the same insulator thickness of 2.1 nm. Devices have a LG of 6 μm. The NCFET exhibits the hysteresis-free characteristics. The inset shows the point SS vs. IDS curves for the devices, demonstrating that improved SS is achieved in the NCFET compared to the control device, up to the threshold voltage. Figure 8b shows the IDS-VDS curves of the NEI NCFET and the control MOSFET. NCFET exhibits the NDR phenomenon for the low VGS. The NDR effect corresponds to the improved drain-induced barrier lowering (DIBL) characteristics in NCFET compared to the control MOSFET, as shown in Fig. 8a. At ∣VGS − VTH ∣ = ∣ VDS ∣ = 1.0 V, a 16% IDS enhancement is obtained in NCFET in comparison with the control device. NCFET with 2.1 nm NEI has the less significant NDR compared to the transistor with 3.6 nm NEI, which is consistent with the conclusion in [20].

a IDS-VGS curves of an NEI NCFET and control MOSFET with pure Al2O3 dielectric. Both devices have the 2.1-nm gate insulator. The inset shows that the NCFET has steeper SS than control device up to the threshold voltage. b Measured IDS-VDS curves for NCFET and control MOSFET. NDR is observed for NCFET at very low VGS. At ∣VGS − VTH ∣ = ∣ VDS ∣ = 1.0 V, NCFET achieves a 16% IDS improvement compared to the control device

The temperature dependence of the NCFET with 3.6-nm-thick NEI is investigated herein. Figure 9a shows IDS-VGS curves measured at 10 °C and 30 °C. Inset indicates that the SS performance of the transistor does not degrade at the elevated temperatures. As the temperature increases, the I-V curve shifts to more negative VGS due to the dominant effect of ferroelectricity, which is opposite to the trend for a conventional MOSFET. Figure 9b summarizes the shifts in hysteresis voltage and forward switching threshold voltage with temperature. Forward VGS shifts to more negative values as temperature increases, which might be due to increased Ec of the NEI.

a IDS-VGS of a NEI (3.6 nm) NCFET measured at 10 °C and 30 °C. The curves show a shift towards more negative voltage with increasing temperature, as expected. Inset shows steep point SS. b Statistical plots of hysteresis (left) and forward VGS @ 10−7 A/μm (right) for NCFETs with 3.6-nm NEI layer. Forward VGS shifts in the negative direction with increasing temperature

NEI FeFET for Non-Volatile Memory Application

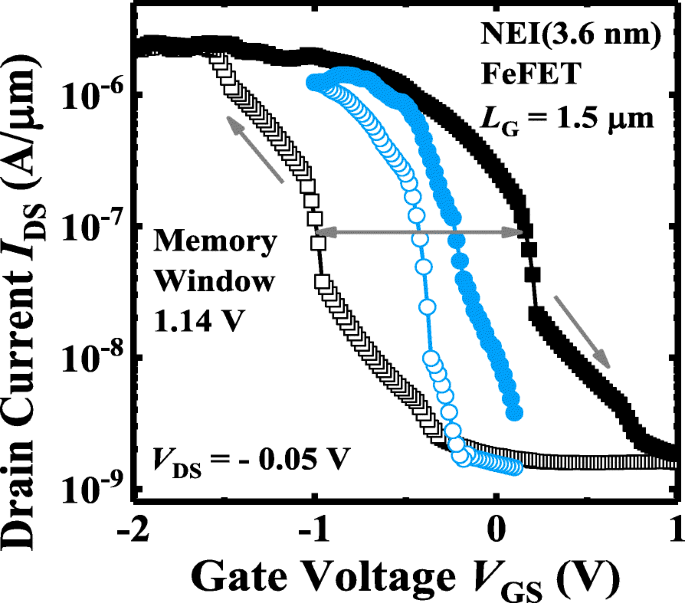

By increasing the range of VGS sweeping, the hysteresis voltage of a NEI FeFET can be increased to achieve a large and stable memory window (MW) for read and write operations. As shown in Fig. 10, a FeFET with 3.6-nm NEI demonstrates that the MW increases from 0.2 to 1.14 V as VGS sweeping range varies from (0.1 V, − 0.1 V) to (1 V, − 2 V). DC sweep endurance of another FeFET memory device is shown in Fig. 11a, Fig. 11b illustrates the hysteresis characteristics as a function of number of DC sweeping cycles. Stable I-V hysteresis window of ~ 0.65 V is seen.

Figure 12 benchmarks the NEI FeFET memory device against reported FeFETs, with regard to MW and FE layer thickness [8, 21–24]. It should be noted that the NEI FeFET device in this work achieves a sizable (> 1 V) MW with the thinnest reported FE thickness of 3.6 nm. We speculate that it is easier to achieve the stable FE phase in NEI with a smaller thickness, as compared to the doped HfO2 [28,29,30].

Finally, the advantages of the NEI FeFET provided by ZrO2 nanocrystals embedded in amorphous gate insulator are discussed. Figure 13 benchmarks the NEI layer against reported doped HfO2 films [2, 3, 21, 25–27], with regard to Ec and Pr. NEI can achieve a much lower Pr compared to doped HfO2 for similar Ec. Our experiments have demonstrated that a Pr below 1 μC/cm2 can provide the required MW in the FeFETs. Excessive polarization could lead to greater depolarization, resulting in worse retention characteristics, which was reported in [25]. Furthermore, the FE and DE properties of the NEI layer can be adjusted separately: Pr is enhanced/reduced by increasing/decreasing the volume of FE nanocrystals, and κ is increased by incorporating other elements in the amorphous matrix (e.g., LaAlO3), to optimize FeFET performance.

Conclusions

Novel FeFETs with ZrO2 nanocrystals embedded in an amorphous Al2O3 gate insulating layer are reported. Physical analyses indicate that less than 0.5% Zr in Al2O3 produces sufficient ferroelectricity for NCFET and NVM applications. Stable NC effect is observed at different measurement temperatures. Stable FeFET memory operation with record thin (3.6-nm total thickness) gate insulator is demonstrated. Stable MW is achieved over 1000 DC endurance cycles. The proposed NEI FeFET design provides a pathway for scaling down the thickness of the FE/DE gate insulator layer to be compatible with FinFETs with very small fin pitches.

Abbreviations

- Al2O3 :

-

Aluminum oxide

- ALD:

-

Atomic layer deposition

- BF2 + :

-

Boron fluoride ion

- DC:

-

Direct current

- Ec:

-

Coercive field

- FeFET:

-

Ferroelectric field-effect transistor

- Ge:

-

Germanium

- GeOx :

-

Germanium oxide

- HF:

-

Hydrofluoric acid

- HRTEM:

-

High-resolution transmission electron microscope

- I DS :

-

Drain current

- MOSFETs:

-

Metal-oxide-semiconductor field-effect transistors

- MW:

-

Memory window

- NC:

-

Negative capacitance

- NDR:

-

Negative differential resistance

- NEI:

-

Nanocrystal-embedded-insulator

- Ni:

-

Nickel

- Pr:

-

Remnant polarization

- RTA:

-

Rapid thermal annealing

- SS:

-

Subthreshold swing

- TaN:

-

Tantalum nitride

- V GS :

-

Gate voltage

- V TH :

-

Threshold voltage

- ZrO2 :

-

Zirconium dioxide

References

Salahuddin S, Datta S (2018) Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett 8:405–410

Krivokapic Z, Rana U, Galatage R, Razavieh A, Aziz A, Liu J, Shi J, Kim HJ, Sporer R, Serrao C, Busquet A, Polakowski P, Müller J, Kleemeier W, Jacob A, Brown D, Knorr A, Carter R, Banna S (2017) 14nm ferroelectric FinFET technology with steep subthreshold slope for ultra low power applications. In: IEDM Tech. Dig, pp 357–360

Chung W, Si M, Ye PD (2017) Hysteresis-free negative capacitance germanium CMOS FinFETs with Bi-directional Sub-60 mV/dec. In: IEDM Tech. Dig, pp 365–368

Si M, Jiang C, Su C-J, Tang Y-T, Yang L, Chung W, Alam MA, Ye PD (2017) Sub-60mV/dec ferroelctric HZO MoS2 negative capacitance field-effect transistor with metal gate: the role of parasitic capacitance. In: IEDM Tech. Dig, pp 369–372

Su C-J, Tang Y-T, Tsou Y-C, Sung P-J, Hou F-J, Wang C-J, Chung S-T, Hsieh C-Y, Yeh Y-S, Hsueh F-K, Kao K-H, Chuang S-S, Wu C-T, You T-Y, Jian Y-L, Chou T-H, Shen Y-L, Chen B-Y, Luo G-L, Hong T-C, Huang K-P, Chen M-C, Lee Y-J, Chao T-S, Tseng T-Y, Wu W-F, Huang G-W, Shieh J-M, Yeh W-K, Wang Y-H (2017) Nano-scaled Ge FinFETs with low temperature ferroelectric HfZrOx on specific interfacial layers exhibiting 65% S.S. reduction and improved I ON. In: VLSI Tech. Symp, p TI2-1

Zhou J, Han G, Li Q, Peng Y, Lu X, Zhang C, Zhang J, Sun Q, Zhang DW, Hao Y (2016) Ferroelectric HfZrOx Ge and GeSn PMOSFETs with sub-60 mV/decade subthreshold swing, negligible hysteresis, and improved I DS. In: IEDM Tech. Dig, pp 310–313

Luc QH, Fan-Chiang CC, Huynh SH, Huang P, Do HB, Ha MTH, Jin YD, Nguyen TA, Zhang KY, Wang HC, Lin YK, Lin YC, Hu C, Iwai H, Chang EY (2018) First experimental demonstration of negative capacitance InGaAs MOSFETs with Hf0.5Zr0.5O2 ferroelectric gate stack. In: VLSI Symp, pp 47–48

Müller J, Yurchuk E, Schlösser T, Paul J, Hoffmann R, Müller S, Martin D, Slesazeck S, Polakowski P, Sundqvist J, Czernohorsky M, Seidel K, Kücher P, Boschke R, Trentzsch M, Gebauer K, Schröder U, Mikolajick T (2012) Ferroelectricity in HfO2 enables nonvolatile data storage in 28 nm HKMG. In: VLSI Symp, pp 25–26

Xiao W, Liu C, Peng Y, Zheng S, Feng Q, Zhang C, Zhang J, Hao Y, Liao M, Zhou Y (2019) Performance Improvement of Hf0.5Zr0.5O2 Based Ferroelectric-Field-Effect Transistors with ZrO2 seed layers. IEEE Electron Device Lett xx.

King Y-C, King T-J, Hu C (1998) MOS memory using germanium nanocrystals formed by thermal oxidation of Si1-xGex. In: IEDM Tech. Dig, pp 115–118

Blauwe JD (2002) Nanocrystal nonvolatile memory devices. IEEE Tran Nanotech 1:72–77

Peng Y, Xiao W, Han G, Wu J, Liu H, Liu Y, Xu N, King Liu T-J, Hao Y (2019) Nanocrystal-embedded-insulator ferroelectric negative capacitance FETs with sub-kT/q swing. IEEE Electron Device Lett 40:9–12

Ohtaka O, Yamanaka T, Kume S, Hara N, Asano H, Izumi F (2013) Phase transformation of baddeleyite (ZrO2) to an orthorhombic phase: structural analysis of ortho-ZrO2 by neutron diffraction. US Jap Sem 67:463–468

Müller J, Böscke TS, Schröder U, Mueller S, Bräuhaus D, Böttger U, Frey L, Mikolajick T (2012) Ferroelectricity in simple binary ZrO2 and HfO2. Nano Lett. 12:4318–4323

Zhou J, Han G, Li J, Liu Y, Peng Y, Zhang J, Sun Q-Q, Zhang DW, Hao Y (2018) Effects of the variation of V GS sweep range on the performance of negative capacitance FETs. IEEE Elect Dev Lett 39:618–621

Smith SW, Kitahara AR, Rodriguez MA, Henry MD, Brumbach MT, Ihlefeld JF (2017) Pyroelectric response in crystalline hafnium zirconium oxide (Hf1-xZrxO2) thin films. Appl Phys Lett 110:072901

Yurchuk E, Müller J, Müller S, Paul J, Pešić M, Bentum RV, Schroeder U, Mikolajick T (2016) Charge-trapping phenomena in HfO2-based FeFET-type nonvolatile memories. IEEE Trans Electron Devices 63:3501–3507

Narasimha S, Jagannathan B, Ogino A, Jaeger D, Greene B, Sheraw C, Zhao K, Haran B, Kwon U, Mahalingam AKM, Kannan B, Morganfeld B, Dechene J, Radens C, Tessier A, Hassan A, Narisetty H, Ahsan I, Aminpur M, An C, Aquilino M, Arya A, Augur R, Baliga N, Bhelkar R, Biery G, Blauberg A, Borjemscaia N, Bryant A, Cao L (2017) A 7nm CMOS technology platform for mobile and high performance compute application. In: IEDM Tech Dig, pp 29.5.1–29.5.4

Zhang Q, Wu N, Osipowicz T, Bera LK, Zhu C (2005) Formation and thermal stability of nickel germanide on germanium substrate. Jap J Appl Phys 44:L1389–L1391

Zhou J, Han G, Li J, Liu Y, Peng Y, Zhang J, Sun Q-Q, Zhang D-W, Hao Y (2018) Negative differential resistance in negative capacitance FETs. IEEE Electron Device Lett 39:622–625

Müller J, Böscke TS, Müller S, Yurchuk E, Polakowski P, Paul J, Martin D, Schenk T, Khullar K, Kersch A, Weinreich W, Riedel S, Seidel K, Kumar A, Arruda TM, Kalinin SV, Schlösser T, Boschke R, van Bentum R, Schröder U, Mikolajick T (2013) Ferroelectric hafnium oxide: A CMOS-compatible and highly scalable approach to future ferroelectric memories. In: IEDM Tech Dig, pp 280–283

Chiu Y-C, Cheng C-H, Chang C-Y, Lee M-H, Hsu H-H, Yen S-S (2015) Low power 1T DRAM/NVM versatile memory featuring steep sub-60-mV/decade operation fast 20-ns speed and robust 85°C-extrapolated 1016 endurance. In: Symp. on VLSI Technology and Circuits, pp T184–T185

Chiu Y-C, Cheng C-H, Chang C-Y, Tang Y-T, Chen M-C (2016) One-transistor ferroelectric versatile memory: strained-gate engineering for realizing energy-efficient switching and fast negative-capacitance operation. In: VLSI Symp, pp 150–151

Chatterjee K, Kim S, Karbasian G, Tan A-J, Yadav A-K, Khan A-I, Hu C, Salahuddin S (2017) Self-aligned gate last FDSOI ferroelectric gate memory device with 5.5-nm Hf0.8Zr0.2O2 high endurance and breakdown recovery. IEEE Electron Device Letters 38:1379–1382

Müller J, Polakowski P, Riedel S, Mueller S, Yurchuk E, Mikolajick T (2013) Performance investigation and optimization of Si:HfO2 FeFETs on a 28 nm bulk technology, ISAF/PFM, pp 248–251

Chen K-Y, Huang Y-H, Kao R-W, Lin Y-X, Wu Y-H (2018) Dependence of reliability of ferroelectric HfZrOx on epitaxial SiGe film with various Ge content. In: VLSI Symp, pp 119–120

Martin D, Yurchuk E, Müller S, Müller J, Paul J, Sundquist J, Slesazeck S, Schloesser T, Bentum RV, Trentzsch M, Schroeder U, Mikojajick T (2012) Downscaling ferroelectric field effect transistors by using ferroelectric Si-doped HfO2. In: ULIS, pp 195–198

Zhou J, Wu J, Han G, Kanyang R, Peng Y, Li J, Wang H, Liu Y, Zhang J, Sun Q, Zhang D, Hao Y (2017) Frequency dependence of performance in Ge negative capacitance PFETs achieving sub-30 mV/decade swing and 110 mV hysteresis at MHz. In: IEDM Tech. Dig, pp 373–376

Lee MH, Fan S-T, Tang C-H, Chen P-G, Chou Y-C, Chen H-H, Kuo J-Y, Xie M-J, Liu S-N, Liao M-H, Jong C-A, Li K-S, Chen M-C, Liu CW (2016) Physical thickness 1.x nm ferroelectric HfZrOx negative capacitance FETs. In: IEDM Tech. Dig, pp 370–373

Zhou H, Kwon D, Sachid AB, Liao Y, Chatterjee K, Tan AJ, Yadav AK, Hu C, Salahuddin S (2018) Negative capacitance, n-channel, Si FinFETs: bi-directional sub-60 mV/dec, negative DIBL, negative differential resistance and improved short channel effect. In: VLSI Symp, pp 53–54

Acknowledgements

Not applicable.

Funding

The authors acknowledge support from the National Natural Science Foundation of China under Grant No. 61534004, 61604112, 61622405, 61874081, and 61851406. This work was also supported by the 111 Project (B12026).

Availability of Data and Materials

The datasets supporting the conclusions of this article are included within the article.

Author information

Authors and Affiliations

Contributions

YP carried out the experiments and drafted the manuscript. GQH, YP, and WWX designed the experiments. JBW helped to measure the device. GQH and YL helped to revise the manuscript. JCZ and YH supported the study. All the authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Authors’ information

State Key Discipline Laboratory of Wide Band Gap Semiconductor Technology, School of Microelectronics, Xidian University, Xi’an 710071, People’s Republic of China.

Competing interests

The authors declare that they have no competing interests.

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

Peng, Y., Han, G., Xiao, W. et al. Nanocrystal-Embedded-Insulator (NEI) Ferroelectric FETs for Negative Capacitance Device and Non-Volatile Memory Applications. Nanoscale Res Lett 14, 115 (2019). https://doi.org/10.1186/s11671-019-2943-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1186/s11671-019-2943-9