Abstract

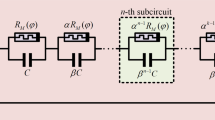

A method of control is proposed on the basis of representing the checked circuits as consequently connected subcircuits (cascades). The subdivision of the circuits into cascades is made in such a way that any failure in each of them results in a distortion of no more than one binary digit at its input. There is developed an universal sequential-sampling circuit with step-by-step control, where the detection of errors does not require additional (coding) variables. The results of this investigation showed that the proposed method for operational control entails considerably lesser hardware and power expenditure as compared with the circuits based on application of the Berger code.

Similar content being viewed by others

References

Lala, P., Self-checking and Fault-Tolerant Digital Design, San Francisco: Morgan Kaufmann, 2000.

Goessel, M. and Graf, S., Error Detection Circuits, London: McGraw-Hill, 1993.

Berger, J.M., A Note on Error Detection Codes for Asymmetric Channels, Inform. Control, 1961, vol. 4, pp. 68–73.

Smith, J.E., On Separable Unordered Codes, IEEE Trans. Comput., 1984, vol. C-33,no. 8, pp. 741–743.

Ostrovskii, V.I., Levin, I.S., and Ostanin, S.A., Synthesis of Self-checking Controllers on the Basis of Modified (M,N)-code, Avtom. Vychisl. Tekhn., 2003, no. 2, pp. 48–55.

Jha, N.K. and Wang, S.J., Design and Synthesis of Self-Checking VLSI Circuits, IEEE Transaction CAD, 1993, vol. 12, no. 6, pp. 878–887.

Kaushik, De., Chitra, N., Devi, N., and Prithviraj, B., A System for Automated Synthesis of Reliable Multilevel Circuits, IEEE Trans. VLSI Syst., 1994, vol. 2, no. 2.

Saposhnikov, V.V., Morosov, A., Saposhnikov, Vl.V., and Gössel, M., A New Design Method for Self-Checking Unidirectional Combinational Circuits, J. Electron. Testing: Theory Appl., 1998, no. 12, pp. 41–53.

Metra, C., Francescantonio, S., and Omana, M., Automatic Modification of Sequential Circuits for Self-Checking Implementation, Proc. 18 IEEE Int. Symp. on Defect and Fault Tolerance in VLSI Syst., 2003, pp. 417–424.

Pomeranz, I. and Reddy, S.M., On-Line Testing of Identical Circuits, Proc. 20 IEEE Int. Sympos. on Defect and Fault Tolerance in VLSI Syst., 2005, pp. 475–483.

Bose, B. and Lin, D.J., Systematic Unidirectional Error-Detecting Codes, IEEE Trans. Comput., 1985, pp. 1026–1032.

Omana, M., Losco, O., Metra, C., and Pagni, A., On the Selection of Unidirectional Error Detecting Codes for Self-Checking Circuits Area Overhead and Performance Optimization, Proc. 4 IEEE Int. On-line Testing Sympos., 2005, pp. 163–168.

Gessel, M., Morozov, V.S., Sapozhnikov, V.V., and Sapozhnikov, Vl.V., Logic Complement, a New Method of Checking the Combinational Circuits, Autom. Remote Control, 2001, no. 1, pp. 153–161.

Hartje, H., Sogomonyan, E.S., and Goessel, M., Code-Disjoint Circuits for Parity Codes, Proc. 6 Asian Test Sympos., 1997, pp. 100–105.

Levin, I., Ostrovsky, V., Keren, O., and Sinelnikov, V., Cascade Scheme for Concurrent Errors Detection, Proc. 9 EUROMICRO Conf. on Digital Syst. Design, 2006, pp. 359–368.

Ostrovsky, V. and Levin, I., Implementation of Concurrent Checking Circuits by Independent Subcircuits, Proc. 20 IEEE Int. Sympos. on Defect and Fault Tolerance in VLSI Syst. (DFT’05), California, 2005, pp. 343–351.

Levin, I., Matrosova, A., and Ostanin, S., Survivable Self-checking Sequential Circuits, Proc. IEEE Int. Sympos. on Defect and Fault Tolerance in VLSI Syst., San Francisco, 2001, pp. 395–402.

Logic Synthesis and Optimization Benchmarks, Report NC 27709, Berkley: Univ. of California, 1988.

Author information

Authors and Affiliations

Additional information

Original Russian Text © B.B. Abramov, O. Keren, I.S. Levin, V.I. Ostrovskii, 2009, published in Avtomatika i Telemekhanika, 2009, No. 7, pp. 139–150.

Rights and permissions

About this article

Cite this article

Abramov, B.B., Keren, O., Levin, I.S. et al. Constructing self-testing circuits with the use of step-by-step (cascade) control. Autom Remote Control 70, 1217–1227 (2009). https://doi.org/10.1134/S0005117909070121

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1134/S0005117909070121