Abstract

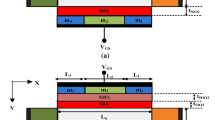

In this exposition, we have proposed the Dual Material Gate Double Gate Impact Ionization Metal Oxide Semiconductor (DMG DG IMOS) device with a gate engineered technique of Gate Stacking which is ordinarily used in MOSFET for performance augmentation. This paper compares the performance of four DG IMOS based devices i.e. Single Material Gate Double Gate IMOS (SMG DG IMOS), SMG Gate Stacked DG IMOS (SMG GS DG IMOS), DMG DG IMOS and DMG Gate stacked DG IMOS (DMG GS DG IMOS). The performance of all the devices has been investigated using 2-D simulations. The device structures of gate stacked devices have been developed with two gate oxides namely SiO2 and HfO2 and remaining parameters have been taken alike for all four devices. The doping concentration of source and drain regions for all four devices has been taken as 1020 cm−3 and the doping concentration of the intrinsic region has been taken as 1015 cm−3. The Gate Stacked devices showed better analog outcomes as compared to the other devices. The analog parameters evaluated include transconductance (gm), total gate capacitance (Cgg) and unity gain frequency (fT). The proposed design, DMG GS DG IMOS has been then analyzed for different channel lengths and dielectrics of gate oxide materials to optimize the gate engineered design for various applications.

Similar content being viewed by others

References

R.R. Schaller, Moore’s law: past, present and future. IEEE Spectr. 34(6), 52–59 (1997)

T. Skotnicki, G. Merckel, T. Pedron, The voltage-doping transformation: a new approach to the modeling of MOSFET short-channel effects. IEEE Electron Device Lett. 9(3), 109–112 (1988)

R.G. Dreslinski et al., Near-threshold computing: reclaiming moore’s law through energy efficient integrated circuits. Proc. IEEE 98(2), 253–266 (2010)

S.-H. Oh, D. Monroe, J.M. Hergenrother, Analytic description of short-channel effects in fully-depleted double-gate and cylindrical, surrounding-gate MOSFETs. IEEE Electron Device Lett. 21(9), 445–447 (2000)

K.K. Young, Short-channel effect in fully depleted SOI MOSFETs. IEEE Trans. Electron Devices 36(2), 399–402 (1989)

S.-H. Oh, D. Monroe, J.M. Hergenrother, Analytic description of short-channel effects in fully-depleted double-gate and cylindrical, surrounding-gate MOSFETs. IEEE Electron Device Lett. 21(9), 445–447 (2000)

A. Rusu, G.A. Salvatore, D. Jiménez, A.M. Ionescu, Metal-ferroelectric-meta-oxide-semiconductor field effect transistor with sub-60 mV/decade subthreshold swing and internal voltage amplification, in 2010 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2010), pp. 16–30

E.-H. Toh et al., I-MOS transistor with an elevated silicon–germanium impact-ionization region for bandgap engineering. IEEE Electron Device Lett. 27(12), 975–977 (2006)

S. Anand, R.K. Sarin, Analog and RFperformance of doping-less tunnel FETs with Si0.55Ge0.45 source. J. Comput. Electron. 15(3), 850–856 (2016)

S. Anand, R.K. Sarin, Performance investigation of InAs based dual electrode tunnel FET on the analog/RF platform. Superlattices Microstruct. 97, 60–69 (2016)

K. Boucart, A.M. Ionescu, Double-gate tunnel FET with high-$kappa $ gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

K. Gopalakrishnan, P.B. Griffin, J.D. Plummer, Impact ionization MOS (I-MOS)-Part I: device and circuit simulations. IEEE Trans. Electron Devices 52(1), 69–76 (2005)

L. Chang, S. Tang, T.-J. King, J. Bokor, C. Hu, Gate length scaling and threshold voltage control of double-gate MOSFETs, in Electron Devices Meeting, 2000. IEDM’00. Technical Digest. International (IEEE, 2000), pp. 719–722

R. Kraus, C. Jungemann, Investigation of the vertical IMOS-transistor by device simulation, in 10th International Conference on Ultimate Integration of Silicon, 2009. ULIS 2009 (IEEE, 2009), pp. 281–284

E.-H. Toh, G.H. Wang, L. Chan, G.-Q. Lo, D. Sylvester, C.-H. Heng, G. Samudra, Y.-C. Yeo, A complementary-I-MOS technology featuring SiGe channel and i-region for enhancement of impact-ionization, breakdown voltage, and performance, in 37th European Solid State Device Research Conference, 2007. ESSDERC 2007 (IEEE, 2007), pp. 295–298

C. Onal et al., A novel depletion-IMOS (DIMOS) device with improved reliability and reduced operating voltage. IEEE Electron Device Lett. 30(1), 64–67 (2009)

S. Singh, A. Raman, N. Kumar, Design and optimization analysis of dual material gate on DG-IMOS. J. Semicond. 38(12), 124003 (2017)

S. Ramaswamy, M.J. Kumar, Junctionless impact ionization MOS: proposal and investigation. IEEE Trans. Electron Devices 61(12), 4295–4298 (2014)

F.A. Hassani, M. Fathipour, M. Mehran, A comparison study between double and single gate p-IMOS, in AFRICON 2007 (IEEE, 2007), pp. 1–7

I. Saad, N. Bolong, Equivalent circuit model analysis of vertical impact ionization MOSFET (IMOS), in 2015 3rd International Conference on Artificial Intelligence, Modelling and Simulation (AIMS) (IEEE, 2015), pp. 451–456

R. Chau et al., High-spl kappa metal-gate stack and its MOSFET characteristics. IEEE Electron Device Lett. 25(6), 408–410 (2004)

D.K. Mohata, R. Bijesh, Y. Zhu, M.K. Hudait, R. Southwick, Z. Chbili, D. Gundlach, et al., Demonstration of improved heteroepitaxy, scaled gate stack and reduced interface states enabling heterojunction tunnel FETs with high drive current and high on-off ratio, in 2012 Symposium on VLSI technology (VLSIT) (IEEE, 2012), pp. 53–54

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Solay, L.R., Singh, S., Amin, S.I. et al. Design and Analysis of Gate Engineered Dual Material Gate Double Gate Impact Ionization Metal Oxide Semiconductor. Trans. Electr. Electron. Mater. 20, 132–140 (2019). https://doi.org/10.1007/s42341-018-0080-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42341-018-0080-2