Abstract

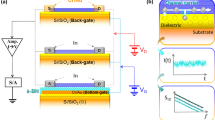

The impact of temperature in carrier transport of scattered SiNW MOSFET has been developed. Scattered SiNW MOSFET model includes the effects of elastic scattering, optical phonon emission, surface roughness scattering and random discrete dopants. The temperature effect of above mentioned scatterings in the device limits electron mobility, decreasing device current and transconductance. This work discusses the detailed behavior of analog parameters like transconductance (gm) and early voltage (VA). The validity of the proposed model has been confirmed by comparing the analytical results with the technology computer aided design simulation results.

Similar content being viewed by others

References

Sheik Arafat I, Balamurugan NB, Priya C (2014) Effects of roughness scattering in carrier transport of near ballistic silicon nanowire MOSFET. Appl Mech Mater 573:201–208

Natori K (2008) Compact modeling of ballistic nanowire MOSFETs. IEEE Trans Electron Dev 55:2877–2885

Martinez A, Seoane N, Brown A, Asenov A (2009) A comparison between a fully 3D real-space versus coupled mode-space NEGF in the study of variability in gate-all-around Si nanowire MOSFET. In: Proceedings of SISPAD, San Jose, CA, pp 194–197

Zilli M, Esseni D, Palestri P, Selmi L (2007) On the apparent mobility in nanometric n-MOSFET. IEEE Electron Dev Lett 28:1036–1039

Pala MG, Buran C, Poli S, Mouis M (2009) Full quantum treatment of surface roughness effects in silicon nanowires and double gate. J Comput Electron 8:374–381

Chang P-C, Lu JG (2008) ZnO nanowire field-effect transistor. IEEE Trans Electron Dev 55:164–171

Fischetti MV, Laux SE (1993) Monte Carlo study of electron transport in silicon inversion layers. Phys Rev B 48:2244–2274

Majima H, Saito Y, Hiramoto T (2001) Impact of quantum mechanical effects on design of nano-scale narrow channel n- and p-type MOSFETs. In: IEEE international electron devices meeting (IEDM) technical digest, pp 951–954

Niquet Y, Mera H, Delerue C (2012) Impurity-limited mobility and variability in gate-all-around silicon nanowires. Appl Phys Lett 100:153119–153125

Martinez A, Bescond M, Barker JR, Svizhenkov A, Anantram A, Asenov A (2007) A self consistent 3-D full real space NEGF simulator for studying non perturbarative effects in nanoMOSFET. IEEE Trans Electron Dev 54:2213–2222

Seoane N, Martinez A, Brown AR (2009) Current variability in Si nanowire MOSFETs due to random dopants in the source/drain regions: a fully 3-D NEGF simulation study. IEEE Trans Electron Dev 56:1388–1395

Natori K (2012) Compact modeling of quasi-ballistic nanowire MOSFETs. IEEE Trans Electron Dev 59:79–86

Wang R, Zhuge J, Huang R, Tian Y, Xiao H, Zhang L, Li C, Zhang X (2007) Analog/RF performance of Si nanowire MOSFETs and the impact of process variation. IEEE Trans Electron Dev 54:1288–1294

Kelzenberg MD, Evans DB, Filler MA, Putnam MC, Lewis NS, HA Atwater (2008) Single-nanowire Si solar cells. In: IEEE photovoltaic speacialists conference

Penzin O, Paasch G, Heinz F, Smith L (2011) Extended quantum correction model applied to six-band valence band near silicon/oxide interfaces. IEEE Trans Electron Dev 58:1614–1619

Penzin O, Smith L, Erlebach A, Lee K (2015) Layer thickness and stress-dependent correction for InGaAs low-field mobility in TCAD applications. IEEE Trans Electron Dev 62:493–500

Landauer R (1957) Spatial variation of currents and fields due to localized scatterers in metallic conduction. IBM J Res Dev 1:223–228

Grosso G, Moroni S, Parravicini GP (1989) Electronic structure of the InAs-GaSb superlattice studied by the renormalization method. Phys Rev B 40:12328–12334

Suk SD, Lee SY, Kim SM, Yoon EJ, Kim MS, Li M, Park CJ, Park JB, Kim DW, Park D, Ryu BI (2005) Highperformance 5-nm radius twin silicon nanowire MOSFET (TSNWFET): fabrication on bulk Si wafer, characteristics, and reliability. In: IEDM technical digest, pp 717–720

Li SS (1977) The dopant density and temperature dependence of electron mobility and resistivity in n-type silicon. NBS special publication, pp 400–413

Sato S (2010) Gate semi-around Si nanowire FET fabricated by conventional CMOS process with very high drivability. In: IEEE, pp 14–16

Jiang Y (2008) Performance breakthrough in 8 nm gate length gate-all-around nanowire transistors using metallic nanowire contacts. In: Technical digest of symposium on VLSI technology, pp 34–35

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Sheik Arafat, I., Balamurugan, N.B. & Bismillah Khan, S. Influence of Temperature in Scattered SiNW MOSFET. Proc. Natl. Acad. Sci., India, Sect. A Phys. Sci. 89, 35–40 (2019). https://doi.org/10.1007/s40010-017-0385-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40010-017-0385-2