Abstract

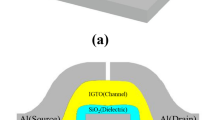

In this paper, we focus on the improvement of comprehensive device performance of Silicon Nanotube Tunnel Field Effect Transistor (NT_TFET) for ultra low power applications. In the design we have implanted 2nm Halo region at the source side of Si NT_TFET for improving the subthreshold swing and short channel effects (SCEs). To prove the concept, the performance of Silicon Nanowire tunnel FET (NW_TFET), Silicon Nanotube TFET without Halo (NT_TFET) and Silicon Nanotube TFET with halo (NT_FET_HALO) implant are compared. The impact of halo doping profile on the Subthreshold swing, ON and OFF current are investigated. Further, the degradation of OFF state current due to Halo doping is controlled by lightly doped drain.

Similar content being viewed by others

References

Kale S, Kondekar PN (2016) Superlattices and Microstructures Ferroelectric Schottky barrier tunnel FET with gate-drain underlap: proposal and investigation. Superlattices Microstructure 89:225–230

Boucart K, Ionescu AM (2007) Double-gate tunnel FET with high-K gate dielectric. IEEE Trans Electron Devices 54:1725–1733

Singh A, Chaudhary SK, Panday CK, Sharma SM, Sarkar CK (2019) Design and analysis of High K Silicon Nano Tube Tunnel FET Device IET Circuit, Devices and Systems (Accepted). https://doi.org/10.1049/iet-cds.2019.0230

Harris H, Choi K, Mehta N, Chandolu A, Biswas N, Kipshidze G, Nikishin S, Gangopadhyay S (2002) HfO2 gate dielectric with 0.5 nm equivalent oxide thickness. Appl Phys Lett

Memisevic E, Svensson J, Hellenbrand M, Lind E, Wernersson L-E (2017) Vertical InAs/GaAsSb/GaSb Tunneling Field-Effect Transistor on Si with S = 48 mV/decade and Ion = 10μA/μm for Ioff = 1nA/μm at VDS = 0.3 V IEEE International Electron Devices Meeting, IEDM. 19.1.1–19.1.4

Ionescu AM (2017) Nano-devices with advanced junction engineering and improved energy efficiency 17th. Int Workshop Junction Technol (IWJT): 1–6

Zhang Y Tunneling field effect transistor (TFET) with ultra shallow pockets formed by asymmetric ion implantation and method of making same U.S. Patent 9252250 B2, Feb. 2, 2016

Ashita SA, Loan MR (2018) A high-performance inverted-c tunnel junction FET with source–channel overlap pockets. IEEE Trans Electron Devices 65:763–768

Der Agopian PG, Martino JA, Vandooren A (2017) Study of line- TFET analog performance comparing with other TFET and MOSFET architectures . Solid-State Electron 128:43–47

Japa A, Majumder MK, Sahoo SK, Vaddi R (2019) Tunnel FET ambipolarity-based energy efficient and robust true random number generator against reverse engineering attacks . The Institution of Engineering and Technology (IET) 13:689– 695

Bhowmick B (2019) Emerging device: FINFET, tunnel FET and their applications. CSI Trans on ICT 7:221–225

Roy T, et al. (2016) Field-effect transistors built from all two-dimensional material components. ACS Nano 8:6259–6264

Shan G, Wang Y, Huang W (2011) Electronic transport characteristics in silicon nanotube field-effect transistors. Physica E: Low-dimensional Systems and Nanostructures 43:1655–1658

Jossy AM, Vigneswaran T (2014) A perspective review of tunnel field effect transistor with steeper switching behavior and low off current (IOFF) for Ultra Low Power Applications 6: 2092–2104

Xu M (2017) Two methods of tuning threshold voltage of bulk FinFETs with replacement high-k metal-gate stacks. Solid State Electron 129:52–60

Chandan K, Pandey DD, Chaudhury S (2018) Impact of dielectric pocket on analog and high-frequency performances of cylindrical gate-all-around tunnel FETs. ECS Journal of Solid State Science and Technology, The Electrochemical Society 7. https://doi.org/10.1149/2.0101805jss

Guin S, Chattopadhyay A, Karmakar A, Mallik A (2014) Impact of a pocket doping on the device performance of a schottky tunneling field-effect transistor . IEEE Trans Electron Devices 61:2515–2522

Fahad HM, Smith CE, Rojas JP, Hussain MM (2011) Silicon nanotube field effect transistor with core-shell gate stacks for enhanced high-performance operation and area scaling benefits . Nano Lett 119:4393–4399

Tekleab D (2014) Device performance of silicon nanotube field effect transistor. IEEE Electron Device Lett 35:506–508

Singh Avtar, Pandey CK, Chaudhury S, Sarkar CK (2018) Effect of strain in silicon nanotube FET devices for low power applications. The European Phys J Appl Phys

Kumar N, Mushtaq U, Amin SI, Anand S (2019) Design and performance analysis of Dual-Gate All around Core-Shell Nanotube TFET. Superlattices and Microstructures 125:356–364

Karimi NV, Pourasad Y (2015) Tunneling carbon nanotube field effect transistor with asymmetric graded double halo doping in channel. Asym-GDH-T-CNTFET Procedia Material Science 11:287– 292

Tekleab D, Tran HH, Sleight JW, Chidambarrao D (2014) Silicon Nanotube MOSFET, US 8,866,266 B2

Yadav M, Bulusu A, Dasgupta S (2015) Super-threshold semi analytical channel potential model for DG tunnel FET

Ghedini P, et al. (2017) Solid-state electronics study of line-TFET analog performance comparing with other TFET and MOSFET architectures . Solid State Electron 128:43–47

Acknowledgments

The authors would like to thank the Department of Electrical Engineering, NIT Silchar, for their valuable support in carrying out this research work.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Singh, A., Chaudhary, S., Sharma, S.M. et al. Improved Drive Capability of Silicon Nano Tube Tunnel FET Using Halo Implantation. Silicon 12, 2555–2561 (2020). https://doi.org/10.1007/s12633-019-00350-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-019-00350-y