Abstract

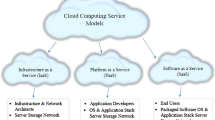

Hardware security has become more and more important in current information security architecture. Recently collected reports have shown that there may have been considerable hardware attacks prepared for possible military usage from all over the world. Due to the intrinsic difference from software security, hardware security has some special features and challenges. In order to guarantee hardware security, academia has proposed the concept of trusted integrated circuits, which aims at a secure circulation of IC design, manufacture and chip using. This paper reviews the main problems of trusted integrated circuits, and concludes four key domains of the trusted IC, namely the trusted IC design, trusted manufacture, trusted IP protection, and trusted chip authentication. The main challenges in those domains are also analyzed based on the current known techniques. Finally, the main limitations of the current techniques and possible future trends are discussed.

Similar content being viewed by others

References

Adee S. The hunt for the kill switch. IEEE Spectrum, 2008, 45(5): 34–39. http://spectrum.ieee.org/semiconductors/design/the-hunt-for-the-kill-switch, May 2014.

Markoff J. CYBERWAR: Old trick threatens the newest weapons. The New York Times, Oct. 2009. http://www.ny-times.com/2009/10/27/science/27trojan.html?_r=2&pagew, Apr. 2014.

De Mulder E, Örs S B, Preneel B et al. Differential power and electromagnetic attacks on a FPGA implementation of elliptic curve cryptosystems. Computers and Electrical Engineering, 2007, 33(5/6): 367–382.

Dehbaoui A, Lomne V, Maurine P et al. Enhancing electromagnetic attacks using spectral coherence based cartography. In VLSI-SoC: Technologies for Systems Integration, Becker J, Johann M, Reis R (eds.), Springer Berlin Heidelberg, 2011, pp.135–155.

Da Rolt J, Di Natale G, Flottes M L et al. New security threats against chips containing scan chain structures. In Proc. IEEE International Symposium on Hardware-Oriented Security and Trust (HOST), June 2011, p.110.

Yang B, Wu K, Karri R. Secure scan: A design-for-test architecture for crypto chips. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2006, 25(10): 2287–2293.

Bar-El H, Choukri H, Naccache D et al. The sorcerer's apprentice guide to fault attacks. Proceedings of the IEEE, 2006, 94(2): 370–382.

Aumüller C, Bier P, Fischer W et al. Fault attacks on RSA with CRT: Concrete results and practical countermeasures. In Proc. the Cryptographic Hardware and Embedded Systems (CHES), Aug. 2002, pp.260–275.

Yuan L, Qu G, Ghouti L et al. VLSI design IP protection: Solutions, new challenges, and opportunities. In Proc. the 1st IEEE NASA/ESA Conference on Adaptive Hardware and Systems, June 2006, pp.469–476.

Rostami M, Koushanfar F, Rajendran J, Karri R. Hardware security: Threat models and metrics. In Proc. International Conference on Computer-Aided Design, Nov. 2013, pp.819–823.

Wang X, Tehranipoor M, Plusquellic J. Detecting malicious inclusions in secure hardware: Challenges and solutions. In Proc. IEEE Int. Workshop Hardware-Oriented Security and Trust (HOST), June 2008, pp.15–19.

Karri R, Rajendran J, Rosenfeld K, Tehranipoor M. Trustworthy hardware: Identifying and classifying hardware Trojans. IEEE Computer, 2010, 43(10): 39–46.

Tehranipoor M, Koushanfar F. A survey of hardware Trojan taxonomy and detection. IEEE Design & Test of Computers, 2010, 27(1): 10–25.

Biere A, Cimatti A, Clarke E M et al. Symbolic model checking using SAT procedures instead of BDDs. In Proc. the 36th ACM/IEEE conference on Design automation (DAC), June 1999, pp.317–320.

Chakraborty R S, Narasimhan S, Bhunia S. Hardware Trojan: Threats and emerging solutions. IEEE International High Level Design Validation and Test Workshop, Nov. 2009, pp.166–171.

Chakraborty R S, Bhunia S. Security against hardware Trojan through a novel application of design obfuscation. In Proc. IEEE/ACM Int. Conf. Computer-Aided Design (ICCAD), Nov. 2009, pp.113–116.

Waksman A, Sethumadhavan S. Silencing hardware back-doors. In Proc. IEEE Symposium on Security and Privacy, May 2011, pp.49–63.

Gu J, Qu G, Zhou Q. Information hiding for trusted system design. In Proc. the 46th ACM/IEEE Design Automation Conference (DAC), July 2009, pp.698–701.

Chakraborty R S, Paul S, Bhunia S. On-demand transparency for improving hardware Trojan detectability. In Proc. Hardware-Oriented Security and Trust (HOST), June 2008, pp.48–50.

Kim L W, Villasenor J D, Koc C K. A Trojan-resistant system-on-chip bus architecture. In Proc. Int. Conf. Military Communication, Oct. 2009.

Abramovici M, Bradley P. Integrated circuit security: New threats and solutions. In Proc. the 5th Cyber Security and Information Intelligence Research Workshop, Apr. 2009, Article No.55.

Hicks M, Finnicum M, King S T et al. Overcoming an untrusted computing base: Detecting and removing malicious hardware automatically. In Proc. IEEE Symposium on Security and Privacy, May 2010, pp.159–172.

Zhang J, Yuan F, Wei L et al. VeriTrust: Verification for hardware trust. In Proc. the 50th Annual Design Automation Conference, May 29-June 7, 2013, pp.1–8.

Chakraborty R S, Wolff F, Paul S. MERO: A statistical approach for hardware Trojan detection. In Proc. the 11th Workshop on Cryptographic Hardware and Embedded Systems (CHES), Sept. 2009, pp.396–410.

Salmani H, Tehranipoor M, Plusquellic J. A novel technique for improving hardware Trojan detection and reducing Trojan activation time. IEEE Transactions on VLSI, 2012, 20(1): 112–125.

Banga M, Hsiao M S. A region based approach for the identification of hardware Trojans. In Proc. IEEE International Workshop on Hardware-Oriented Security and Trust (HOST), June 2008, pp.40–47.

Potkonjak M, Nahapetian A, Nelson M, Massey T. Hardware Trojan horse detection using gate-level characterization. In Proc. the 46th Design Automation Conference (DAC), July 2009, pp.688–693.

Cha B, Gupta S K. Trojan detection via delay measurements: A new approach to select paths and vectors to maximize effectiveness and minimize cost. In Proc. Conference on Design, Automation and Test in Europe, Mar. 2013, pp.1265–1270.

Wei S, Meguerdichian S, Potkonjak M. Malicious circuitry detection using thermal conditioning. IEEE Transactions on Information Forensics and Security, 2011, 6(3): 1136–1145.

Agrawal D, Baktir S, Karakoyunlu D et al. Trojan detection using IC fingerprinting. In Proc. IEEE Symposium Security and Privacy, May 2007, pp.296–310.

Jin Y, Makris Y. Hardware Trojan detection using path delay fingerprint. In Proc. IEEE International Workshop onHardware-Oriented Security and Trust (HOST), June 2008, pp.51–57.

Skorobogatov S, Woods C. Breakthrough silicon scanning discovers backdoor in military chip. In Proc. the 14th Workshop on Cryptographic Hardware and Embedded Systems (CHES), Sept. 2012, pp.23–40.

Tehranipoor M, Salmani H, Zhang X et al. Trustworthy hard-ware: Trojan detection and design-for-trust challenges. IEEE Computer, 2011, 44(7): 66–74.

Yang B, Wu K, Karri R. Scan based side channel attack on dedicated hardware implementations of data encryption standard. In Proc. IEEE International Test Conference, Oct. 2004, pp.339–344.

Koushanfar F. Hardware metering: A survey. In Introduction to Hardware Security and Trust, Tehranipoor M, Wang C (eds.), Springer New York, 2012, pp.103–122.

Roy J, Koushanfar F, Markov I. Ending piracy of integrated circuits. IEEE Computer, 2010, 43(10): 30–38.

Chakraborty R S, Bhunia S. HARPOON: An obfuscation-based SoC design methodology for hardware protection. IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, 2009, 28(10): 1493–1502.

Moudgil R, Ganta D, Nazhandali L et al. A novel statistical and circuit-based technique for counterfeit detection in existing ICs. In Proc. the 23rd ACM International Conference on Great Lakes Symposium on VLSI, May 2013, pp.1–6.

Kocher P, Jaffe J, Jun B. Differential power analysis. In Proc. the 19th Advances in Cryptology, May 1999, pp.388–397.

Rolt J D, Natale G D, Flottes M et al. A novel differential scan attack on advanced DFT structures. ACM Transactions on Design Automation of Electronic Systems, 2013, 18(4): Article No.58.

Torrance R, James D. The state-of-the-art in semiconductor reverse engineering. In Proc. the 48th IEEE/ACM Design Automation Conference (DAC), June 2011, pp.333–338.

Rohatgi P. Improved techniques for side-channel analysis. In Cryptographic Engineering, Koç Ç K (ed.), Springer US, pp.381–406.

Rajendran J, Pino Y, Sinanoglu O, Karri R. Security analysis of logic obfuscation. In Proc. the 49th IEEE/ACM Design Automation Conference (DAC), June 2012, pp.83–89.

Baumgarten A, Tyagi A, Zambreno J. Preventing IC piracy using reconfigurable logic barriers. IEEE Design and Test of Computers, 2010, 27(1): 66–75.

Rajendran J, Sam M, Sinanoglu O, Karri R. Security analysis of integrated circuit camouflaging. In Proc. ACM SIGSAC Conference on Computer & Communications Security (CCS), Nov. 2013, pp.709–720.

Qu G, Potkonjak M. Fingerprinting intellectual property using constraint-addition. In Proc. the 37th IEEE/ACM Design Automation Conference (DAC), June 2000, pp.587–592.

Lach J, Mangione-Smith W H, Potkonjak M. Fingerprinting digital circuits on programmable hardware. In Proc. the 2nd Int. Workshop on Information Hiding, April 1998, pp.16–31.

Qu G, Potkonjak M. Intellectual Property Protection in VLSI Design. Springer, 2003.

Smerdon M. Security solutions using Spartan-3 generation FPGAs (v1.1). Xilinx White Paper, Apr. 2008, http://www.xilinx.com/support/documentation/white papers/wp266.pdf, May 2014.

Zhang J, Lin Y, Lyu Y et al. FPGA IP protection by binding finite state machine to physical unclonable function. In Proc. the 23rd Field Programmable Logic and Applications (FPL), Sept. 2013.

Maes R, Schellekens D, Verbauwhede I. A pay-per-use licensing scheme for hardware IP cores in recent SRAM-FPGAs.IEEE Trans. Information Forensics and Security, 2012, 7(1): 98–108.

Alkabani Y, Koushanfar F, Potkonjak M. Remote activation of ICs for piracy prevention and digital right management. In Proc. IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Nov. 2007, pp.674–677.

Koushanfar F. Provably secure active IC metering techniques for piracy avoidance and digital rights management. IEEE Trans. Information Forensics and Security, 2012, 7(1): 51–63.

Chatterjee K, Das D. Semiconductor manufacturers' efforts to improve trust in the electronic part supply chain. IEEE Trans. Components and Packaging Technologies, 2007, 30(3): 547–549.

Huang K, Carulli J, Makris Y. Parametric counterfeit IC detection via support vector machines. In Proc. IEEE Int. Symp. Defect and Fault Tolerance in VLSI and Nanotechnology Systems, Oct. 2012, pp.7–12.

Cui A, Chang C, Tahar S et al. A robust FSM watermarking scheme for IP protection of sequential circuit design. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2011, 30(5): 678–690.

Yin C, Qu G. Temperature-aware cooperative ring oscillator PUF. In Proc. IEEE International Workshop on Hardware-Oriented Security and Trust (HOST), July 2009, pp.36–42.

Zhang J, Wu Q, Lyu Y et al. Design and implementation of a delay-based PUF for FPGA IP protection. In Proc. CAD/CG, Oct. 2013, pp.1–6.

Salmani H, Tehranipoor M. Layout-aware switching activity localization to enhance hardware Trojan detection. IEEE Transactions on Information Forensics and Security, 2012, 7(1): 76–87.

Rad R, Plusquellic J, Tehranipoor M. Sensitivity analysis to hardware Trojans using power supply transient signals. In Proc. IEEE International Workshop on Hardware-Oriented Security and Trust (HOST), June 2008, pp.3–7.

Bhunia S, Abramovici M, Agrawal D et al. Protection against hardware Trojan attacks: Towards a comprehensive solution. IEEE Design and Test, 2013, 30(3):6–17.

Forte D, Bao C, Srivastava A. Temperature tracking: An innovative run-time approach for hardware Trojan detection. In Proc. IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Nov. 2013, pp.532–539.

Author information

Authors and Affiliations

Corresponding author

Additional information

The work is supported by the National Natural Science Foundation of China under Grant No. 61228204 and the National Science and Technology Major Project of China under Grant No. 2013ZX01039001-002-003.

Electronic supplementary material

Below is the link to the electronic supplementary material.

ESM 1

(PDF 192 kb)

Rights and permissions

About this article

Cite this article

Lv, YQ., Zhou, Q., Cai, YC. et al. Trusted Integrated Circuits: The Problem and Challenges. J. Comput. Sci. Technol. 29, 918–928 (2014). https://doi.org/10.1007/s11390-014-1479-9

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11390-014-1479-9