Abstract

Discrete Wavelet Transform (DWT) is widely used in digital image and video processing due to its various advantages over other similar transform techniques. In this paper, efficient hardware architecture of Optimized Haar Wavelet Transform is proposed which is modeled using Optimized Kogge–Stone Adder/Subtractor, Optimized Controller, Buffer, Shifter and D_FF blocks. The existing Kogge–Stone Adder architecture is optimized by using Modified Carry Correction block which uses parallel architecture to reduce the computational delay. Similarly, the Controller block is optimized by using Clock Dividers and Reset Counter interdependently. To preserve the accuracy of the processed data, suitable size of intermediate bits in fractional format with the help of Q-notation is considered. The comparison results show that the proposed architecture performs better than existing ones concerning both hardware utilization and data accuracy.

Similar content being viewed by others

References

Aishwarya, N., Abirami, S. & Amutha, R. (2016). Multi-focus image fusion using discrete wavelet transform and sparse representation. In IEEE international conference on wireless communications, signal processing and networking (WiSPNET) (pp. 2377–2382). https://doi.org/10.1109/WiSPNET.2016.7566567.

Alsubari, A., Satange, D. N., Ramteke, R. J. (2017). Facial expression recognition using wavelet transform and local binary pattern. In 2nd IEEE international conference for convergence in technology (I2CT) (pp. 338–342). https://doi.org/10.1109/I2CT.2017.8226147.

Anitha, M., & Sathish, K. (2018). Implementation of high speed 32 bit Kogge–Stone adder. Journal of Signal Processing and Wireless Networks, 3(1), 37–40.

Aravind B. N. & Suresh, K. V. (2015). An improved image denoising using wavelet transform. In IEEE international conference on trends in automation, communications and computing technology (I-TACT-15) (pp. 1–5). https://doi.org/10.1109/ITACT.2015.7492679.

Arora, A., & Niranjan, V. (2017). A new 16-bit high speed and variable stage carry skip adder. In 3rd IEEE international conference on computational intelligence and communication technology (CICT) (pp. 1–4). https://doi.org/10.1109/CIACT.2017.7977359.

Bamerni, S. A., & Al-Sulaifanie, A. K. (2018). An efficient non-separable architecture for Haar wavelet transform with lifting structure. International Journal of Computers, 12, 43–53.

Bamerni, S. A., & Al-Sulaifanie, A. K. (2019). An efficient non-separable architecture for Haar wavelet transform with lifting structure. Journals of Microprocessors and Microsystems, 71, 1–7. https://doi.org/10.1016/j.micpro.2019.102881.

Basics of Euclidean distance for image processing. [Online] Available https://en.wikipedia.org/wiki/Euclidean_distance. Accessed 26 March 2020.

Bhairannawar, S. S., Sarkar, S., & Raja, K. B. (2018a). FPGA implementation of optimized Karhunen–Loeve transform for image processing applications. Journal of Real time Image Processing. https://doi.org/10.1007/s11554-018-0776-x.

Bhairannawar, S. S., Sayantam, S., Raja, K. B., & Venugopal, K. R. (2018b). Implementation of fingerprint based biometric system using optimized 5/3 DWT architecture and modified CORDIC based FFT. Journal of Circuits, Systems and Signal Processing,37(1), 342–366. https://doi.org/10.1007/s00034-017-0555-0.

Bhairannawar, S. S., Raja, K. B., & Venugopal, K. R. (2016). An efficient reconfigurable architecture for fingerprint recognition. Journal of VLSI Design,. https://doi.org/10.1155/2016/9532762.

Bhardwaj, A., & Khunteta, A. (2017). Video watermarking equations using DWT and DCT sub-sub bands for secure transmission over communication channels: A research paper. In IEEE international conference on power, control, signals and instrumentation engineering (ICPCSI) (pp. 435–440). https://doi.org/10.1109/ICPCSI.2017.8392333.

Chakraborty, A., & Banerjee, A. (2020). Area and memory efficient tunable VLSI implementation of DWT filters for image decomposition using distributed arithmetic. International Journal of Electronics,. https://doi.org/10.1007/s00034-019-01328-2.

Datasheet of Digilent ATLYS FPGA board. [Online] Available at https://reference.digilentinc.com/_media/atlys:atlys:atlys_rm.pdf. Accessed 26 March 2020.

Elakkiya, S., & Audithan, S. (2014). Feature based object recognition using discrete wavelet transform. In Second IEEE international conference on current trends in engineering and technology (ICCTET) (pp. 1–4). https://doi.org/10.1109/ICCTET.2014.6966323.

Gafsi, M., Ajili, S., Hajjaji, M. A., & Mtibaa, A. (2016). XSG for hardware implementation of a robust watermarking system. In 17th IEEE international conference on sciences and techniques of automatic control and computer engineering (STA) (pp. 117–122). https://doi.org/10.1109/STA.2016.7952031.

Gonzalez, R. C., & Woods, R. E. (2008). Digital image processing (3rd ed.). London: Pearson Education.

Gonzalez, R. C., Woods, R. E., & Eddins, S. L. (2009). Digital image processing using MATLAB (2nd ed.). Knoxville, TN: Gatesmark Publishing.

Gupta, V., Mahle, R. & Shriwas, R. S. (2013). Image denoising using wavelet transform method. In Tenth IEEE international conference on wireless and optical communications networks (WOCN) (pp. 1–4). https://doi.org/10.1109/WOCN.2013.6616235.

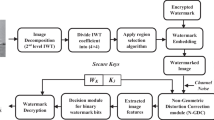

Hajjaji, M. A., Gafsi, M., Abdelali, A. B., & Mtibaa, A. (2019). FPGA implementation of digital images watermarking system based on discrete Haar wavelet transform. Journal of Security and Communication Networks,. https://doi.org/10.1155/2019/1294267.

Harender, & Sharma, R. K. (2017) EEG signal denoising based on wavelet transform. In IEEE international conference of electronics, communication and aerospace technology (ICECA) (pp. 758–761). https://doi.org/10.1109/ICECA.2017.8203645.

Hasan, K. K., Ngah, U. K., & Salleh, M. F. M. (2013). Multilevel decomposition discrete wavelet transform for hardware image compression architectures applications. In IEEE International conference on control system, computing and engineering (pp. 315–320). https://doi.org/10.1109/ICCSCE.2013.6719981.

IEEE 754 format for floating number. [Online] Available https://en.wikipedia.org/wiki/Single-precision_floating-point_format. Accessed 26 March 2020.

Jayaraman, S., Esakkirajan, S., & Veerakumar, T. (2009). Digital image processing. London: Tata McGraw Hill.

Karris, S. T. (2006). Introduction to simulink with engineering applications. Newton: Orchard Publications.

Kaur, A., & Toor, C. K. (2017). Implementation of parallel prefix adders using FPGA’s. Australian Journal of Basic and Applied Sciences, 11(8), 100–106.

Khan, S., Nazir, S., Hussain, A., Ali, A., & Ullah, A. (2019). An efficient JPEG image compression based on Haar wavelet transform, discrete cosine transform, and run length encoding techniques for advanced manufacturing processes. Journal of Measurement and Control, 52, 1532–1544. https://doi.org/10.1177/0020294019877508.

Kogge, P. M., & Stone, H. S. (1973). A parallel algorithm for the efficient solution of a general class of recurrence relations. IEEE Transactions on Computers, 22(8), 786–793. https://doi.org/10.1109/TC.1973.5009159.

Koyada, B., Meghana, N., Jaleel M. O., & Jeripotula, P. R. (2017). A comparative study on adders. In IEEE international conference on wireless communications, signal processing and networking (WiSPNET) (pp. 2226–2230). https://doi.org/10.1109/WiSPNET.2017.8300155.

Lee, B. D., & Oklobdzija, V. G. (1990). Optimization and speed improvement analysis of carry-lookahead adder structure. In Twenty-fourth asilomar conference on signals, systems and computers (pp. 359–362). https://doi.org/10.1109/ACSSC.1990.523471.

Mallat, S. (2008). A wavelet tour of signal processing: The sparse way (1st ed.). London: Academic Press.

Mamatha, G., Sumalatha, V., & Lakshmaiah, M. V. (2015). FPGA implementation of satellite image fusion using wavelet substitution method. In IEEE international science and information conference (SAI) (pp. 1155–1159). https://doi.org/10.1109/SAI.2015.7237290.

Marques, O. (2012). Practical Image and Video Processing Using MATLAB (1st ed.). London: Wiley-IEEE Press.

Mhamunkar, N. S., & Gayal, B. S. (2015). Design and implementation of generic 2-D biorthogonal discrete wavelet transform on FPGA. In IEEE international conference on energy systems and applications (pp. 622–627). https://doi.org/10.1109/ICESA.2015.7503424.

Mohammadi, S., Omidi, R., & Lotfinejad, M. (2010). Low-power area-efficient fault tolerant adder in current mode multi valued logic using Berger codes. Journal of Electronic Testing, 36, 555–563. https://doi.org/10.1007/s10836-020-05887-0.

Nashat, A. A., & Hussain, N. M. H. (2016). Image Compression based upon wavelet transform and a statistical threshold. In IEEE international conference on optoelectronics and image processing (ICOIP) (pp. 20–24). https://doi.org/10.1109/OPTIP.2016.7528492.

Nedunuri, S., Cheung, J. Y., & Nedunuri, P. (2006). Design of low memory usage discrete wavelet transform on FPGA using novel diagonal scan. In IEEE international symposium on parallel computing in electrical engineering (PARELEC) (pp. 1–6). https://doi.org/10.1109/PARELEC.2006.29.

Palnitkar, S. (2003). Verilog HDL: A guide to digital design and synthesis (2nd ed.). London: Pearson Education.

Penchalaiah, U. & Siva Kumar, V. G. (2018). Design of high-speed and energy-efficient parallel prefix Kogge–Stone adder. In IEEE international conference on system, computation, automation and networking (ICSCAN) (pp. 1-7). https://doi.org/10.1109/ICSCAN.2018.8541143.

Prasad, L., & Iyengar, S. S. (1997). Wavelet analysis with applications to image processing (1st ed.). London: CRC Press.

Rajasekhar, V., Vaishnavi, V., Koushik, J. & Thamarai, M. (2014). An efficient image compression technique using discrete wavelet transform (DWT). In IEEE international conference on electronics and communication systems (ICECS) (pp. 1–4). https://doi.org/10.1109/ECS.2014.6892826.

Roth, C. H. (1992). Fundamentals of logic design (1st ed.). Mumbai: Jaico Publishing House.

Roth, C. H. (2006). Digital system design using VHDL. Boston, MA: Cengage Learning.

San, A. M., & Yakunin, A. N. (2018). Reducing the hardware complexity of a parallel prefix adder. In IEEE conference of Russian young researchers in electrical and electronic engineering (EIConRus) (pp. 1348–1351). https://doi.org/10.1109/EIConRus.2018.8317346.

Sateesh Kumar, H. C., Sarkar, S., Bhairannawar, S. S., Raja, K. B., & Venugopal, K. R. (2015). FPGA implementation of moving object and face detection using adaptive threshold. International Journal of VLSI Design and Communication Systems, 6(5), 15–35. https://doi.org/10.5121/vlsic.2015.6502.

Shilpa, K. C., Shwetha, M, Geetha, B. C, Lohitha, D. M., Navya & Pramod, N. V. (2018). Performance analysis of parallel prefix adder for datapath VLSI design. In Second IEEE international conference on inventive communication and computational technologies (ICICCT) (pp. 1552–1555). https://doi.org/10.1109/ICICCT.2018.8473087.

Shrivastava, A., Churhe, S., Bhagat, H., & Wamankar, R. (2017). Design and estimation of delay, power and area for parallel prefix adders. International Journal of Engineering Research and Application, 7(4), 1–8. https://doi.org/10.9790/9622-0704050108.

Siddmal, R. R. R. S. V. (2017). Hardware implementation of optimized Kogge–Stone adder. International Journal of Emerging Technology in Computer Science and Electronics,14(2), 1–8.

Singh, A., & Srinivasan, S. (2003). Digital signal processing implementations: Using DSP microprocessors—with examples from TMS320C54xx. Nelson Engineering.

Smith, M. J. S. (2004). Application specific integrated circuit (1st ed.). London: Pearson Education.

Soares, L. B., da Rosa, M. M. A., Diniz, C. M., da Costa, E. A. C., & Bampi, S. (2019). Design methodology to explore hybrid approximate adders for energy-efficient image and video processing accelerators. IEEE Transactions on Circuits and Systems I: Regular Papers, 66(6), 2137–2150. https://doi.org/10.1109/TCSI.2019.2892588.

Standard Video Database. [Online] Available at https://media.xiph.org/video/derf/. Accessed 26 March 2020.

Talukder, K. H., & Harada, K. (2007). Haar wavelet based approach for image compression and quality assessment of compressed image. IAENG International Journal of Applied Mathematics, 36(1), 1–8.

Talukder, S., Singh, R., Bora, S., & Paily, R. (2020). An efficient architecture for QRS detection in FPGA using integer Haar wavelet transform. Journal of Circuits, Systems, and Signal Processing, 39, 3610–3625. https://doi.org/10.1007/s00034-019-01328-2.

Tapasvi, B., Bala Sinduri, K., Lakshmi, B. G. S. S. B., & Udaya Kumar, N. (2015). Implementation of 64-bit Kogge–Stone carry select adder with ZFC for efficient area. In IEEE international conference on electrical, computer and communication technologies (ICECCT) (pp. 1–6). https://doi.org/10.1109/ICECCT.2015.7226154.

Tyagi, A. (1993). A reduced-area scheme for carry-select adders. IEEE Transactions on Computers, 42(10), 1163–1170. https://doi.org/10.1109/12.257703.

Vaidyanathan, P. P. (1993). Multirate systems and filter banks (1st ed.). London: Pearson Education.

Vamsi, A. K., Kumar, N. U., Sindhuri, K. B., & Teja, G. S. C. (2018). A systematic delay and power dominant carry save adder design. In IEEE international conference on smart systems and inventive technology (ICSSIT) (pp. 918–922). https://doi.org/10.1109/ICSSIT.2018.8748789.

Vijendra, V., & Kulkarni, M (2016). ECG signal filtering using DWT haar wavelets coefficient techniques. In IEEE international conference on emerging trends in engineering, technology and science (ICETETS) (pp. 1-6). https://doi.org/10.1109/ICETETS.2016.7603040.

Wang, Z., Jullien, G. A., Miller, W. C., Wang, J. (1993). New concepts for the design of carry lookahead adders. In IEEE international symposium on circuits and systems (pp. 1837–1840). https://doi.org/10.1109/ISCAS.1993.394104.

Weste, N. H. E., & Eshraghian, K. (1994). Principles of CMOS VLSI design (2nd ed.). London: Addison-Wesley.

Wolf, W. (2004). FPGA-based system design. Prentice: Prentice Hall.

Xiang, L. M., Zabidi, M. M. Ah. Awab, A. H., & Ab Rahman, Ab A. (2018). VLSI implementation of a fast Kogge–Stone parallel-prefix adder. Journal of Physics: Conference Series, 1049, 1–11. https://doi.org/10.1088/1742-6596/1049/1/012077.

Xilinx ISE In-Depth Tutorial. [Online] Available at https://www.xilinx.com/support/documentation/sw_manuals/xilinx14_1/ise_tutorial_ug695.pdf. Accessed 26 March 2020.

Zhang, J., & Zhang, Q. (2015). Image fusion algorithm based on wavelet transform. In 4th IEEE international conference on advanced information technology and sensor application (AITS) (pp. 47–50). https://doi.org/10.1109/AITS.2015.19.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendices

Appendices

The user-defined symbols are used in all the algorithms and equations present in this paper are as follows

-

\({{\sim \,\leftarrow }}\) Logical NOT Operation.

-

\({{| \,\leftarrow }}\) Logical OR Operation.

-

\({{\bigoplus \leftarrow }}\) Logical XOR Operation.

-

\( {{ \& \leftarrow }}\) Logical AND Operation.

-

\({{{(, )}\big /{\{,\}}\big /{[, ]} \leftarrow }}\) Logical Concatenation Operation.

-

\({{(x~downto~y) \leftarrow }}\) Data of Length (x-y+1).

-

\({{(N) \leftarrow }}\) Bit Present in Nth Position of a Binary Digit.

Rights and permissions

About this article

Cite this article

Sarkar, S., Bhairannawar, S.S. Efficient FPGA architecture of optimized Haar wavelet transform for image and video processing applications. Multidim Syst Sign Process 32, 821–844 (2021). https://doi.org/10.1007/s11045-020-00759-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11045-020-00759-4