Abstract

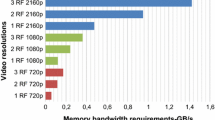

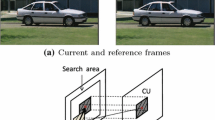

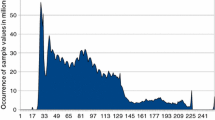

In this paper, a low-cost compatible motion compensator is implemented and integrated into a macroblock-level three-stage-pipelined HDTV decoder, in which an embedded compression (EC) engine is realized as well. The decoder with EC engine is designed to reduce the power consumption and memory bandwidth requirement since memory accesses are reduced. In the motion compensator, a boundary judgment scheme for reference pixel fetching is proposed to provide seamless integration in HDTV video decoder for the block-based EC engines. Furthermore, a buffer sharing mechanism is adopted to reduce extra memory requirement involved by EC. The reference pixel fetching unit costs only 17.3 K logic gates when the working frequency is set to 166.7 MHz. On average, when decoding HD1080 video sequence, 30% memory access reduction and 24% memory power consumption saving are achieved when a near lossless EC algorithm is integrated in the video decoder. In other words, the proposed motion compensator makes the EC engine an integral part of a memory reduced decoder without extra cost. Additionally, since the work in this paper is based on EC schemes, the EC design criterion are discussed, and several useful rules on the selection of EC algorithm are addressed for the video decoder of corresponding VLSI architecture.

Similar content being viewed by others

References

Bruni R, Chimienti A, Lucenteforte M, Paul D, Sannino R (1998) A novel adaptive vector quantization method for memory reduction in MPEG-2 HDTV decoders. IEEE Trans Consum Electron 44(3):537–544

Budagavi M, Zhou M (2008) Video coding using compressed reference frames, In: Proc. 2008 IEEE int. conf. on acoustics, speech and signal processing, pp 1165–1168

Cheng CC, Tseng PC, Huang CT, Chen LG (2005) Multi-mode embedded compression codec engine for power-aware video coding system. In: Proc. IEEE workshop on signal processing syst. design and implemen, pp 532–537

Chen WY, Ding LF, Tsung PK, Chen LG (2008) Architecture design of high performance embedded compression for high definition video coding. In: Proc. IEEE int. conf. on multimedia and expo, pp 825–828

Chien H, Chen H, Huang L, Guo J (2005) A low-power motion compensation IP core design for MPEG-1/2/4 video decoding. In: Proc. 2005 IEEE int. symp. on circuits syst., pp 4542–4545

de With PH, Frencken PH, Schaar-Mitrea MV (1998) An MPEG decoder with embedded compression for memory reduction. IEEE Trans Consum Electron 44(3):545–555

Gao H, Qiao F, Yang H (2008) A lossless memory reduction and efficient frame storage architecture for HDTV video decoder. In: Proc. IEEE int. conf. on audio, language and image processing, pp 593–598

Graham SL, Snir M, Patterson CA (2004) Getting up to speed: the future of supercomputing. The National Academies Press, Washington, DC

Jia X, Chen G, Zou W (2005) A high-speed memory interface architecture for MPEG-2 video decoder. In: Proc. 2005 conf. on high density microsystem design package and component failure analysis

Kim H, Park, IC (1999) Array address translation for SDRAM-based video processing applications. Electron Lett 35(28):1929–1931

Lee TY (2003) A new frame-recompression algorithm and its hardware design for MPEG-2 video decoders. IEEE Trans Circuits Syst Video Technol 13(6):529–534

Lee YX, Tsai TH (2008) An efficient embedded compression algorithm using adjusted binary code method. In: Proc. 2008 IEEE int. symp. on circuits and syst., pp 2586–2589

Lee Y, Rhee CE, Lee HJ (2007) A new frame recompression algorithm integrated with H.264 video compression. In: Proc. 2007 IEEE int. symp. on circuits and syst., pp 1621–1624

Li Y, He Y (2008) Bandwidth optimized and high performance interpolation architecture in motion compensation for H.264/AVC HDTV decoder. J Signal Process Syst 52(2):111–126

Lee C, Yu Y (2008) Design of a motion compensation unit for H.264 decoder using 2-dimensinal circular register files. In: Proc. 2008 IEEE int. SoC design conf., pp 109–112

Li Y, Qu Y, He Y (2007) Memory cache based compensation architecture for HDTV H.264/AVC decoder. In: Proc. 2007 IEEE int. symp. on circuits syst., pp 2906–2909

Micron (2009) SDRAM system-power calculator. www.micron.com

Micron (2002) Data sheet of synchronous DRAM MT48LC4M32B2. www.micron.com

Ohira H, Karube F (1999) A memory reduction approach for MPEG decoding system. IEICE Trans Fundam E82-A:1588–1591

Park SI, Yi Y, Park IC (2003) High performance memory mode control for HDTV decoders. IEEE Trans Consum Electron 49(4):1348–1353

Tsai CY, Chen TC, Chen TW, Chen LG (2005) Bandwidth optimized motion compensation hardware design for H.264/AVC HDTV decoder. In: Proc. 48th midwest symp. on circuits syst., pp 1199–1202

Zheng J, Gao W, Wu D, Xie D (2008) A novel VLSI architecture of motion compensation for multiple standards. IEEE Trans Consum Electron 54(2):687–694

Zhu J, Hou L, Wu W (2004) High performance synchronous DRAMs controller in H.264 HDTV decoder. In: Proc. 7th int. conf. on solid-state integrated circuits technology, pp 1621–1624

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Gao, H., Qiao, F. & Yang, H. Design and implementation of motion compensator in memory reduced HDTV decoder with embedded compression engine. Multimed Tools Appl 56, 597–614 (2012). https://doi.org/10.1007/s11042-010-0628-6

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11042-010-0628-6