Abstract

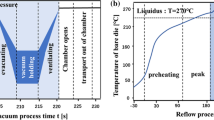

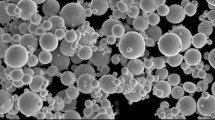

The void fraction in the solder joint of a chip resistor and its effect on the solder joint strength and reliability were investigated. The solder joint of a chip resistor has two regions: solder beneath the component and solder fillet. Although the total void fraction was similar irrespective of the component size, the void fraction of solder beneath the component increased and that of solder fillet decreased as the component size increased. The void fraction decreased considerably under vacuum reflow compared with that under air reflow. Furthermore, the vacuum reflowed samples showed similar void fraction characteristics as the air reflowed samples: the void fraction in the solder beneath the chip resistor increased and that in the solder fillet decreased as the chip resistor size increased. For both air and vacuum reflow, the shear strength of the chip resistor solder joint decreased as the chip size increased. The reliability of the chip resistor joint was evaluated using a thermal shock test. As the number of thermal shock cycles increased, the shear strength of the chip resistor solder joint decreased. Up to 2000 cycles, the shear strength reduction rates were similar irrespective of the component size. However, after 3000 cycles, the shear strength reduction rate of the large components (0805, 1210) was to about 50%, which was twice that of the small components (0402, 0603). Cross-sectional SEM after the thermal shock test revealed that a generated crack merged with a void, forming a long crack and lowering the joint reliability.

Similar content being viewed by others

References

L.J. Ladani, A. Dasgupta, J. Electron. Packag. 129(3), 273–277 (2007)

A. DerMarderosian, V. Gionet, Reliability Physics Symposium, 21st Annual, IEEE, pp. 235–241 (1983)

N. Lee, W. O’Hara, in Proc. Surf. Mount Int. pp. 462–471 (1995)

R.K. Wassink, Solder in Electronics (Electrochemical Publications, New York, 1989)

M. Yunus, K. Srihari, J. Pitarresi, A. Primavera, Microelectron. Reliab. 43(12), 2077–2086 (2003)

S. Sethuraman, R. Coyle, R. Popowich, P. Read, in SMTAI Conf. Proc. (2007)

R. Coyle, H. McCormick, P. Read, R. Popowich, J. Osenbach, in SMTAI Conf. Proc. p. 14 (2010)

Q. Yu, T. Shibutani, D.-S. Kim, Y. Kobayashi, J. Yang, M. Shiratori, Microelectron. Reliab. 48(3), 431–437 (2008)

T.-C. Chiu, K. Zeng, R. Stierman, D. Edwards, K. Ano, in Electronic Components and Technology Conference, 2004, Proc. 54th, IEEE, pp. 1256–1262 (2004)

IPC-610D standard, Acceptability of Electronic Assemblies, Association Connecting Electroncs Industries (2014). http://www.ipc.org/

D. Hillman, D. Adams, T. Pearson, B. Williams, B. Petrick, R. Wilcoxon, R. Collins, D. Bernard, J. Travis, E. Krastev, Proc. SMTAI 2011, 163–177 (2011)

P. Wild, D. Lorenz, T. Grözinger, A. Zimmermann, Microelectron. Reliab. 85, 163–175 (2018)

M.-S. Kang, Y.-J. Jeon, D.-S. Kim, Y.-E. Shin, Int. J. Precis. Eng. Manuf. 17(4), 445–452 (2016)

Y.-J. Jeon, S.-I. Son, D.-S. Kim, Y.-E. Shin, J. Korean Inst. Electr. Electron. Mater. Eng. 23(8), 611–616 (2010)

A. Youssef, I. Birner, H. Voelkel, J. Thierauf, R. Vodiunig, A. Middendorf, K.-D. Lang, in Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE), 2016 17th International Conference on, IEEE, pp. 1–6 (2016)

P. Tu, Y.C. Chan, J. Lai, IEEE Trans. Compon. Packag. Manuf. Technol. Part B 20(1), 87–93 (1997)

D.R. Banks, T.E. Burnette, Y. Cho, W.T. DeMarco, A.J. Mawer, in Proc. Surface Mount International, Surface Mount International San Jose, California, pp. 121–126 (1996)

D. Kim, K. Hubbard, B. Nandagopal, M. Hu, S. Teng, A. Nouri, in IPC APEX Conf. Proc., pp. S31–03 (2006)

J. Smetana, T. Sack, D. Love, C. Katzko, in IPC APEX Conf. Proc., pp. S28–02 (2011)

Y. Liu, J. Keck, E. Page, N.-C. Lee, in IPC APEX EXPO Conf. Proc., p. 19 (2014)

M. Rauer, A. Volkert, T. Scherck, S. Harter, M. Kaloudis, J. Fail, Anal. Prev. 14, 272–281 (2014)

P. Wild, T. Grozinger, D. Lorenz, A. Zimmermann, IEEE Trans. Reliab. 66(4), 1229–1237 (2017)

JIS Z 3198-7 Standard, Test Methods for Lead-Free Solders-Part 7: Methods for Shear Strength of Solder Joints on Chip Components, Japanese Standards Association (2009). https://www.jsa.or.jp/en/

K. Sweatman, T. Nishimura, K. Sugimoto, A. Kita, Controlling Voiding Mechanisms in the Reflow Soldering Process, in Proc. IPC APEX Expo (2016)

Z. Wang, H. Zhao, W. Lou, H. Li, L. Jin, in IEEE 12th International Conference on Electronic Packaging Technology and High Density Packaging (ICEPT-HDP), pp. 1–4 (2011)

Acknowledgements

This work was financially supported through a grant from Korea Institute of Industrial Technology, Republic of Korea.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Seo, W., Ko, YH., Kim, YH. et al. Void fraction of a Sn–Ag–Cu solder joint underneath a chip resistor and its effect on joint strength and thermomechanical reliability. J Mater Sci: Mater Electron 30, 15889–15896 (2019). https://doi.org/10.1007/s10854-019-01935-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-019-01935-4