Abstract

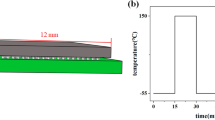

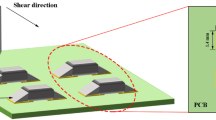

In this research, two different Sn3.0Ag0.5Cu solder bump joints with barrel shape and hourglass shape respectively were fabricated by controlling solder process, and evolution of intermetallic compounds (IMC) between different solder joint and Cu substrate under 4 × 103 A/cm2 current stressing at 60 °C were investigated. The results indicate that both the decrease of IMC layer thickness in the cathode and the increase of IMC layer thickness in the anode of the hourglass-shaped solder bump joint were obviously slower than that of barrel-shaped solder bump joint, and the formation of the voids at cathode interface was observed in the barrel-shaped solder bump joint after current stressing for 240 h. The mean-time-to-failure (MTTF) of solder joint with hourglass-shaped bump is efficiently improved compared to that with barrel-shaped bump. Compared to that of the solder joint with barrel-shaped bump, enhancement of MTTF of the solder joint with hourglass-shaped bump is attributed to relieve current crowding in entrance and outlet of electric current.

Similar content being viewed by others

References

R.R. Tummala, E.J. Rymaszewski, A.G. Klopfenstein, Microelectronics Packaging Handbook, 2nd edn. (International Thompson, New York, 1997), pp. 1–65

K.N. Tu, Recent advances on electromigration in very-large-scale-integration of interconnects. J. Appl. Phys. 94(9), 5451–5473 (2003)

K.M. Chen, Impact of packaging materials on reliability test for low-K wire bond-stacked flip chip CSP. J. Mater. Sci. Mater. Electron. 20, 484–489 (2009)

X. Liu, S. Haque et al., Three-dimensional flip-chip on flex packaging for power electronics applications. IEEE Trans. Adv. Packag. 24(1), 1–9 (2001)

C.Y. Tan, J.-G. Duh, Characterization of the effect of shape memory alloy on solder joint strength through modelling and testing. J. Electron. Mater. 38(12), 2496–2505 (2009)

S.P.V. Nadimpali, J.K. Spelt, Effect of geometry on the fracture behavior of lead free solder joints. Eng. Fract. Mech. 78(6), 1169–1181 (2011)

J.R. Black, IEEE Trans. Electron Devices 16, 338 (1969)

W.-C. Kuan, S.W. Liang, C. Chen, Effect of bump size on current density and temperature distributions in flip-chip solder joints. Microelectron. Reliab. 49(5), 544–550 (2009)

X. Liu, G.-Q. Lu, Effects of solder joint shape and height on thermal fatigue lifetime. IEEE Trans. Compon. Packag. Technol. 26(2), 455–465 (2003)

X.S. Liu, S. Haque, J. Wang, G.Q. Lu, in Packaging of Integrated Power Electronics Modules Using Flip-Chip Technology. Fifteenth Annual IEEE Applied Power Electronics Conference and Exposition, vol. 1 (2000), pp. 290–296

K.-N. Chiang, C.-A. Yuan, An overview of solder bump shape prediction algorithms with validations. IEEE Trans. Adv. Packag. 24(2), 158–162 (2001)

X.S. Liu, S.Y. Xu, G.Q. Lu, D.A. Dillard, Stacked solder bumping technology for improved solder joint reliability. Microelectron. Reliab. 41(12), 1979–1992 (2001)

D.J. Zhou, Z.C. Chen, K.L. Pan, Z.H. Wu, Modeling and predicting solder joint shapes of plastic ball grid array. J. Zhejiang Univ. 34(6), 637–641 (2000)

C.M. Chen, S.W. Chen, Electromigration effects upon the low-temperature Sn/Ni interfacial reactions. J. Mater. Res. 18(6), 1293–1296 (2003)

C.-Y. Yu, K.-J. Wang, J.-G. Duh, Interfacial reaction of Sn and Cu–xZn substrates after reflow and thermal aging. J. Electron. Mater. 39(2), 230–237 (2010)

X. Li, X. Yang, F. Li, in Effect of Isothermal Aging on Interfacial IMC Growth and Fracture Behavior of SnAgCu/Cu Soldered Joints. ICEPT-HDP (2008), pp. 1–5

K. Zeng, K.N. Tu, Six cases of reliability study of Pb-free solder joints in electronic packaging technology. Mater. Sci. Eng. R 38(2), 55–105 (2002)

Y.W. Chang, C. Chen, in Optimal Design of Passivation/UBM Openings for Reducing Current Crowding Effect Under Electromigration of Flip-Chip Solder Joint. EPTC (2009), pp. 818–822

Acknowledgments

The authors gratefully acknowledge the support received from National Science and Technology Major Project (2011ZX02607).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chen, P., Zhao, X., Wang, Y. et al. Enhancement of mean-time-to-failure of Sn3.0Ag0.5Cu solder bump joint under current stressing via controlling bump shape. J Mater Sci: Mater Electron 26, 1940–1949 (2015). https://doi.org/10.1007/s10854-014-2633-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-014-2633-4