Abstract

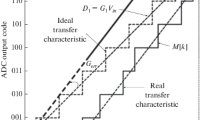

Measurement of integral non-linearity (INL) and differential non-linearity (DNL) of an A/D converter using the histogram method incurs large test time. This test time can be a significant percentage of the total test time, especially for high resolution and low sampling-speed A/D converters. This paper describes a test methodology for measuring the INL and DNL specifications of A/D converters by measuring a subset of the total set of code widths. This methodology is based on the fact that manufacturing variations in the electronic components of an A/D converter affect specific sets of codes in a similar manner. The proposed methodology measures code width parameters across such different sets of codes and estimates the A/D converter transfer function from the resulting information. A novel test generation methodology is presented for measuring the relevant code widths using a piecewise linear ramp that is designed to extract test information accurately from test data in minimal test time. The test procedure has been applied to different A/D converters and test time reduction of more than 75% has been achieved.

Similar content being viewed by others

References

Adamo F et al. (2001) FFT test of A/D converters to determine the integral nonlinearity. In: Proceedings of Instrumentation and Measurement Technology Conference, 710–714 May

Alegria F, Arpaia P, de Cruz Serra AM, Daponte P (2002) Performance analysis of an ADC histogram test using small triangular waves. IEEE Trans Instrum Meas 51(4):723–729, Aug

Blair J (1994) Histogram measurement of ADC nonlinearities using sine waves. IEEE Trans Instrum Meas 43(3):373–383, June

Burns M, Roberts GW (2001) An introduction to mixed-signal IC test and measurement. Oxford University Press, Oxford, pp 423–424

Carbone P, Petri D (1998) Noise sensitivity of ADC histogram test. IEEE Trans Instrum Meas 47(3):1001–1004

Capofreddi PD, Wooley BA (1997) The use of linear models in A/D converter testing. IEEE Trans Circuits Syst I Fundam Theory Appl 44(12):1105–1113, Dec

Cherubal S, Chatterjee A (2003) Optimal linearity testing of analog-to-digital converters using a linear model. IEEE Trans Circuits Syst I Fundam Theory Appl 50(3):317–327, Mar

Flores MGC, Negreiros M, Carro L, Susin AA (2004) INL and DNL estimation based on noise for ADC test. IEEE Trans Instrum Meas 53(5):1391–1395 Oct

Jin L, Parthasarathy K, Kuyel T, Chen D, Geiger RL (2003) Linearity testing of precision analog-to-digital converters using stationary non-linear inputs. In: Proc Intl Test Conf, Sept, pp 218–227

Ginetti B, Jespers P (1991) Reliability of code density test for high resolution ADCs. Electron Lett 27:2231–2233, Nov

Goyal S, et al. (2005) Test time reduction of successive approximation A/D converters using selective code measurement. In: Proc. Intl. Test Conf, Nov, pp 218–225

Kuyel T (1999) Linearity testing issues of analog to digital converters. In Proc. International Test Conference, Sept, pp 747–756

Max S (2001) IEEE Std 1241: Benefits and risks of ADC histogram testing. Proc. Instrum Meas Technol Conf 1:704–709

Maxim IC (2000) Application note 641, ADC and DAC glossary. http://www.maxim-ic.com/appnotes.cfm/appnote_number/641, Dec

Maxim IC (2003) Application note 2085, Histogram testing determines INL and DNL errors. http://www.maxim-ic.com/appnotes.cfm/appnote_number/2085, May

Martins RC, de Cruz Serra AM (1999) Automated ADC characterization using the histogram test stimulated by Gaussian noise. IEEE Trans Instrum Meas 48(2):471–474 Apr

Michaeli L, Michalko P, Saliga J (2005) ADC testing by decomposition of the error model. Meas Sci Rev 5(Sec. 1):39–42

Pei S, Chan S-P (1991) New approach to linearity testing of A/D converters. Intl J Electron 70(6):1049–1062, June

Razavi B (1995) Data conversion system design. Wiley-IEEE Press, New York, pp 143–147

Souders TM, G N Stenbakken (1990) A comprehensive approach for modeling and testing analog and mixed-signal devices. In: Proc. Intl. Test Conf, Sept, pp. 169–176

Wegener C, Kennedy MP (2004) Linear model-based testing of ADC nonlinearities. IEEE Trans Circuits Syst I Fundam Theory Appl 51(1):213–217 Jan

Acknowledgment

S. Goyal thanks the Data Conversion System Test Development group of National Semiconductor Corporation, Santa Clara for the providing the tester facility.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: V. Champac

Rights and permissions

About this article

Cite this article

Goyal, S., Chatterjee, A. Linearity Testing of A/D Converters Using Selective Code Measurement. J Electron Test 24, 567–576 (2008). https://doi.org/10.1007/s10836-008-5071-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-008-5071-5