Abstract

In this article, the electrical behavior of laterally grown novel short-channel III–V/Si heterostructure double gate triple material PiN tunneling graphene nanoribbon field effect transistor (DG-TM-PiN-TGNFET) has been studied based on their quantum mechanical effect (QME). Firstly, by varying the device process parameters of the novel TFET structure, the DC parameter responses viz. threshold voltage, electric field and surface potential are investigated. Further these responses are analyzed by considering the QME for better device performance. Two-dimensional numerical device simulator (SILVACO TCAD) tool is used for simulating the quantum and semi-classical models. The simulation work has been validated by extensive analytical modeling, that reflected in our accurate graphical representations. Finally, to investigate the QME effect in circuit level applications, an TFET inverter circuit has been designed and its DC performance viz. power dissipation and propagation delay analysis is performed.

Similar content being viewed by others

1 Introduction

In last two decades, the device scaling has encouraged a new paradigm of nanodevice modeling and fabrication. The conventional device structures of metal oxide field effect transistors (MOSFET) have been outplayed for many limitations viz. short channel effects (SCE), drain-induced barrier thinning (DIBT) issues, scattering, etc., due to which the subthreshold swing also got limited to 60 mV/decade [1,2,3,4,5].

With the advent of device engineering and inclusion of multi-gate metal contacts, the limited subthreshold swing (ss) results much better than earlier structures. But continuous device scaling also got restricted, when the power dissipation and heat generation comes into the picture.

A new device physics, i.e., quantum tunneling came into this research domain, which outplayed the SCE, DIBT and many other limitations at ease. The tunneling field effect transistors (TFET) with double gate becomes more encouraging solution to limited swing, and also it boosts its drive current (ION) [6,7,8]. There were several multi-gate TFET structures that faced detrimental effects, viz. short channel effects, drain-induced barrier thinning (DIBT) and quantum mechanical effects (QME) [9,10,11,12,13,14]. After a detailed study of recent literature survey on DC performance of modified TFET structures, graphene nanoribbon-lapped double gate triple metal transistor (DG-TM-PiN-TGNFET) has been established by R. Dutta et al. [15] and validated by analytical modeling. The graphene material is used as a ribbon to reduce the energy gap, by virtue of which a better tunneling window was obtained in the energy band diagram (EBD). Chien et al. investigated the dependency of short channel effects on semiconductor band gap in tunnel FETs in 2018 [16], where low band gap materials were used to improve the ON state current.

In addition to short channel effects, quantum mechanical effect (QME) also plays major role in short-channel tunnel FETs.

Especially when the channel length is scaled below 25 nm, the electrostatic control starts degrading rapidly. As the motion of carriers is largely influenced by its quantum confinement, therefore the carrier transport is altogether different in such TFET structures compared to the classical carrier transport mechanism.

2 Device structure and simulation methodology

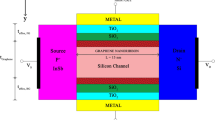

In this section, TCAD simulated structure of N-type III-V/Si heterostructure double gate triple-metal PiN tunneling TGNFET is shown in Fig. 1. In our established simulated device model [15] shown in Fig. 1, indium arsenide (InAs) III/V compound material is used in source for better tunneling at source–channel interface. Double gate is used as front gate and back gate, for better gate-source voltage control over short channel [17]. The channel length (L) is taken as 20 nm, which is intrinsic in nature for less doping. Since triple metal is used in our device model, total effective channel length (L) is shown as L = L1 + L2 + L3. Here three different metal materials are used with different work functions as ΦM1 = 4 eV and ΦM2 = 4.5 eV and ΦM3 = 4.8 eV, in order to achieve better ON state current compared to single or double metal contacts [18]. Doping concentration at source (NS) = 1020 cm−3, at drain (ND) = 1018 cm−3 and at intrinsic channel (Nch) = 1014 cm−3 are taken. The body thickness (tGNR) = 10 nm and dielectric (SiO2) thickness (toxf = toxb = 2 nm) are taken (Tables 1, 2).

The entire simulation work is performed in two-dimensional numerical device simulator. SILVACO TCAD device simulator is used for obtaining the simulation results incorporating semi-classical model and validated by recent work [19, 20]. Shockley–Read–Hall (SRH) model is used for recombination purpose for physical models. Field-dependent mobility (FLDMOB) model [21, 22] has been introduced to study velocity saturation under high electric field. For BTBT tunneling, the band gap narrowing (BGN) model is used and CONMOB for mobility degradation. In addition to this, Schrödinger’s quantum model is used to validate the analytical modeling results.

A three-dimensional schematic diagram of our proposed model is shown in Fig. 2 for better understanding of quantum mechanical effect across the channel and the ultra-thin graphene nanoribbon placement over short channel for III-V/Si heterostructure TFET. Since energy band gap plays major role on short channel effects in Tunnel FETs, lower band gap material, viz. InAs (0.35 eV) is used compared to higher band gap materials, viz. Si (1.12 eV) and Ge (0.8 eV).

2.1 DIBT analysis

The purpose of introducing the quantum mechanical effect (QME) is to assess the variation of electric field, surface potential distribution and drain-induced barrier thinning (DIBT) effect along x-axis of the channel. Figure 3 depicts the DIBT variation with QME was much less compared to the classical model.

2.2 Surface potential distribution analysis

In Fig. 4, the surface potential distribution is shown along x-axis of the device channel length using both quantum and semi-classical models. Wherein, it can very well be identified that the sharp raise of surface potential distribution in the inversion region occurs due to QME, compared to the semi-classical one. Raise in surface potential results in less electron charge and lower drain current.

2.3 Transfer characteristics analysis on varied gate oxide thickness, channel thickness and channel doping concentration

In Fig. 5a–c, the transfer characteristics analysis (ID vs VGS) using QME is performed based on varied device parameters, i.e., gate oxide thickness (toxf and toxb), channel thickness (tGNR) and channel doping concentration (Nch).

a Transfer characteristics of DG-TM-PiN-TGNFET using quantum model and semi-classical model w.r.t. the oxide thickness variation. b Transfer characteristics of DG-TM-PiN-TGNFET using quantum model and semi-classical model w.r.t. the channel thickness variation. c Transfer characteristics of DG-TM-PiN-TGNFET using quantum model and semi-classical model w.r.t. doping concentration variation

As the quantum effect is considered in our work, from Fig. 5a, b and c, we can see that the quantum confinement results in low drain current profile compared to the semi-classical model. From Fig. 5a, it can be observed that the best drain current (ION) is obtained at tox = 2 nm using semi-classical model, where the leakage current (IOFF) has been under control results less ambipolar conduction. In Fig. 5b, at channel thickness (tGNR) = 10 nm the best subthreshold slope is obtained. Besides this, the channel doping concentration (Nch) also plays pivotal role in determining best drive current as well as better switching (ION/IOFF) ratio. In Fig. 5c, at intrinsic channel doping of 1014 atoms/cm3, substantial drain current is received.

3 Proposed digital inverter operation

In this section, the schematic diagram of an equivalent circuit of digital inverter using DG-TM-PiN-TGNFET is portrayed in Fig. 6. The tunnel FET-based inverter comprises of PTFET forming the pull-up network (PUN) and NTFET forming the pull-down network (PDN). Generally, PTFETs have lower drive strength compared to NTFETs, which further provides asymmetric voltage transfer characteristics (VTC). Therefore, in this work the digital inverter has been realized using graphene nanoribbon-lapped TGNFET exhibits sharp VTC transition and better DC operations after a detailed survey of modified TFET inverter circuits [23,24,25].

3.1 Power dissipation analysis

The equivalent circuit representation of a typical TFET digital inverter with graphene nanoribbon can be analyzed in this mathematical representation. A LOW logic, i.e., logic 0 at the input of our proposed TGN PTFET acts as a resistor (RP) and the TGN NTFET acts as current source (IN).

The drain current equation of N-type TFET can be written as,

Here,

i.e., \(I_{{\text{N}}} = K_{{\text{N}}} \left( \frac{W}{L} \right)_{{\text{N}}} \exp \left( {\frac{{V_{{{\text{GS}}}} - \left( {V_{{{\text{th}}0}} - \lambda_{{{\text{DS}}}} V_{{{\text{DS}}}} + \Delta V_{{{\text{th}}, {\text{Q}}}} } \right)}}{{V_{{\text{T}}} }}} \right)\left( {1 - e^{{\frac{{V_{{{\text{DS}}}} }}{{V_{{\text{T}}} }}}} } \right)\).

i.e., \(I_{{\text{N}}} = K_{{\text{N}}} \left( \frac{W}{L} \right)_{{\text{N}}} \exp \left( {\frac{{V_{{{\text{GS}}}} }}{{V_{{\text{T}}} }}} \right)\exp \left( {\frac{{V_{{{\text{th}}0}} - \lambda_{{{\text{DS}}}} V_{{{\text{DS}}}} + \Delta V_{{{\text{th}}, \;Q}} }}{{V_{{\text{T}}} }}} \right)\left( {1 - e^{{\frac{{V_{{{\text{DS}}}} }}{{V_{{\text{T}}} }}}} } \right)\).

i.e., \(I_{{\text{N}}} = \beta \exp \left( {\frac{{V_{{{\text{GS}}}} }}{{V_{{\text{T}}} }}} \right)\left( {1 - e^{{\frac{{V_{{{\text{DS}}}} }}{{V_{{\text{T}}} }}}} } \right)\) where

Now, from the proposed TFET inverter circuit, the PTFET can be replaced by its equivalent resistor, whose resistance can be obtained by,

Which is nothing but

Therefore, the load capacitance (CL) can be obtained from the equivalent circuit,

Now integrating both the sides, we can get,

Since, T ˃˃ \(R_{{\text{P}}} C_{{\text{L}}}\) and \(e^{{ - \frac{T}{{R_{{\text{P}}} C_{{\text{L}}} }}}}\) → 0,

So, output high voltage VOH can be obtained as,

Finally, the power dissipation can be analyzed by the following equation,

3.2 Propagation delay analysis

To find out the propagation delay, KCL has been applied at the output node of equivalent circuit of our TFET inverter circuit.

Since, \(V_{{{\text{OH}}}} = V_{{{\text{DD}}}} - I_{{\text{N}}} R_{{\text{P}}}\).

i.e., \(C_{{\text{L}}} \frac{{{\text{d}}V_{{{\text{out}}}} }}{{d_{{\text{t}}} }} + I_{{\text{N}}} = \frac{\Delta V}{{R_{{\text{P}}} }}\)

Now, integrating the expression we can write,

i.e., \( - R_{{\text{P}}} C_{{\text{L}}} = \int\limits_{0}^{{V_{{{\text{DD}}}} - \Delta V}} {\frac{{{\text{d}}(V_{{{\text{DD}}}} - V_{{{\text{out}}}} - I_{{\text{N}}} R_{{\text{P}}} )}}{{V_{{{\text{DD}}}} - V_{{{\text{out}}}} - I_{{\text{N}}} R_{{\text{P}}} }}} = T_{{\text{R}}} \).

i.e., \(- R_{{\text{P }}} C_{{\text{L}}} \ln \frac{{ \left( {V_{{{\text{DD}} }} - I_{{\text{N}}} R_{{\text{P}}} + \Delta V} \right)}}{{V_{{{\text{DD}}}} - I_{{\text{N}}} R_{{\text{P}}} }} = T_{{\text{R}}}\)

where, \(T_{{\text{R}}} \) is the digital inverter propagation delay at subthreshold region.

4 Result and discussion

In earlier sections, lower band gap III–V material, i.e., InAs/Si-based heterostructure of proposed DG-TM-PiN-TGNFET has been designed with quantum effect by varying threshold voltage and surface potential along short channel. The detail transfer characteristics has been analyzed by varying device parameters, viz. oxide thickness, channel thickness and doping concentration with quantum effect. In this section, a novel digital TGNFET inverter circuit performance has been analyzed by semi-classical and quantum effects. For ultra-low power applications, the DC performance, i.e., power dissipation, propagation delay and power-delay product of our TGNFET inverter circuit have been taken into account in subthreshold regime.

4.1 Power dissipation analysis (with quantum and semi-classical model) on gate oxide thickness, channel thickness and channel doping variation

In this subsection, the power dissipation of proposed TFET inverter is shown in Fig. 7a–c. Figure 7a shows variation of gate oxide thickness (tox) and supply voltage (VDD) ranging between 1 and 0.5 V; the power dissipation can be measured. The power has been dissipated much less using quantum mechanical effect compared to semi-classical one. In this graphical representation, the straight lines and dotted lines denote semi-classical and quantum models, respectively.

a Power dissipation characteristics of DG-TM-PiN-TGNFET-based digital inverter circuit w.r.t. gate oxide thickness variation. b Power dissipation characteristics of DG-TM-PiN-TGNFET-based digital inverter circuit w.r.t. channel thickness variation. c Power dissipation characteristics of DG-TM-PiN-TGNFET-based digital inverter circuit w.r.t. channel doping variation

After solving the mathematics behind this power dissipation in Eq. 4.2, we can see that power dissipation increases with increase in gate oxide (tox) and channel thickness (tGNR) for TFET digital inverter circuit. In addition to this, the intrinsic channel doping concentration variation also determines the best selection of low power TFET inverter for circuit level applications. The average difference in percentage value of power dissipation between quantum and semi-classical models is almost 25–30% for a particular process parameter variation. Therefore, the inclusion of quantum mechanical effect provides better understanding of circuit level analysis of TFET digital inverter.

4.2 Propagation delay analysis (with quantum and semi-classical model) on gate oxide thickness, channel thickness and channel doping variation

From Fig. 8a, b and c, it can be very well understood that the propagation delay becomes much less using semi-classical model compared to quantum model, on variation of all device process parameters. From earlier transfer characteristics of DG-TM-PiN-TGNFET shown in Fig. 5a, b and c, it is evident that the quantum confinement of charge carriers in our proposed device produces much less drain current compared to semi-classical one. Therefore, the digital inverter operates much faster using semi-classical model.

a Propagation delay analysis of DG-TM-PiN-TGNFET-based digital inverter circuit w.r.t. gate oxide thickness variation. b Propagation delay analysis of DG-TM-PiN-TGNFET based digital inverter circuit w.r.t. channel thickness variation. c Propagation delay analysis of DG-TM-PiN-TGNFET-based digital inverter circuit w.r.t. channel doping variation

4.3 Power-delay product analysis (with quantum and semi-classical model) on gate oxide thickness, channel thickness and channel doping variation

The product of power (P) and delay (TR) of the inverter gives the PDP value. The power-delay product (PDP) is generally analyzed for optimizing all process parameters with minimum value of supply voltage that can be given to the proposed TFET digital inverter circuit. Taking the quantum mechanical effect into consideration, it can be studied that the PDP becomes much less using quantum confinement in charge carriers on all process parameter variation, compared to semi-classical one, shown in Fig. 9a, b and c.

a Power-delay product analysis of DG-TM-PiN-TGNFET-based digital inverter circuit w.r.t. gate oxide thickness variation. b Power-delay product analysis of DG-TM-PiN-TGNFET-based digital inverter circuit w.r.t. channel thickness variation. c Power-delay product analysis of DG-TM-PiN-TGNFET-based digital inverter circuit w.r.t. channel doping variation

However, the supply voltage (below 1 V) also plays significant role in determining best TFET inverter considering its suitable device parameters. Since with increase in supply voltage, the PDP of the inverter circuit rises; therefore, at 0.5 V of VDD, the minimum value of PDP is obtained. This minimum power-delay product can justify and validate the proposed TFET inverter circuit for low power applications.

5 Conclusion

In this article, the DC parameters of laterally grown novel short channel III–V/Si heterostructure DG-TM-PiN-TGNFET have been analytically modeled and an inverter has been analyzed in subthreshold regime. DC characteristics of the III–V/Si heterostructure DG-TM-PiN-TGNFET have been studied with respect to the quantum mechanical and classical effect in subthreshold regime for low-power digital applications.

It is quite evident that the derived models and simulation results are in good agreement for a wide variation of process parameters. Schrodinger model has been used in ATLAS simulation platform to validate the derived analytical model considering QME. Comprehensive analysis of the short channel III–V/Si heterostructure double gate triple material PiN tunneling graphene nanoribbon field effect transistor (DG-TM-PiN-TGNFET) gives a better view and understanding of DC characteristics of the device. At the end, the DC characteristics (i.e., power dissipation, propagation delay, power-delay product) of an inverter circuit has been taken under consideration to check the impact of QMEs on circuit performance.

Power dissipation of the proposed TFET inverter circuit is illustrated by considering semi-classical and quantum models, where the power has been dissipated much less using quantum mechanical effect compared to semi-classical one.

But propagation delay becomes much less using semi-classical model compared to quantum model for the proposed TFET structure making it suitable for high-speed applications due to high current driving capability. However, as per as the power-delay product analyses , the quantum confinement is able to provide less energy consumption, and it is an essential factor in case of optimizing the process parameters of the device. So, the proposed device can be alternatively used for low-power quantum computing applications.

References

Ionescu, A.M., Riel, H.: Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479(7373), 329–337 (2011)

Koswatta, S.O., Lundstrom, M.S., Nikonov, D.E.: Performance comparison between p-i-n tunneling transistors and conventional MOSFETs. IEEE Trans. Electron. Devices 56(3), 456–465 (2009)

Seabaugh, A.C., Zhang, Q.: Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98(12), 2095–2110 (2010)

Choi, W.Y., Park, B.-G., Lee, J.D., Liu, T.-J.K.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007)

Thomas, N., Philip Wong, H.S.: The end of Moore’s Law: a new beginning for information technology. IEEE J. Comput. Sci. Eng. 19(2), 41–50 (2017)

Dutta, R., Konar, S.C., Paitya, N.: Influence of gate and channel engineering on multigate tunnel FETs: a review. In: Maharatna, K., Kanjilal, M., Konar, S., Nandi, S., Das, K. (eds.) Computational advancement in communication circuits and systems. Lecture notes in electrical engineering, vol. 575. Springer, Heidelberg (2020)

Madan, J., Gupta, R.S., Chaujar, R.: Mathematical modeling insight of hetero gate dielectric-dual material gate-GAA-tunnel FET for VLSI/analog applications. Microsyst. Technol. 23(9), 4091–4098 (2017)

Bardon, M.G., Neves, H.P., Puers, R., Van Hoof, C.: Pseudo two- dimensional model for double-gate tunnel FETs considering the junctions depletion regions. IEEE Trans. Electron. Devices 57(4), 827–834 (2010)

Madan, J., Gupta, R.S., Chaujar, R.: Performance investigation of heterogeneous gate dielectric-gate metal engineered–gate all around-tunnel FET for RF applications. Microsyst Technol 23, 4081–4090 (2017)

Dutta, R., Paitya, N.: Electrical characteristics assessmenton heterojunction tunnel FET (HTFET) by optimizing various high-κ materials: HfO2/ZrO2. Int. J. Innov. Technol. Explor. Eng. 8(10), 393–396 (2019)

Verhulst, A.S., Soree, B., Leonelli, D., Vandenberghe, W.G., Groeseneken, G.: Modeling the single-gate, doublegate, and gate all-around tunnel field-effect transistor. J. Appl. Phys. 107(2), 024518 (2010)

Alper, C., Palestri, P., Lattanzio, L., Padilla, L. J., Ionescu, A.M.: Two dimensional quantum mechanical simulation of low dimensional tunneling devices. In: 2014 44th European solid state device research conference (ESSDERC), pp. 186–189 (2014)

Wu, J., Min, J., Taur, Y.: Short-channel effects in tunnel FETs. IEEE Trans. Electron Dev. 62(9), 3019–3024 (2015). https://doi.org/10.1109/ted.2015.2458977

Dutta, R., Paitya, N., Subash, T.D.: Electric field and surface potential analytical modeling of novel double gate triple material PiN tunneling graphene nano ribbon FET (DG-TM-PiN-TGNFET). Silicon (2020). https://doi.org/10.1007/s12633-020-00474-6

Chien, N.D., et al.: Dependence of short-channel effects on semiconductor bandgap in tunnel field-effect transistors. J Phys Conf Ser 1034, 012003 (2014)

Dutta, R., Subash, T.D., Paitya, N.: InAs/Si hetero-junction channel to enhance the performance of dg-tfet with graphene nanoribbon: an analytical model. Silicon (2020). https://doi.org/10.1007/s12633-020-00546-7

Vimala, P., Arun Samuel, T.S., Nirmal, D., Panda, A.K.: Performance enhancement of triple material double gate TFET with heterojunction and heterodielectric. Solid State Electron. Lett. 1, 64–72 (2019)

TCAD Atlas Manual, Silvaco, Inc., CA 95054, USA (2015)

Cappy, A., et al.: Comparative potential performance of Si, GaAs, GaInAs, InAs submicrometer-gate FET’s. IEEE Trans. Electron Devices ED27(11), 2158–2160 (1980)

Arora, N.D., Hauser, J.R., Roulston, D.J., et al.: Electron and hole mobilities in silicon as a function of concentration and temperature. IEEE Trans. Electron Devices 29(2), 292–295 (1982)

Fossum, J.G., Lee, D.S., et al.: A physical model for the dependence of carrier lifetime on doping density in nondegenerate silicon. Solid State Electron 25, 741–747 (1982)

Richter, S., Trellenkamp, S., Schäfer, A., Hartmann, J.M., Bourdelle, K., Zhao, Q.T., Mantl, S.: Improved tunnel-FET inverter performance with SiGe/Si heterostructure nanowire TFETs by reduction of ambipolarity. Solid State Electron. 108, 97–103 (2015). https://doi.org/10.1016/j.sse.2015.02.018

Richter, S., Trellenkamp, S., Schafer, A., Hartmann, J.M., Bourdelle, K.K., Zhao, Q.T., Mantl, S.: Tunnel-FET inverters for ultra-low power logic with supply voltage down to VDD = 0.2 V. In: 2014 15th international conference on ultimate integration on silicon (ULIS), 2014.

Kwon, D.W., Kim, H.W., Kim, J.H., Park, E., Lee, J., Kim, W.: Effects of localized body doping on switching characteristics of tunnel FET inverters with vertical structures. IEEE Trans. Electron Devices 64(4), 1799–1805 (2017)

Acknowledgement

This work was supported by All India Council for Technical Education (AICTE), Govt. of India, under Research Promotion Scheme through the Grant: 8-139/RIFD/RPS-NER/Policy-1/2018-19. Special acknowledgement also goes to Dr. Nitai Paitya for facilitating the authors with Nanoelectronics Lab, Sikkim Manipal Institute of Technology (SMIT)-Sikkim, India, for this research work.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Dutta, R., Subash, T.D. & Paitya, N. DC performance analysis of III–V/Si heterostructure double gate triple material PiN tunneling graphene nanoribbon FET circuits with quantum mechanical effects. J Comput Electron 20, 855–863 (2021). https://doi.org/10.1007/s10825-020-01649-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-020-01649-5