Abstract

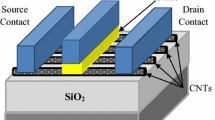

Ternary content-addressable memory (TCAM) is a type of associative memory used in many applications for high-speed data searching. We present herein a gate-all-around (GAA) carbon nanotube field-effect transistor (CNTFET)-based self-controlled TCAM cell design with a precharge-free match line. We compare the power–delay product (PDP) and static noise margin between the GAA-CNTFET-based traditional and proposed TCAM cell designs at the 11-nm technology node with a supply voltage of 0.8 V. The simulations are performed using the Virtuoso tool for different parameter values with the Stanford University GAA-CNTFET model. The simulation results show that, compared with the traditional design, the proposed design exhibits a significant reduction in power by 51.30%, delay by 17.16%, and PDP by 59.66% for a chiral vector of (20, 16, 0) with two channels. It is observed that the best chirality for the proposed design is (14, 20, 0) for a single channel, but (16, 16, 0) and (20, 16, 0) for a dual channel in terms of power, delay, stability, and PDP.

Similar content being viewed by others

References

Hoefflinger, B.: Chips 2020: A Guide to the Future of Nanoelectronics. Springer, New York (2012)

Chen, T.-C.: Overcoming research challenges for CMOS scaling: industry directions. In: 2006 8th International Conference on Solid-State and Integrated Circuit Technology Proceedings, pp. 4–7. IEEE (2006)

Sharifi, F., Moaiyeri, M.H., Navi, K., Bagherzadeh, N.: Quaternary full adder cells based on carbon nanotube FETs. J. Comput. Electron. 14(3), 762–772 (2015)

Chau, R., Datta, S., Doczy, M., Doyle, B., Jin, B., Kavalieros, J., Majumdar, A., Metz, M., Radosavljevic, M.: Benchmarking nanotechnology for high-performance and low-power logic transistor applications. IEEE Trans. Nanotechnol. 4(2), 153–158 (2005)

Avouris, P.: Electronics with carbon nanotubes. Phys. World 20(3), 40 (2007)

Pagiamtzis, K., Sheikholeslami, A.: Content-addressable memory (CAM) circuits and architectures: a tutorial and survey. IEEE J. Solid-State Circuits 41(3), 712–727 (2006)

Kumar, S., Noor, A., Kaushik, B.K., Kumar, B.: Design of ternary content addressable memory (TCAM) with 180 nm. In: 2011 International Conference on Devices and Communications (ICDeCom), pp. 1–5. IEEE (2011)

Chang, Y.-J., Tsai, K.-L., Tsai, H.-J.: Low leakage TCAM for IP lookup using two-side self-gating. IEEE Trans. Circuits Syst. I Regul. Pap. 60(6), 1478–1486 (2013)

Lin, S., Kim, Y.-B., Lombardi, F.: Design of a CNTFET-based SRAM cell by dual-chirality selection. IEEE Trans. Nanotechnol. 9(1), 30–37 (2010)

Kumar, G.S., Singh, A., Raj, B.: Design and analysis of a gate-all-around CNTFET-based SRAM cell. J. Comput. Electron. 17(1), 1–8 (2017)

Das, D., Roy, A., Rahaman, H.: Design of content addressable memory architecture using carbon nanotube field effect transistors. In: Rahaman, H., Chattopadhyay, S., Chattopadhyay, S. (eds.). Progress in VLSI Design and Test. Lecture Notes in Computer Science, vol 7373. pp. 233–242. Springer, Berlin, Heidelberg (2012)

Nepal, K.: Ternary content addressable memory cells designed using ambipolar carbon nanotube transistors. In: 2012 IEEE 10th International New Circuits and Systems Conference (NEWCAS), pp. 421–424. IEEE (2012)

Sinha, S.K., Chaudhury, S.: Comparative study of leakage power in CNTFET over MOSFET device. J. Semicond. 35(11), 114002 (2014)

Sethi, D., Kaur, M., Singh, G.: Design and performance analysis of a CNFET-based TCAM cell with dual-chirality selection. J. Comput. Electron. 16(1), 106–114 (2017)

Kittur, H.M., et al.: Precharge-free, low-power content-addressable memory. IEEE Trans. Very Large Scale Integr. VLSI Syst. 24(8), 2614–2621 (2016)

Mahendra, T.V., Mishra, S., Dandapat, A.: Self-controlled high-performance precharge-free content-addressable memory. IEEE Trans. Very Large Scale Integr. VLSI Syst. 25(8), 2388–2392 (2017)

Iijima, S.: Helical microtubules of graphitic carbon. Nature 354(6348), 56–58 (1991)

Raychowdhury, A., Roy, K.: Carbon nanotube electronics: design of high-performance and low-power digital circuits. IEEE Trans. Circuits Syst. I Regul. Pap. 54(11), 2391–2401 (2007)

Hazeghi, A., Krishnamohan, T., Wong, H.-S.P.: Schottky-barrier carbon nanotube field-effect transistor modeling. IEEE Trans. Electron Devices 54(3), 439–445 (2007)

Lee, C.-S., Pop, E., Franklin, A.D., Haensch, W., Wong, H.-S.P.: A compact virtual-source model for carbon nanotube FETs in the sub-10-nm regime—part I: intrinsic elements. IEEE Trans. Electron Devices 62(9), 3061–3069 (2015)

Lee, C.-S., Pop, E., Franklin, A.D., Haensch, W., Wong, H.-S.P.: A compact virtual-source model for carbon nanotube FETs in the sub-10-nm regime—part II: extrinsic elements, performance assessment, and design optimization. IEEE Trans. Electron Devices 62(9), 3070–3078 (2015)

Luo, J., Wei, L., Lee, C.-S., Franklin, A.D., Guan, X., Pop, E., Antoniadis, D.A., Wong, H.-S.P.: Compact model for carbon nanotube field-effect transistors including nonidealities and calibrated with experimental data down to 9-nm gate length. IEEE Trans. Electron Devices 60(6), 1834–1843 (2013)

Zhang, Z., Wang, S., Wang, Z., Ding, L., Pei, T., Zhudong, H., Liang, X., Chen, Q., Li, Y., Peng, L.-M.: Almost perfectly symmetric SWCNT-based CMOS devices and scaling. ACS Nano 3(11), 3781–3787 (2009)

d’Honincthun, H.C., Nguyen, H.-N., Galdin-Retailleau, S., Bournel, A., Dollfus, P., Bourgoin, J.P.: Influence of capacitive effects on the dynamic of a CNTFET by Monte Carlo method. Phys. E Low-Dimens. Syst. Nanostruct. 40(7), 2294–2298 (2008)

Seevinck, E., List, F.J., Lohstroh, J.: Static-noise margin analysis of MOS SRAM cells. IEEE J. Solid-State Circuits 22(5), 748–754 (1987)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Satyanarayana, S.V.V., Shailendra, S.R., Ramakrishnan, V.N. et al. Dual-chirality GAA-CNTFET-based SCPF-TCAM cell design for low power and high performance. J Comput Electron 18, 1045–1054 (2019). https://doi.org/10.1007/s10825-019-01362-y

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-019-01362-y