Abstract

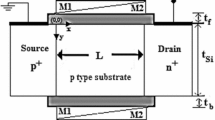

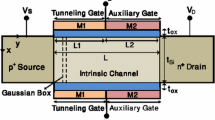

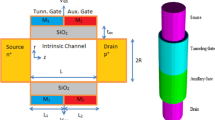

In this paper, a 2-D analytical model for the drain current of a dual material gate tunneling field-effect transistor is developed incorporating the effects of source and drain depletion regions. The model can forecast the effects of drain voltage, gate work function, oxide thickness, and silicon film thickness. The proposed model gives analytical expressions for the surface potential, electric field and the band to band generation rate which is numerically integrated to give the drain current. More importantly, our model accurately predicts the ambipolar current and the effects of drain voltage in the saturation region. A semi-empirical approach is used to model the transition from the linear to the saturation region, leading to an infinitely differentiable characteristics. The model is shown to be scalable down to a gate length of 50 nm. The model validation is carried out by a comparison with 2-D numerical simulations.

Similar content being viewed by others

References

Seabaugh, A.C., Zhang, Q.: Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98(12), 2095–2110 (2010)

Koswatta, S.O., Lundstrom, M.S., Nikonov, D.E.: Performance comparison between p-i-n tunneling transistors and conventional MOSFETs. IEEE Trans. Electron Devices 56(3), 456–465 (2009)

Toh, E.-H., Wang, G.H., Samudra, G., Yeo, Y.C.: Device physics and design of germanium tunneling field-effect transistor with source and drain engineering for low power and high performance applications. J. Appl. Phys. 103(10), 104504-1–104504-5 (2008)

Kumar, M.J., Janardhanan, S.: Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Devices 60(10), 3285–3290 (2013)

Saurabh, S., Kumar, M.J.: Estimation and compensation of process induced variations in nanoscale tunnel field effect transistors (TFETs) for improved reliability. IEEE Trans. Device Mater. Rel. 10(3), 390–395 (2010)

Ram, M.S., Abdi, D.B.: Single Grain boundary tunnel field effect transistors on recrystallized polycrystalline silicon: proposal and investigation. IEEE Electron Device Lett. 35(10), 989–991 (2014)

Appenzeller, J., Lin, Y.-M., Knoch, J., Avouris, P.: Band-to-band tunneling in carbon nanotube field-effect transistors. Phys. Rev. Lett. 93(19), 196805-1 (2004)

ITRS, Denver, CO, USA: International technology roadmap for semiconductors [Online]. http://www.itrs.net/ (2013)

Boucart, K., Ionescu, A.M.: Double-gate tunnel FET with high-\(k\) gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

Boucart, K., Ionescu, A.M.: A new definition of threshold voltage in tunnel FETs. Solid State Electron. 52(9), 1318–1323 (2008)

Saurabh, S., Kumar, M.J.: Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans. Electron Devices 58(2), 404–410 (2011)

Shih, C.-H., Chien, N.D.: Sub-10-nm tunnel field-effect transistor with graded Si/Ge heterojunction. IEEE Electron Device Lett. 32(11), 1498–1500 (2011)

Villalon, A., Royer, C.L., et al.: First demonstration of strained SiGe nanowires TFETs with ION beyond \(700 \mu \text{ A }/\mu \text{ m }\), Symposium on VLSI Tech., pp. 1–2. Honolulu, (2014)

Zhang, A., Mei, J., Zhang, L., He, H., He, J., Chan, M.: Numerical study on dual material gate nanowire tunnel field-effect transistor. In: Proceedings IEEE International Conference EDSSC, pp. 1–5 (2012)

Cui, N., Liang, R., Xu, J.: Heteromaterial gate tunnel field effect transistor with lateral energy band profile modulation. Appl. Phys. Lett. 98(14), 142105-1–142105-3 (2011)

Lou, H., Zhang, L., Zhu, Y., Lin, X., Yang, S., He, J., Chan, M.: A junctionless nanowire transistor with a dual-material gate. IEEE Trans. Electron Devices 59(7), 1829–1836 (2012)

Lee, M.J., Choi, W.Y.: Effects of device geometry on hetero-gate-dielectric tunneling field-effect transistors. IEEE Electron Device Lett. 33(10), 1459–1461 (2012)

Fan, M.-L., Hu, V.P., Chen, Y.-N., Su, P., Chuang, C.-T.: Analysis of single-trap-induced random telegraph noise and its interaction with work function variation for tunnel FET. IEEE Trans. Electron Devices 60(6), 2038–2044 (2013)

Vandenberghe, W.G., Verhulst, A.S., Groeseneken, G., Soree, B., Magnus, W.: Analytical model for tunnel field-effect transistors. In: Proceedings \(14^{{\rm th}}\) IEEE Mediterranean Electrotech. Conference, pp. 923–928 (2008)

Verhulst, A.S., Leoneli, D., Rooyackers, R., Groeseneken, G.: Drain voltage dependent analytical model of tunnel field-effect transistors. J. Appl. Phys. 110(2), 024510-1–024510-10 (2011)

Lee, M., Choi, W.: Analytical model of single-gate silicon-on-insulator tunneling field-effect transistors. Solid State Electron. 63(1), 110–114 (2011)

Wan, J., Royer, C.L., Zaslavsky, A., Cristoloveanu, S.: A tunneling field effect transistor model combining interband tunneling with channel transport. J. Appl. Phys. 110(10), 104503-1–104503-7 (2011)

Vishnoi, R., Kumar, M.J.: Compact analytical drain current model of gate-all-around nanowire tunneling FET. IEEE Trans. Electron Devices 61(7), 2599–2603 (2014)

Liu, L., Mohanta, D., Datta, S.: Scaling length theory of double-gate interband tunnel field-effect transistors. IEEE Trans. Electron Devices 59(4), 902–908 (2012)

Shen, C., Ong, S.-L., Heng, C.-H., Samudra, G., Yeo, Y.-C.: A variational approach to the two-dimensional nonlinear Poisson’s equation for the modeling of tunneling transistors. IEEE Electron Dev. Lett. 29(11), 1252–1255 (2008)

Vishnoi, R., Kumar, M.J.: Compact analytical model of dual material gate tunneling field effect transistor using interband tunneling and channel transport. IEEE Trans. Electron Devices 61(6), 1936–1942 (2014)

Vishnoi, R., Kumar, M.J.: A pseudo-2D analytical model of dual material gate all-around nanowire tunneling FET. IEEE Trans. Electron Devices 61(7), 2264–2270 (2014)

ATLAS Device Simulation Software, Silvaco Int., Santa Clara, CA, USA (2014)

Kane, E.O.: Zener tunneling in semiconductors. J. Phys. Chem. Solids 12(2), 181–188 (1960)

Young, K.K.: Short-channel effect in fully depleted SOI-MOSFETs. IEEE Trans. Electron Devices 40(10), 1812–1817 (1993)

Kamchouchi, H., Zaky, A.: A direct method for the edge capacitance of thick electrodes. J. Phys. D 8, 1365–1371 (1975)

Lin, S., Kuo, J.: Modeling the fringing electric field effect on the threshold voltage of FD SOI nMOS devices with the LDD/sidewall oxide spacer structure. IEEE Trans. Electron Devices 50(12), 2559–2564 (2003)

Kumar, M.J., Gupta, S.K., Venkataraman, V.: Compact modeling of parasitic internal fringe capacitance effects on the threshold voltage of high-k gate dielectric nanoscale SOI MOSFETs. IEEE Trans. Electron Devices 53(4), 706–711 (2006)

Lee, M.S.L., Tenbroek, B.N., Redman-White, W., Benson, J., Uren, M.J.: A physically based compact model of partially depleted SOI MOSFETs for analog circuit simulation. IEEE J. Solid State Circuits 36(1), 110–121 (2001)

Agarwal, P., Saraswat, G., Kumar, M.J.: Compact surface potential model for FD SOI MOSFET considering substrate depletion region. IEEE Trans. Electron Dev. 55(3), 789–795 (2008)

Sze, S.: Physics of Semiconductor Devices. Wiley, New York (1981)

Author information

Authors and Affiliations

Corresponding author

Appendix

Appendix

The coefficients \(\hbox {a}_{1}\) and \(\hbox {b}_{1}\) for the source depletion region (R1) are found by applying the boundary conditions as given in (16) and solving the resultant six linear equations in the six variables \(\hbox {a}_{\mathrm{i}}\) and \(\hbox {b}_{\mathrm{i}}\):

Here additional symbols \(\Delta \psi _{i,j}\), \(\Delta k_{ij}\) and \(\Sigma k_{ij}\) have been defined for compact representation of the coefficients \(\hbox {a}_{1}\) and \(\hbox {b}_{1}\):

Rights and permissions

About this article

Cite this article

Pandey, P., Vishnoi, R. & Kumar, M.J. A full-range dual material gate tunnel field effect transistor drain current model considering both source and drain depletion region band-to-band tunneling. J Comput Electron 14, 280–287 (2015). https://doi.org/10.1007/s10825-014-0649-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-014-0649-x