Abstract

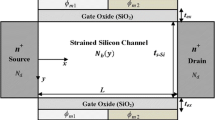

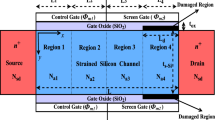

The present paper proposes the surface potential based two-dimensional (2D) analytical models of subthreshold current and subthreshold swing of nanoscale double-material-gate (DMG) strained-Si (s-Si) on Silicon-Germanium-on-Insulator (SGOI) MOSFETs. The surface potential expression has been directly taken from our previous reported work. The effect of various device parameters on subthreshold current and swing like Ge mole fraction, Si film thickness, gate-length ratio and various combinations of control/screen gate work-functions have been discussed. The validity of the present 2D model is verified by using ATLASTM, a 2D device simulator from Silvaco.

Similar content being viewed by others

References

International Technology Roadmap for Semiconductors (2011)

Moore, G.E.: Progress in digital integrated electronics. Int. Elec. Dev. Meet. 11–13 (1975)

Leong, M., Doris, B., Kedzierski, J., Rim, K., Yang, M.: Silicon device scaling to the sub-10-nm regime. Science 306, 2057–2060 (2004)

Kalna, K., Martinez, A., Svizhenko, A., Anantram, M.P., Barker, J.R., Asenov, A.: NEGF simulations of the effect of strain on scaled double gate nanoMOSFETs. J. Comput. Electron. 7, 288–292 (2008)

Fischetti, M.V.: Scaling MOSFETs to the limit: a physicists’s perspective. J. Compt. Electron. 2, 73–79 (2003)

Saxena, M., Haldar, S., Gupta, M., Gupta, R.S.: Design consideration for novel device architecture: hetero-material double-gate (HEM-DG) MOSFET with sub-100 nm gate length. Solid State Electronics 48, 1169–1174 (2004)

Long, W., Chin, K.K.: Dual Material Gate Field Effect Transistor (DMGFET). Tech. Dig.—Int. Electron Devices Meet., pp. 549–551 (1997)

Tiwari, P.K., Dubey, S., Singh, M., Jit, S.: A two-dimensional analytical model for threshold voltage of short-channel triple-material double-gate metal-oxide-semiconductor field-effect transistors. J. Applied Physics 108, 074508 (2010)

Polishchuk, I., Ranade, P., King, T.J., Hu, C.: Dual work function metal gate CMOS technology using metal inter-diffusion. IEEE Electron Device Lett. 22, 444–446 (2001)

Guillaumot, B.: 75 nm damascene metal gate and high-k integration for advanced CMOS devices. In: Proc. IEDM, pp. 355–358 (2002)

Liu, J., Wen, H.C., Lu, J.P., Kwong, D.L.: Dual-work-function metal gates by full silicidation of poly-Si with Co–Nibi-layers. IEEE Electron Device Letters 26, 228–230 (2005)

Zhang, Z., Song, S.C., Huffman, C., Hussain, M.M., Barnett, J., Moumen, N., Alshareef, H.N., Majhi, P., Sim, J.H., Bae, S.H., Lee, B.H.: Integration of dual metal gate CMOS on high-k dielectric sutilizing a metal wet etch process. Electro-chem. Solid-State Lett. 8, 271–274 (2005)

Kumar, M., Dubey, S., Tiwari, P.K., Jit, S.: An analytical model of threshold voltage for short-channel double-material-gate (DMG) strained-Si (s-Si) on silicon-germanium (SGOI) MOSFETs. J. Compt. Electron. (2012). doi:10.1007/s10825-012-0429-4

Yeh, P.C., Fossum, J.G.: Physical subthreshold MOSFET modeling applied to viable design of deep-submicrometer fully depleted SO1 low-voltage CMOS technology. IEEE Trans. Electron Devices 42, 1605–1613 (1995)

Hamid, H.A.E., Guitart, J.R., Iñíguez, B.: Two-dimensional analytical threshold voltage and subthreshold swing models of undoped symmetric double-gate MOSFETs. IEEE Trans. Electron Devices 54, 1402–1408 (2007)

ATLAS manual: Silvaco Int. Santa Clara (2008)

Mizuno, T., Takagi, S., Sugiyama, N., Koga, J., Tezuka, T., et al.: High performance strained-Si p-MOSFETs on SiGe-on-insulator substrates fabricated by SIMOX technology. In: Proc. IEDM, pp. 134–135 (1999)

Wasler, J., Hoyt, J.L., Gibbons, J.F.: NMOS and PMOS transistors fabricated in strained silicon/relaxed silico-germanium structures. In: Proc. IEDM, pp. 1000–1002 (1992)

Numata, T., Irisawa, T., Tezuka, T., Koga, J., et al.: Performance enhancement of partially and fully depleted strained-SOI MOSFETs. IEEE Trans. Electron Devices 53, 1030–1038 (2006)

Dey, A., Chakravorty, A., Dasgupta, N., Dasgupta, A.: Analytical model of subthreshold current and slope for asymmetric 4-T and 3-T double-gate MOSFETs. IEEE Trans. Electron Devices 55, 3442–3449 (2008)

Chen, Q., Agrawal, B., Meindl, J.D.: A comprehensive analytical subthreshold swing (S) model for double-gate MOSFETs. IEEE Trans. Electron Devices 49, 1086–1090 (2002)

Hamid, H.A.E., Guitart, J.R., Iniguez, B.: Two-dimensional analytical threshold voltage and subthreshold swing models of undoped symmetric double-gate MOSFETs. IEEE Trans. Electron Devices 54, 1402–1408 (2007)

Jankovic, N.D., Armstrong, G.A.: Comparative analysis of the DC performance of DG MOSFETs on highly-doped and near-intrinsic silicon layers. Microelectron. J. 35, 647–653 (2004)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kumar, M., Dubey, S., Tiwari, P.K. et al. Two-dimensional modeling of subthreshold current and subthreshold swing of double-material-gate (DMG) strained-Si (s-Si) on SGOI MOSFETs. J Comput Electron 12, 275–280 (2013). https://doi.org/10.1007/s10825-013-0442-2

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-013-0442-2