Abstract

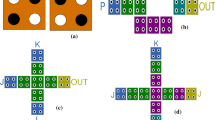

The difficulties which the CMOS technology is facing at the nano scale has led to the investigation of quantum-dot cellular automata (QCA) nanotechnology and reversible logic as an alternative to conventional CMOS technology. In this paper, these two paradigms have been combined. Firstly, a new 3 × 3 reversible gate, SSG-QCA, which is universal and multifunctional in nature, is proposed and implemented in QCA using conventional 3-input majority voter based logic. By using the concept of explicit interaction of cells, the proposed gate is further optimized and then used to design an ultra-efficient 1-bit full adder in QCA. The universal nature has been verified by designing all the logic gates from the proposed SSG-QCA gate whereas the multifunctional nature is verified by implementing all the 13 standard Boolean functions. The proposed 3 × 3 gate and adder designs are then extensively compared with the existing literature and it is observed that the proposed designs are ultra-efficient in terms of both area and cost in QCA technology. In addition to this energy dissipation analysis for different scenarios is also done on all the designs and it is observed that the proposed designs dissipate minimum energy thereby making them suitable for ultra-low power designs.

Similar content being viewed by others

References

Lent, C.S., Tougaw, P.D., Porod, W., Bernstein, G.H.: Quantum cellular automata. Nanotechnology. 4, 49–57 (1993)

Smith, C.G.: Computation without current. Science. 284, 274–274 (1999)

Bilal, B., Ahmed, S., Kakkar, V.: Modular adder designs using optimal reversible and fault tolerant gates in field-coupled QCA nanocomputing. Int. J. Theor. Phys. 57, 1356–1375 (2018)

Bilal, B., Ahmed, S., Kakkar, V.: An insight into beyond CMOS next generation computing using quantum-dot cellular automata nanotechnology. Int. J. Eng. Manag. Econ. 8, 25–37 (2018)

Tougaw, P.D., Lent, C.S.: Logical devices implemented using quantum cellular automata. J. Appl. Phys. 75, 1818–1825 (1994)

Bilal, B., Ahmed, S., Kakkar, V.: Quantum dot cellular automata: a new paradigm for digital design. International Journal of Nanoelectronics & Materials. 11, (2018)

Landauer, R.: Irreversibility and heat generation in the computing process. IBM J. Res. Dev. 5, 183–191 (1961)

Bennett, C.H.: Logical reversibility of computation. IBM J. Res. Dev. 17, 525–532 (1973)

Bilal, B., Ahmed, S., Kakkar, V.: QCA based efficient Toffoli gate design and implementation for nanotechnology applications. Int. J. Eng. Technol. 9, 84–92 (2017)

Bilal, B., Ahmed, S., Kakkar, V.: Optimal realization of universality of peres gate using explicit interaction of cells in quantum dot cellular automata nanotechnology. International Journal of Intelligent Systems and Applications. 9, 75–84 (2017)

Ahmad, F.: An optimal design of QCA based 2n: 1/1: 2n multiplexer/demultiplexer and its efficient digital logic realization. Microprocess. Microsyst. 56, 64–75 (2018)

Ahmad, F., Ahmed, S., Kakkar, V., Bhat, G.M., Bahar, A.N., Wani, S.: Modular Design of Ultra-Efficient Reversible Full Adder-Subtractor in QCA with power dissipation analysis. Int. J. Theor. Phys. 57, 2863–2880 (2018)

Bilal, B., Ahmed, S., Kakkar, V.: Multifunction reversbile logic gate: logic synthesis and design implementation in QCA. In: 2017 International Conference on Computing, Communication and Automation (ICCCA), pp. 1385–1390 (2017)

Ahmad, F., Bhat, G.M., Khademolhosseini, H., Azimi, S., Angizi, S., Navi, K.: Towards single layer quantum-dot cellular automata adders based on explicit interaction of cells. Journal of Computational Science. 16, 8–15 (2016)

Srivastava, S., Asthana, A., Bhanja, S., Sarkar, S.: QCAPro-an error-power estimation tool for QCA circuit design. In: 2011 IEEE International Symposium of Circuits and Systems (ISCAS), pp. 2377–2380 (2011)

Timler, J., Lent, C.S.: Power gain and dissipation in quantum-dot cellular automata. J. Appl. Phys. 91, 823–831 (2002)

Srivastava, S., Sarkar, S., Bhanja, S.: Estimation of upper bound of power dissipation in QCA circuits. IEEE Trans. Nanotechnol. 8, 116–127 (2009)

Liu, W., Srivastava, S., Lu, L., O'Neill, M., Swartzlander, E.E.: Are QCA cryptographic circuits resistant to power analysis attack? IEEE Trans. Nanotechnol. 11, 1239–1251 (2012)

Thapliyal, H., Ranganathan, N.: Conservative QCA gate (CQCA) for designing concurrently testable molecular QCA circuits. In: 2009 22nd International Conference on VLSI Design, pp. 511–516 (2009)

Thapliyal, H., Ranganathan, N., Kotiyal, S.: Design of testable reversible sequential circuits. IEEE Transactions on Very Large scale Integration (vlsi) systems. 21, 1201–1209 (2013)

Fredkin, E., Toffoli, T.: Conservative logic. Int. J. Theor. Phys. 21, 219–253 (1982)

Sen, B., Saran, D., Saha, M., Sikdar, B.K.: Synthesis of reversible universal logic around QCA with online testability. In: 2011 International Symposium on Electronic System Design, pp. 236–241 (2011)

Roohi, A., Zand, R., Angizi, S., Demara, R.F.: A parity-preserving reversible QCA gate with self-checking cascadable resiliency. IEEE Trans. Emerg. Top. Comput. 2016,

Sen, B., Dutta, M., Goswami, M., Sikdar, B.K.: Modular design of testable reversible ALU by QCA multiplexer with increase in programmability. Microelectron. J. 45, 1522–1532 (2014)

Sasamal, T.N., Singh, A.K., Mohan, A.: Design of cost-efficient qca reversible circuits via clock-zone-based crossover. Int. J. Theor. Phys. 57, 3127–3140 (2018)

X. Ma, J. Huang, C. Metra, and F. Lombardi, "Reversible and testable circuits for molecular QCA design," in Emerging Nanotechnologies, ed: Springer, (2008), pp. 157–202

Sen, B., Dutta, M., Some, S., Sikdar, B.K.: Realizing reversible computing in QCA framework resulting in efficient design of testable ALU. ACM Journal on Emerging Technologies in Computing Systems (JETC). 11, 30 (2014)

Khezeli, M.R., Moaiyeri, M.H., Jalali, A.: Analysis of crosstalk effects for multiwalled carbon nanotube bundle interconnects in ternary logic and comparison with cu interconnects. IEEE Trans. Nanotechnol. 16, 107–117 (2017)

Taherkhani, E., Moaiyeri, M.H., Angizi, S.: Design of an ultra-efficient reversible full adder-subtractor in quantum-dot cellular automata. Optik. 142, 557–563 (2017)

Funding

This research was funded by TEQIP-III (A Government of India Project Assisted by the World Bank) under CRS with sanction no.: 1-5736612144.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Bhat, S.M., Ahmed, S. Design of Ultra-Efficient Reversible Gate Based 1-bit Full Adder in QCA with Power Dissipation Analysis. Int J Theor Phys 58, 4042–4063 (2019). https://doi.org/10.1007/s10773-019-04271-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10773-019-04271-9