Abstract

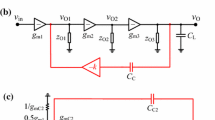

Hybrid cascode feedforward compensation (HCFC) is an effective technique to stabilize nano-scale three-stage amplifiers driving ultra-large load capacitors. It divides the compensation capacitance and shares it between two high-speed local feedback loops embedded within the amplifier core. In this article, a systematic approach to analyze the transfer function and to evaluate the pole expressions of nano-scale HCFC amplifiers is presented. For the first time, the equivalent output impedance is successfully modeled to approximate the complicated transfer function of the HCFC amplifier without the need for lengthy pencil-and-paper calculations. An HCFC amplifier is designed and simulated in 90-nm CMOS technology, to verify the effectiveness of the new analytic approach. The simulated transfer function of the amplifier is almost identical to a calculated transfer function derived based on the new model.

Similar content being viewed by others

References

Carusone, T. C., Johns, D. A., & Martin, K. W. (2011). Analog integrated circuit design. Hoboken: Wiley.

Leung, K. N., & Mok, P. K. T. (2001). Analysis of multistage amplifier-frequency compensation. IEEE Transactions on Circuits and Systems I, 48(8), 1041–1056.

Mesri, A., Javidan, J., & Pirbazari, M. M. (2015). High gain two-stage amplifier with positive capacitive feedback compensation. IET Circuits, Devices and Systems, 9(3), 181–190.

Bult, K., & Geelen, G. J. G. M. (1990). A fast-settling CMOS opamp for SC circuits with 90 dB DC gain. IEEE Journal of Solid-Slate Circuits, 25(6), 1379–1384.

Aminzadeh, H. (2017). Evaluation of the pole expressions of nano-scale multistage amplifiers based on equivalent output impedance. International Journal of Electronics and Communications, 72, 243–251.

Razavi, B. (2001). Design of analog CMOS integrated circuits. New York: McGraw-Hill.

Eschauzier, R. G. H., & Huijsing, J. H. (1995). Frequency compensation techniques for low-power operational amplifiers. Boston, MA: Kluwer.

Ahuja, B. K. (1983). An improved frequency compensation technique for CMOS operational amplifiers. IEEE Journal of Solid-State Circuits, 18(6), 629–633.

Leung, K. N., Mok, P. K. T., Ki, W. H., & Sin, J. K. O. (2000). Three-stage large capacitive load amplifier with damping-factor-control frequency compensation. IEEE Journal of Solid-State Circuits, 35(2), 221–230.

Lee, H., & Mok, P. K. T. (2003). Active-feedback frequency compensation technique for low power multistage amplifiers. IEEE Journal of Solid-State Circuits, 38(3), 511–520.

Fan, X., Mishra, C., & Sinencio, E. S. (2005). Single Miller capacitor frequency compensation technique for low-power multistage amplifiers. IEEE Journal of Solid-State Circuits, 40(3), 584–592.

Peng, X., & Sansen, W. (2005). Transconductance with capacitances feedback compensation for multistage amplifiers. IEEE Journal of Solid-State Circuits, 40, 1514–1520.

Aminzadeh, H., Danaie, M., & Lotfi, R. (2008). Design of high-speed two-stage cascode compensated operational amplifiers based on settling time and open-loop parameters. Integration, the VLSI, 41(2), 183–192.

Aminzadeh, H. (2011). Three-stage nested-Miller-compensated operational amplifiers: Analysis, design, and optimization based on settling time. International Journal of Circuit Theory and Applications, 39(6), 573–587.

Chong, S. S., & Chan, P. K. (2012). Cross feedforward cascode compensation for low-power three-stage amplifier with large capacitive load. IEEE Journal of Solid-State Circuits, 47(9), 2227–2234.

Aminzadeh, H., Rakhshanizadeh, E., & Emamjomeh, H. (2014). Hybrid cascode compensation with feedforward stage for high-speed area-efficient three-stage CMOS amplifiers. Analog Integrated Circuits and Signal Processing, 78(1), 253–256.

Aminzadeh, H., & Banihashemi, M. (2014). Miller compensation: optimal design for operational amplifiers with a required settling time. Circuits, Systems and Signal Processing, 33(9), 2675–2694.

Yan, Z., Mak, P. I., & Martins, R. P. (2011). Two-stage operational amplifiers: Power-and-area-efficient frequency compensation for driving a wide range of capacitive load. IEEE Circuits and Systems Magazine, 11(1), 26–42.

Yan, Z., Mak, P. I., Law, M. K., & Martins, R. P. (2012). Ultra-area-efficient three-stage amplifier using current buffer Miller compensation and parallel compensation. IET Electronics Letters, 48, 624–626.

Yan, Z., Mak, P. I., Law, M. K., & Martins, R. P. (2013). A 0.016-mm2 144-µW three-stage amplifier capable of driving 1-to-15 nF capacitive load with > 0.95-MHz GBW. IEEE Journal of Solid-State Circuits, 48, 527–540.

Tan, M., & Ki, W. H. (2015). A cascode Miller-compensated three-stage amplifier with local impedance attenuation for optimized complex-pole control. IEEE Journal of Solid-State Circuits, 50(2), 440–449.

Aminzadeh, H., & Dashti, A. (2015). Hybrid cascode compensation with current amplifiers for nano-scale three-stage amplifiers driving heavy capacitive loads. Analog Integrated Circuits and Signal Processing, 83, 331–341.

Qin, C., Zhang, L., Zhou, C., Zhang, L., Wang, Y., & Yu, Z. (2017). Dual AC boosting compensation scheme for multistage amplifiers. IEEE Transactions on Circuits and Systems I: Express Briefs, 64(8), 882–886.

Luchetta, A., Manetti, S., & Reatti, A. (2001). SAPWIN-a symbolic simulator as a support in electrical engineering education. IEEE Transaction on Education, 44(2), 213.

Rutenbar, R., Gielen, G., & Antao, B. (2009). ISAAC: A symbolic simulator for analog integrated circuits. Computer-Aided Design of Analog Integrated Circuits and Systems, 24(6), 276–286.

Shokouhifar, M., & Jalali, A. (2017). Simplified symbolic transfer function factorization using combined artificial bee colony and simulated annealing. Applied Soft Computing, 55, 436–451.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Aminzadeh, H. Analysis of multistage amplifiers with hybrid cascode feedforward compensation using a modified model for load impedance. Analog Integr Circ Sig Process 95, 271–282 (2018). https://doi.org/10.1007/s10470-018-1179-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-018-1179-4