Abstract

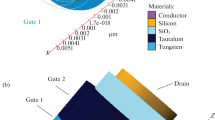

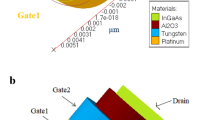

In this work, drain current ID for 3 nm gate length of triple material (TM) double surrounding gate (DSG) inversion mode (IM) and junctionless (JL) Si nanotube (SiNT) MOSFET has been studied and simulation results are reported using Silvaco ATLAS 3D TCAD. In this device we consider the Non Equilibrium Green’s Function (NEGF) approach and self-consistent solution of Poisson’s equation with Schrodinger’s equation. The channel region is lightly doped in case of IM SiNT MOSFET. The effect of TM Gate Engineering for SiNT channel radius 1.5 nm and gate oxide (SiO2) thickness of 0.8 nm on ID, has been studied. Also comparison of results has been done between IM TM DSG and JL TM DSG SiNT. For a reasonable comparison between Junctionless and Inversion Mode SiNT, in Junctionless SiNT, doping concentration is optimized for two concerns (i) to get the same threshold voltage (VTH) as IM SiNT and (ii) to get the same ION current as IM SiNT MOSFET. This results in 103 times smaller IOFF in both matching VTH and ION optimized device as compared to IM SiNT MOSFET. It was found that TM Gate Engineering reduces drain induced barrier lowering (DIBL) in JL SiNT. JL SiNT MOSFET has a smaller DIBL ~ 61.02 mV/V, almost an ideal SS ~ 60 mV/dec and higher ION/IOFF ratio ~ 2.63 × 109 as compared to available CGAA literature device results.

Similar content being viewed by others

References

Padmanaban B, Ramesh R, Nirmal D, Sathiyamoorthy S (2015) Numerical modeling of triple material gate stack gate all-around (TMGSGAA) MOSFET considering quantum mechanical effects. Superlattices Microstruct 82:40–54

Baidya A, Baishya S, Lenk TR (2017) Impact of thin high-k dielectrics and gate metals on RF characteristics of 3D double gate junctionless transistor. Mater Sci Semicond Process 71:413–420

Baruah RK, Paily RP (2014) A dual-material gate junctionless transistor with high-k spacer for enhanced analog performance. IEEE Trans Electron Devices 61:123–128

Boukortt N, Hadri B, Patane S, Caddemi A, Crupi G (2017) Investigation on TG n-FinFET parameters by varying channel doping concentration and gate length. Silicon 9:885–893

Colinge JP, Kranti A, Yan R, Lee CW, Ferain I, Yu R, Akhavan ND, Razavi P (2011) Junctionless nanowire transistor (JNT): properties and design guidelines. Solid State Electron 65:33–37

Das UK, Bardon MG, Jang D, Eneman G, Schuddinck P, Yakimets D, Raghavan P, Groeseneken G (2017) Limitations on lateral nanowire scaling beyond 7nm node. IEEE Electron Device Lett 38:9–11

Das UK, Eneman G, Velampati RSR, Chauhan YS, Jinesh KB, Bhattacharyya TK (2018) Consideration of UFET architecture for the 5 nm node and beyond logic transistor. J Electron Devices Soc 6:1129–1135

Guin S, Sil M, Malik A (2017) Comparison of logic performance of CMOS circuits implemented with junctionless and inversion-mode FinFETs. IEEE Trans Electron Dev 64:953–959

Jena B, Pradhan KP, Sahu PK, Dash D, Mishra GP, Mohapatra SK (2015a) Investigation on cylindrical gate all around (GAA) to nanowire MOSFET for circuit application. Electronics Energ 28:637–643

Jena B, Pradhan KP, Dash D, Mishra GP, Sahu PK, Mohapatra SK (2015b) Performance analysis of undoped cylindrical gate all around (GAA) MOSFET at subthreshold regime. Adv Nat Sci Nanosci Nanotechnol 6:035010

Kai H, Xiaolei W, Hong Y, Wenwu W (2015) Electric dipole formation at high-k dielectric/SiO2 interface. J Semicond 36:036004–036013

Kasturi P, Saxena M, Gupta M, Gupta RS (2008) Dual material double-layer gate stack son mosfet: a novel architecture for enhanced analog performance—part I: impact of gate metal workfunction engineering. IEEE Trans Electron Devices 55:372–381

Kita K, Toriumi A (2009) Origin of electric dipoles formed at high-k/SiO2 interface. Appl Phys Lett 94:132902–132903

Kundu A, Dasgupta A, Das R, Chakraborty S, Dutta A, Sarkar CK (2016) Influence of underlap on gate stack DG-MOSFET for analytical study of analog/RF performance. Superlattices Microstruct 94:60–73

Lee CW, Ferain I, Afzalian A, Yan R, Akhavan ND, Razavi P, Colinge JP (2010) Performance estimation of junctionless multigate transistors. Solid State Electron 54:97–103

Lema FA, Wang X, Amoroso SM, Riddet C, Cheng B, Shifren L, Aitken R, Sinha S, Yeric G, Asenov A (2014) Performance and variability of doped multithreshold FinFETs for 10-nm CMOS. IEEE Trans Electron Devices 61:3372–3378

Liao YB, Chiang MH, Damrongplasit N, Hsu WC, Liu TJK (2014) Design of gate-all-around silicon MOSFETs for 6-T SRAM area efficiency and yield. IEEE Trans Electron Devices 61:2371–2377

Lime F, Moldovan O, Iñiguez B (2014) A compact explicit model for long-channel gate-all-around junctionless MOSFETs. Part I: DC characteristics. IEEE Trans Electron Devices 61:3036–3041

Mohankumar N, Syamal B, Sarkar CK (2010) Influence of channel and gate engineering on the analog and RF performance of DG MOSFETs. IEEE Trans Electron Devices 57:820–826

Moldovan O, Lime F, Iniguez B (2014) A compact explicit model for long-channel gate-all-around junctionless MOSFETs. Part-II: total charges and intrinsic capacitance characteristics. IEEE Trans Electron Devices 61:3042–3046

Moon D, Choi SJ, Duarte JP, Choi YK (2013) Investigation of silicon nanowire gate-all-around junctionless transistor built on a bulk substrate. IEEE Transaction Electron Devices 60:1355–1360

Nagy D, Indalecio G, Loureiro AJG, Elmessary MA, Kalna K, Seoane N (2018) FinFET versus gate-all-around nanowire FET: performance, scaling and variability. IEEE J Electron Devices Soc 6:332–340

Pott V, Moselund KE, Bouvet D, Michielis LD, Ionescu AM (2008) Fabrication and characterization of gate-all-around silicon nanowires on bulk silicon. IEEE Trans Nanotechnol 7:733–744

Pouydebasque A, Denorme S, Loubet N, Wacquez R, Bustos J, Leverd F, Deloffre E, Barnola S, Dutartre D, Coronel P, Skotnicki T (2008) High-Performance High-K/Metal Planar Self-Aligned Gate-All-Around CMOS Devices. IEEE Trans Nanotechnol 7:551–557

Pratap Y, Kumar M, Kabra S, Haldar S, Gupta RS, Gupta M (2017) Analytical modeling of gate-all-around junctionless transistor based biosensor for detection of neural biomolecule species. J Comput Electrons 17:288–296

Razavi P, Fagas G (2013) Electrical performance of III-V gate-all-around nanowire transistors. Appl Phys Lett 103:063506

Rewari S, Nath V, Haldar S, Deswal SS, Gupta RS (2017) Novel design to improve band to band tunnelling and gate induced drain leakages (GIDL) in cylindrical gate all around (GAA) MOSFET. Springer Microsyst Technol 25:1537–1546

Robertson J, Falabretti B (2006) Band offsets of high-k gate oxides on III-V semiconductors. J Appl Phys 100:014111–014118

Sahay S, Kumar MJ (2016) Controlling L-BTBT and volume depletion in nanowire JLFETs using core-shell architecture. IEEE Trans Electron Device 63:3790–3794

Sahay S, Kumar MJ (2017) Symmetric operation in an extended back gate JLFET for scaling to the 5-nm regime considering quantum confinements. IEEE Trans Electron Devices 64:21–27

Sahay S, Kumar MJ (2017) Spacer design guidelines for nanowire fets from gate-induced drain leakage perspective. IEEE Trans Electron Devices 64:3007–3015

Sanjay BP, Vohra A (2020) Dual material gate engineering to reduce DIBL in cylindrical GateAll around Si nanowire MOSFET for 7-nm gate length. Semiconductors 54:1490–1495

Sharma RK, Gupta R, Gupta M, Gupta RS (2009) Dual Material Double-Gate SOI n-MOSFET: Gate Misalignment Analysis. IEEE Trans Electron Devices 56:1284–1291

Silvaco T-CAD Version: ATLAS 5.19.20.R, 2020

Su CJ, Tsai T, Liou YL, Lin ZM, Lin HC, Chao TS (2011) Gate-All-Around Junctionless Transistors With Heavily Doped Polysilicon Nanowire Channels. IEEE Electron Device Lett 32:521–523

Tayal S, Nandi A (2018) Optimization of gate-stack in junctionless Si-nanotube FET for analog/RF applications. Mater Sci Semicond Process 80:63–67

Tekleab D (2014) Device Performance of silicon nanotube MOSFETS field effect transistor. IEEE Electron Device Lett 35:506–508

Wong H, Iwai H (2006) On the scaling issues and high-k dielectric replacement of ultrathin gate dielectrics for nanoscale MOS transistors. Microelectron Eng 83:1867–1904

Zhang X, Connelly D, Zheng P, Takeuchi H, Hytha M, Mears RJ, Liu TJK (2016) Analysis of 7/8-nm bulk-Si FinFET technologies for 6T-SRAM scaling. IEEE Trans Electron Devices 63:1502–1507

Zheng P, Liao YB, Damrongplasit N, Chiang MH, Liu TJK (2014) Variation-aware comparative study of 10-nm GAA versus FinFET 6-T SRAM performance and yield. IEEE Trans Electron Devices 61:3949–3954

Acknowledgements

One of the authors (Sanjay) acknowledges the financial support in the form of SRF from University Grants Commission (UGC), New Delhi, India during the course of this work.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of Interest

The authors declare that they have no conflicts of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sanjay, Prasad, B. & Vohra, A. Effect of 3 nm gate length scaling in junctionless double surrounding gate SiNT MOSFET by using triple material gate engineering. Microsyst Technol 27, 3869–3874 (2021). https://doi.org/10.1007/s00542-020-05182-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-020-05182-0