Abstract

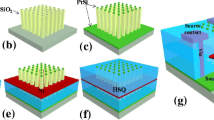

Over the years, semiconductor nanowires have been extensively researched due to their electrical properties for implementation of nano-to-microscale field-effect transistors (FETs). In order to implement a nanowire integrated device, well-aligned arrays of silicon nanowire are necessary for scalable and repeatable mass production. Although there has been much research on various fabrication processes to implement arrayed silicon-nanowires, few studies on channel conduction mechanism and theoretical modeling have been conducted on top-down fabricated silicon nanowires. In this paper, a comparative study on electrical characteristics of (100)- and (111)-silicon nanowire using a quantitative current model is presented for high-performance silicon-nanowire devices. Compared to silicon nanowire using (100)-silicon, one of the advantages of using (111)-silicon is that it can control the height and width of silicon nanowire through a sequential deep-silicon-etching process. According to the operation mechanism of the silicon-nanowire FET, the height of the silicon nanowire needs to be minimized to achieve high on/off-current ratio and low power consumption at off-state. Using (111)-silicon, it is possible to define height and width independently, which can result in higher performance characteristics.

Similar content being viewed by others

References

An S, Lee J, Kim Y, Kim T, Jin D, Min H, Chung H, Kim S (2010) 47.2: 2.8 inch WQVGA flexible AMOLED using high performance low temperature polysilicon TFT on plastic substrates. In: SID symposium digest of technical papers, vol. 41, no. 1, pp. 706–709. Blackwell Publishing Ltd

Barwicz T, Klein L, Koester SJ, Hamann H (2010) Silicon nanowire piezoresistance: impact of surface crystallographic orientation. Appl Phys Lett 97(2):023110

Colinge J-P (2004) Silicon-on-insulator technology: materials to VLSI. Springer Science & Business Media, New York

Duarte JP, Choi S, Moon D, Choi Y (2011) Simple analytical bulk current model for long-channel double-gate junctionless transistors. IEEE Electron Device Lett 32:704–706

Fu Y, Cai X, Wu H, Lv Z, Hou S, Peng M, Yu S, Zou D (2012) Fiber supercapacitors utilizing pen ink for flexible/wearable energy storage. Adv Mater 24(42):5713–5718

Gaidarzhy A, Zolfagharkhani G, Badzey RL, Mohanty P (2005) Evidence for quantized displacement in macroscopic nanomechanical oscillators. Phys Rev Lett 94:030402

Garnett E, Yang P (2008) Silicon nanowire radial p–n junction solar cells. J Am Chem Soc 130(29):9224–9225

Georgiev VP, Mirza MM, Dochioiu A, Adamu-Lema F, Amoroso SM, Towie E, Riddet C, MacLaren DA, Asenov A, Paul DJ (2017) Experimental and simulation study of silicon nanowire transistors using heavily doped channels. IEEE Trans Nanotechnol 16(5):727–735

He R, Yang P (2006) Giant piezoresistance effect in silicon nanowires. Nat Nanotechnol 1:42–46

Koumela A, Mercier D, Dupre C, Jourdan G, Marcoux C, Ollier E, Purcell ST, Duraffourg L (2011) Piezoresistance of top-down suspended Si nanowires. Nanotechnology 20(39):395701

Lee S (2017) Top–down fabrication of silicon-nanowire arrays for large-scale integration on a flexible substrate for achieving high-resolution neural microelectrodes. Microsyst Technol 23:491–498

Lee KN, Jung SW, Shin KS, Kim WH, Lee MH, Seong WK (2008) Fabrication of suspended silicon nanowire arrays. Small 4(5):642–648

Oproglidis TA, Karatsori TA, Barraud S, Ghibaudo G, Dimitriadis CA (2017) Leakage current conduction in metal gate junctionless nanowire transistors. Solid State Electron 131:20–23

Pratap Y, Kumar M, Kabra S, Haldar S, Gupta RS, Gupta M (2017) Analytical modeling of gate-all-around junctionless transistor based biosensors for detection of neutral biomolecule species. J Comput Electron 17(1):1–9

Shahrjerdi D, Bedell S (2012) Extremely flexible nanoscale ultrathin body silicon integrated circuits on plastic. Nano Lett 13(1):315–320

Trevisoli RD, Doria RT, de Souza M, Das S, Ferain I, Pavanello MA (2012) Surface-potential-based drain current analytical model for triple-gate junctionless nanowire transistors. IEEE Trans Electron Devices 59:3510–3518

Weber WM, Mikolajick T (2017) Silicon and germanium nanowire electronics: physics of conventional and unconventional transistors. Rep Prog Phys 80:066502

Woo J, Choi J, Choi Y (2013) Analytical threshold voltage model of junctionless double-gate MOSFETs with localized charges. IEEE Trans Electron Devices 60:2951–2955

Zhong Z, Qian F, Wang D, Lieber CM (2003) Synthesis of p-type gallium nitride nanowires for electronic and photonic nanodevices. Nano Lett 3(3):343–346

Acknowledgement

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIP; Ministry of Science, ICT & Future Planning) (No. NRF-2017R1C1B5017561).

Author information

Authors and Affiliations

Corresponding author

Electronic supplementary material

Below is the link to the electronic supplementary material.

Rights and permissions

About this article

Cite this article

Choi, Y.I., Lee, S. Comparative study on drain current conduction mechanisms of (100)- and (111)-silicon nanowire using a quantitative current model. Microsyst Technol 25, 2059–2066 (2019). https://doi.org/10.1007/s00542-018-3898-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-018-3898-y