Abstract

This paper presents, ant colony optimization based hybrid algorithm for selective harmonic elimination in single phase seven level multilevel inverter with reduced switches. For high power and high voltage applications, multilevel structure with selective harmonic elimination (SHE) modulation scheme is used. The output voltage of multilevel inverter contains fundamental component along with harmonics. SHE technique aims to solve non-linear transcendental equations maintaining the fundamental harmonic component to its desired value and to eliminate lower order odd harmonics. Many optimization algorithms have been implemented to solve this problem. But these algorithms are complicated and time consuming. The Newton–Raphson algorithm is also very convergent for solving these non-linear equations. The main disadvantage of this method is, it requires strong initial guess. To overcome these drawbacks, hybrid optimization algorithm is used in this paper. This algorithm is performed in two stages, during first stage ant colony optimization has been run and in second stage the solutions obtained from ACO is used as a initial guess for Newton–Raphson algorithm which confirms the exact converged solution. Thus the drawback of Newton’s method i.e. requirement of good initial guess is overcomed by proposed hybrid algorithm. The MATLAB/SlMULINK software is used for comprehensive simulation of seven-level inverter. Experimental results validate the simulated results.

Similar content being viewed by others

1 Introduction

For high power medium-voltage industrial applications, multilevel inverters are the best solution. In multilevel inverter as the level of inverter increases, output voltage waveform becomes more sinusoidal. Also it contains less harmonic distortion, and thereby reducing the filter size. The main inverter topologies are neutral point clamped (NPC), flying capacitor (FC), and cascaded H-bridge (CHB) (Rodrigues et al. 2002; Kouro et al. 2010). At present, the operating range for voltage and power is given by 0.3–13.8 kV and 0.3 KVA to 32 MVA (Rodriguez et al. 2007). Every inverter topology is having its own advantages and disadvantages. For high voltage applications usually cascaded H-bridge (CHB) is preferred with modular structure (Meshram and Borghate 2015). It requires separate DC-sources when the level increases. In the flying capacitor (FC) topology, capacitor balancing is the major problem. For proper balancing of the capacitor, high switching frequency is used which leads to high switching losses. Secondly in this topology, if the levels are increased, the number of flying capacitors also increases. For medium voltage applications, neutral point clamped (NPC) is used. But, the problem associated with NPC is voltage imbalance of DC-link capacitors, and numbers of clamping diodes (Franquelo et al. 2008). To overcome the issues related to the conventional topologies, new inverter topology is introduced with reduced switches (Banaei and Salary 2010).

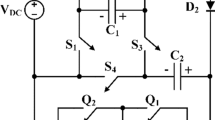

2 Reduced switch topology

In the conventional single phase cascaded multilevel inverter the number of switches required is given by

where ‘k’ is number of switches required and ‘l’ is number of levels in multilevel inverter. In suggested reduced switch topology, the number of switches in the single phase multilevel inverter is given by

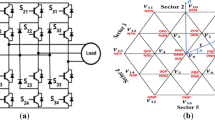

Figure 1 shows final configuration of seven level multilevel inverter with reduced switch connected to the cascaded basic unit which reverse alternate waveform to get positive, zero and negative levels. In this, extra clamping diodes or voltage balancing capacitors are not required. Also the number of output voltage levels is adjustable. The switching losses can be overcome by turning ON and OFF switching devices only once per cycle. For 0 < t < (T/2), switches Sa, Sb are ON together and positive half of output voltage waveform Vout is generated. For (T/2) < t < T, switches, Sc Sd are ON and negative half of output voltage waveform − Vout is produced. In suggested topology, the output phase voltage is given by

where ‘l’ is number of levels and ‘s’ is number of DC sources required. In the conventional cascaded multilevel inverter, for the same number of output phase voltage, the number of DC voltage source required is same. Figure 2 shows the comparison of number of switches required in conventional cascaded multilevel inverter with number of switches in suggested topology. It is clear from Fig. 2 that the suggested topology needs fewer switches for realizing ‘l’ level voltages for output. This point reduces the installation area and the number of the gate driver.

For example, to generate of single phase output voltage for seven levels (l = 7), proposed topology needs 10 switches and conventional cascaded H-bridge multilevel inverter requires 12 switches.

Different modulation schemes are applied for multilevel inverter. Broadly depending upon switching frequency, modulation schemes are classified, i.e. high switching frequency and low switching frequency. High switching frequency schemes uses space vector pulse width modulation (SVPWM) and sinusoidal pulse width modulation (SPWM) where semiconductor switches performs many commutations per cycle of output voltage waveform. Low switching frequency schemes uses selective harmonic elimination (SHE), synchronous optimal pulse width modulation (SOP) and space vector control (SVC) (Edpuganti and Rathore 2015) where semiconductor switches perform one or two commutations per cycle of output voltage waveform. The main advantage of low switching frequency scheme is minimum switching losses, smaller filtering component requirement and no harmonic interference, which makes this technique more suitable for high voltage applications (Sirisukprasert 1999; Dahidha et al. 2015).

3 Selective harmonic elimination

The staircase output voltage waveform of single phase seven level multilevel inverter is shown in Fig. 3.

The Fourier series expansion of this output waveform of the can be easily expressed as follows:

where ‘s’ is the number of H-bridges connected in series for each phase and ‘k’ is the order of harmonic components. Desired fundamental peak voltage V1 can be obtained if the switching angles are calculated such that the dominant lower order harmonic voltages are zero (Fei et al. 2009). It can be achieved by selecting one switching angle for calculation of fundamental voltage and remaining switching angles for elimination of certain lower order harmonics. From Eq. (4), the expression for fundamental voltage is given by

The main objective of SHE method is to eliminate the certain lower order harmonics such as fifth harmonic, seventh harmonic, ninth harmonic and so on. The triplen harmonics are not considered, as they will be automatically eliminated in three-phase applications. Whereas higher order harmonics are removed with the proper selection of filter. For eliminating the lower order harmonics and to maintain desired fundamental component, the three nonlinear equations with three angles are provided as

Modulation index (m) shows the relation between the fundamental voltage and the maximum obtainable voltage. It is the ratio of the fundamental voltage (V1) to the maximum obtainable voltage. When all switching angles are equal to zero, then the maximum fundamental voltage can be obtained i.e. V1max = 4sVdc/π.

Total harmonic distortion (THD) is given by

Solution of non-linear transcendental equations is a major concern in SHE method. To get solution of these equations various deterministic methods are applied so far such as resultant theory, symmetric polynomials (Chiasson et al. 2003), homotopy algorithm (Aghdam et al. 2007) and Newton algorithm (Kumar et al. 2008). These algorithms are time consuming having some advantages and disadvantages. Hence it requires optimization algorithms for getting solution. These algorithms such as particle swarm optimization (PSO), bee algorithm (BA), genetic algorithm (GA), ant colony optimization, etc., which can find optimum solution in the search space are also implemented. (Taghizadeh and Tarafdar Hagh 2010; Kavousi et al. 2012; Baskaran et al. 2012; Sundareswaran et al. 2007). The Newton–Raphson algorithm is very convergent for solving non-linear equations. The main disadvantage of Newton method is, it requires strong initial guess. Also it can give solution for certain modulation indices where solution exists. To overcome these drawbacks, hybrid optimization algorithm is used in this paper. Hybrid algorithm utilizes optimized switching angles obtained from Ant colony optimization as an initial guess in Newton–Raphson method to get exact solution. The paper is organised as follows. Reduced switch topology is explained in Sect. 2. Section 3 explains selective harmonic elimination method. Section 4 presents implementation of hybrid algorithm. Simulation results are discussed in Sect. 5. Experimental results are given in Sect. 6. And conclusion in Sect. 7.

4 Hybrid optimization algorithm

\( f = \mathop {\hbox{min} }\limits_{\alpha i} \left\{ {\left( {100\frac{{V_{1}^{*} - V_{1} }}{{V_{1}^{*} }}} \right)^{4} } \right\} + \sum\nolimits_{s = 2}^{S} {\frac{1}{{h_{s} }}\left( {50\frac{{V_{hs} }}{{V_{1} }}} \right)^{2} } \) to solve the nonlinear equation for achieving optimized switching angles, hybrid algorithm based on ACO and Newton method is written in MATLAB. The flowchart for hybrid algorithm is shown in Fig. 4. The objective function with limitations are shown as

where \( V_{1}^{ * } \) is the desired fundamental components, S is the number of switching angles, and hs is the order of sth harmonic at the output of multilevel inverter. In this section, switching angles are obtained such that low-order odd harmonics (fifth and seventh) are eliminated and the magnitude of the fundamental harmonic reaches to its desirable value.

The hybrid optimization algorithm is performed in two stages. In first stage, ACO is run and the solution obtained from ACO algorithm is used as a initial guess for Newton–Raphson algorithm in second stage. Basically ACO is a stochastic combinatorial, population based optimization approach. This algorithm is a distributed algorithm includes ants as a cooperating artificial agents. The ants generally cooperate among themselves and get the optimum solution for the problem. The blind ants move randomly in search of food by selecting the shortest or optimized path, and it deposits pheromone trails on the edges. While the follower ant can detect the pheromone laid by first ant and follow the same path with high probability. More ants following the same trail path is the collective behaviour of all ants. The probability of selecting the same path increases with the number of ants that previously selected the same path. The ACO algorithm can be implemented with following steps. Table 1 shows ACO parameters values required for implementation of hybrid algorithm.

Step I

While (termination not satisfied)

-

create ant’s population,

-

find solutions.

Step II

Transition probability

where τ is quantity of pheromone and d is heuristic distance

Step III

Pheromone update

where Q is a constant and Lk is the tour length of the kth ant.

Step IV

where T is the tour done at time t by ant k, L is the length

Step V

Pheromone decay

where ρ is evaporation constant and is assumed 0 < ρ < 1.

Step VI

Apply stopping criteria.

5 Simulation results

Simulation of a single phase 7-level multilevel inverter with reduced switch topology is carried out in MATLAB/Simulink environment. Table 2 indicates the specifications used for simulation for the proposed system.

The DC input for three H-bridges of single phase 7-level inverter is 100 V. The proposed hybrid algorithm is used to calculate the optimized switching angles Different solution sets are obtained for switching angles with different modulation indices as shown in Table 3. Out of these solution sets only one solution is feasible for modulation index m = 0.8 where angles obtained are α1 = 14.32°, α2 = 28.64°, α3 = 41.25°. This solution set not only provides optimized switching angles but it will again reduce the lower order harmonics i.e. 5th and 7th harmonic and total harmonic distortion (THD). These angles are plotted against modulation index (m) as shown in Fig. 5. As Newton–Raphson method converges very fast, the convergence of switching angles is shown in Fig. 6. Output voltage of single phase 7-level inverter is shown in Figs. 7 and 8 shows the FFT analysis. Figures 9 and 10 Variation of objective function with iterations and variation of objective function with modulation index. Figure 11 shows the graph of THD with modulation index. Whereas Fig. 12 shows the variation of harmonics (%), THD with modulation index. Figure 13 shows the variation of each ant after 25th iteration. Figure 14 shows the 3-D graph of objective function. It is clear that objective function has minimum value with the optimized values of switching angles. From simulation results it is clear that fifth harmonic and seventh harmonic are found to be very less i.e. h5 = 0.64% and h7 = 0.95% and also total harmonic distortion is also less, i.e. THD = 4.66% which is according to IEEE 519 standards.

6 Experimental results

Hardware implementation of single phase 7 level inverter using SHE system is done by comparing reference wave (sine wave) generated by HEF40106B IC with three constant values of switching angles. Figures 15, 16 and 17 shows the hardware results of gate pulses generated for switching angles α1 = 14.32°, α2 = 28.64°, α3 = 41.25°. Figure 18 shows the experimental result of single phase seven level inverter. For selective harmonic elimination the switching angles should be chosen so correctly that it will satisfy the required fundamental voltage and reduce lower order harmonic and THD.

7 Conclusion

Simulation of Multilevel Inverter for single phase 7-level inverter using hybrid algorithm in MATLAB/Simulink is presented as a systematic design approach. The results shows that the lower order harmonics i.e. 5th and 7th are reduced greatly and also they are within range of 1%. The THD contents are 4.66% which is as per IEEE 519 standard.

References

Aghdam M, Fathi S, Gharehpetian G (2007) Elimination of harmonics in a multi-level inverter with unequal DC sources using homotopy algorithm. In: Proceedinsg of the IEEE international symposium on industrial electronics, pp 578–583

Banaei MR, Salary E (2010) New multilevel inverter with reduction of switches and gate driver. In: ICEE 2010, pp 11–13

Baskaran J, Thamizharasan S, Rajtilak R (2012) GA based optimization and critical evaluation SHE methods for three level inverters. Int J Soft Comput Eng (IJSCE) 2(3):321–326 (ISSN: 2231-2307)

Chiasson JN, Tolbert LM, McKenzie KJ, Du Z (2003) Control of a multilevel converter using resultant theory. IEEE Trans Control Syst Technol II(3):345–354

Dahidha MSA, Konstantinou G, Agelidis VG (2015) A review of multilevel selective harmonic elimination PWM: formulations, solving algorithms, implementation and applications. IEEE Trans Power Electron 30(8):4091–4106

Edpuganti A, Rathore A (2015) A survey of low switching frequency modulation techniques for medium-voltage multilevel converters. IEEE Trans Ind Electron Soc 5(5):4212–4228

Fei W, Ruan X, Wu B (2009) A generalized formulation of quarter-wave symmetry SHE-PWM problems for multilevel inverters. IEEE Trans Power Electron 24:1758–1766

Franquelo LG, Rodriguez J, Leon JI, Kouro S, Portillo R, Prats MAM (2008) The age of multilevel converters arrives. IEEE Ind Electron Mag 2(2):28–39

Kavousi A, Vahidi B, Salehi R, Kazem M, Farokhnia BN, Fathi SH (2012) Application of the bee algorithm for selective harmonic elimination strategy in multilevel inverters. IEEE Trans Power Electron 27(4):1689–1696

Kouro S, Malinowski M, Gopakumar K, Pou J, Franquelo LG, Wu B, Rodriguez J, Perez MA, Leon JI (2010) Recent advances and industrial applications of multilevel converters. IEEE Trans Ind Electron 57(8):2553–2580

Kumar J, Das B, Agarwal P (2008) Selective harmonic elimination technique for a multilevel inverter. In: NPSC 2008, IIT Bombay, pp 608–613

Meshram PM, Borghate VB (2015) A simplified nearest level control (NLC) voltage balancing method for modular multilevel converter (MMC). IEEE Trans Power Electron 30(I):450–462

Rodrigues J, Lai J, Feng FZ (2002) Multilevel inverters: a survey of topologies controls and applications. IEEE Trans Ind Electron 49(4):724–738

Rodriguez J, Bernet S, Wu B, Pontt JO, Kouro S (2007) Multilevel voltage-source-converter topologies for industrial medium-voltage drives. IEEE Trans Ind Electron 54(6):2930–2945

Sirisukprasert S (1999) Optimized harmonic stepped-waveform for multilevel inverter. M.Sc. thesis, Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University (Virginia Tech)

Sundareswaran K, Jayant K, Shanavas TN (2007) Inverter harmonic elimination through a colony of continuously exploring ants. IEEE Trans Ind Electron 54(5):2558–2565

Taghizadeh H, Tarafdar Hagh M (2010) Harmonic elimination of cascade multilevel inverters with nonequal DC sources using particle swarm optimization. IEEE Trans Ind Electron 57(11):3678–3684

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Patil, S.D., Kadwane, S.G. Hybrid optimization algorithm applied for selective harmonic elimination in multilevel inverter with reduced switch topology. Microsyst Technol 24, 3409–3415 (2018). https://doi.org/10.1007/s00542-018-3720-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-018-3720-x