Abstract

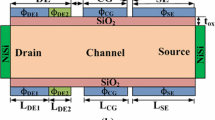

This article presents a new device configuration to enhance current drivability and suppress negative conduction (ambipolar conduction) with improved RF characteristics of physically doped TFET. Here, we used a new approach to get excellent electrical characteristics of hetero-dielectric short gate source electrode TFET (HD-SG SE-TFET) by depositing a metal electrode of 5.93 eV work function over the heavily doped source (P+) region. Deposition of metal electrode induces the plasma (thin layer) of holes under the Si/HfO\(_{2}\) interface due to work function difference of metal and semiconductor. Plasma layer of holes is advantageous to increase abruptness as well as decrease the tunneling barrier at source/channel junction for attaining higher tunneling rate of charge carriers (i.e., electrons), which turns into 86.66 times higher ON-state current compared with the conventional physically doped TFET (C-TFET). Along with metal electrode deposition, gate electrode is under-lapped for inducing asymmetrical concentration of charge carriers in the channel region, which is helpful for widening the tunneling barrier width at the drain/channel interface. Consequently, HD-SG SE-TFET shows suppression of ambipolar behavior with reduction in gate-to-drain capacitance which is beneficial for improvement in RF performance. Furthermore, the effectiveness of hetero-gate dielectric concept has been used for improving the RF performance. Furthermore, reliability of C-TFET and proposed structures has been confirmed in term of linearity.

Similar content being viewed by others

References

S.O. Koswatta, M.S. Lundstrom, D.E. Nikonov, Performance comparison between p-i-n tunneling transistors and conventional MOSFETs. IEEE Trans. Electron Devices 56(3), 456–465 (2007)

J.-P. Colinge, FinFETs and Other Multi-gate Transistors (Springer, New York, 2008)

P.F. Wang, K. Hilsenbeck, T. Nirschl, M. Oswald, C. Stepper, M. Weis, D.S. Landsiedel, W. Hansch, Complementary tunneling transistor for low power application. Solid state Electron 48(2), 2281–2286 (2004)

A.M. Ionescu, H. Riel, Tunnel field-effect transistors as energy efficient electronic switches. Nature 479(7373), 329–337 (2011)

K. Boucart, A.M. Ionescu, Silicon nanowire tunnelling field-effect transistors. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

S. Agarwal, G. Klimeck, M. Luisier, Leakage-reduction design concepts for low-power vertical tunneling field-effect transistors. IEEE Electron Device Lett. 31(6), 621–623 (2010)

S. Saurabh, M.J. Kumar, Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans. Electron Devices 58(2), 404–410 (2010)

A. Hraziia, C. Andrei, A. Vladimirescu, A. Amara, C. Anghel, An analysis on the ambipolar current in Si double-gate tunnel FETs. Solid State Electron 70, 67–72 (2012)

D.B. Abdi, M.J. Kumar, Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. IEEE J. Electron Devices Soc. 2(6), 187–190 (2014)

B. Rawat, R. Paily, Analysis of graphene tunnel field-effect transistors for analog/RF applications. IEEE Trans. Electron Devices 62(8), 2663–2669 (2015)

S. Ghosh, K. Koley, C.K. Sarkar, Impact of the lateral straggle on the analog and RF perforamcne of TFET. Microelectron Reliab. 55(2), 326–331 (2015)

S. Banerjee, W. Richardson, J. Coleman, A. Chatterjee, A new threeterminal tunnel device. IEEE Electron Devices Lett. 8(8), 347–349 (1987)

T. Baba, Proposal for surface tunnel transistors. Jpn. J. Appl. Phys. Lett. 31(4B), 455–457 (1992)

S. Ahish, D. Sharma, Y.B. Nithin Kumar, M.H. Vasantha, Performance enhancement of novel InAs/Si hetero double-gate tunnel FET using Gaussian doping. IEEE Trans. Electron Devices 63(1), 288–295 (2016)

A.N. Hanna, H.M. Hossain, M.M. Hussain, InAs/Si heterojunction nanotube tunnel transistors. Sci. Rep. 5, 1–7 (2015)

S.H. Kim, H. Kam, C. Hu, T.J.K. Liu, Germanium-source tunnel field effect transistors with record high ION/IOFF. in Symposium on VLSI Technology (Honolulu, 2009), pp. 178–179

B. Raad, D. Sharma, K. Nigam, P. Kondekar, Physics-based simulation study of high-performance gallium arsenide phosphide-indium gallium arsenide tunnel field-effect transistor. Micro Nano Lett. 11(7), 366–368 (2016)

T. Krishnamohan, D. Kim, S. Raghunathan, K. Saraswat, DoubleGate Strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and 60 mV, dec subthreshold slope, in IEEE International Electron Devices Meeting (San Francisco, 2008), pp. 1–3

J. Min, J. Wu, Y. Taur, Analysis of source doping effect in tunnel FETs with staggered bandgap. IEEE Electron Device Lett. 34(10), 1094–1096 (2015)

C. Sandow, J. Knoch, C. Urban, Q.-T. Zhao, S. Mantl, Impact of electrostatics and doping concentration on the performance of silicon tunnel field-effect transistors. Solid State Electron. 53(10), 1126–1129 (2009)

H. Schmid, M.T. Bjrk, J. Knoch, S. Karg, H. Riel, W. Riess, Doping limits of grown in situ doped silicon nanowires using phosphine. Nano lett. 57(4), 820–826 (2009)

J. Wu, Y. Taur, Reduction of TFET OFF-current and subthreshold swing by lightly doped drain. IEEE Trans. Electron Devices 63(8), 3342–3345 (2016)

ATLAS Device Simulation Software (Silvaco Int., Santa Clara, CA, 2012)

H.J.M. Veendrick, Short-circuit dissipation of static CMOS circuitry and its impact on the design of buffer circuits. IEEE J. Solid State Circuits 19(4), 468–473 (1984)

M.S. Kim, H. Liu, X. Li, S. Datta, V. Narayanan, A steepslope tunnel FET based SAR analog-to-digital converter. IEEE Trans. Electron Devices 61(11), 3661–3667 (2014)

J. Madan, R. Chaujar, Interfacial charge analysis of heterogeneous gate dielectric-gate all around-tunnel FET for improved device reliability. IEEE Trans. Device Mater. 16(2), 227–234 (2016)

B.R. Raad, S. Tirkey, D. Sharma, P. Kondekar, A new design approach of dopingless tunnel FET for enhancement of device characteristics. IEEE Trans. Electron Devices 64(4), 1830–1836 (2017)

Acknowledgements

The authors would like to thank the Science and Engineering Research Board, Department of Science and Technology, Government of India (established through an act of parliament) for providing the financial support to carry out this work. This work has been implemented under the Project Implementation of Sigma Delta Modulator Using Nanowire Electrically Doped Hetero-Material Tunnel Field-Effect Transistor (TFET) for Ultra-Low-Power Applications which is funded by this board.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Soni, D., Sharma, D., Aslam, M. et al. A novel approach for the improvement of electrostatic behaviour of physically doped TFET using plasma formation and shortening of gate electrode with hetero-gate dielectric. Appl. Phys. A 124, 306 (2018). https://doi.org/10.1007/s00339-018-1670-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-018-1670-x