Abstract

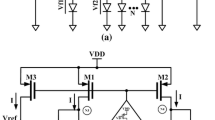

A 2 \(\times \) VDD output buffer in conjunction with a process and voltage (PV) compensation technique is proposed to keep the slew rate (SR) within predefined ranges regardless of PV variations. Temperature variation is not considered as it is found to be relatively less correlated with SR variation for a 90 nm CMOS process or better. All bias voltages in PV variation detectors are generated from bandgap circuits such that variations have been guaranteed by simulation to be less than 4.10%. The proposed design is realized on silicon using a 90 nm CMOS process, where the core area is 0.052 \(\times \) 0.388 mm\(^2\). The data rate is 650/500 MHz given a 1.0/2.0 V supply voltage with a 20 pF load, respectively, by physical measurements. The \(\Delta \) SR improvement is 30.7 and 31.4% for 1 \(\times \) VDD and 2 \(\times \) VDD, respectively, when the proposed PV compensation design is activated.

Similar content being viewed by others

References

M. Bazes, Output buffer impedance control and noise reduction using a speed-loc ked loop, in IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, (2004), pp. 486–541

C.-L. Chen, H.-Y. Tseng, R.-C. Kuo, C.-C. Wang, On-chip MOS PVT variation monitor for slew rate self-adjusting 2 \(\times \) VDD output buffers, in Proc. Int. Conf. on IC Design and Technology (ICICDT), (2012), p. 14

M.-D. Ker, P.-Y. Chiu, Design of 2 \(\times \) VDD-tolerant I/O buffer with PVT compensation realized by only 1\(\times \)VDD thin-oxide devices. IEEE Trans. Circuits Syst. I (TCAS-I) 60(10), 2549–2560 (2013)

J.-S. Kim, J.-Y. Lee, B.-D. Choi, Slew-rate-enhanced rail-to-rail buffer amplifier for TFT LCD data drivers. Electron. Lett. 48(15), 924–925 (2012)

Y.-H. Kwak, I. Jung, H.-D. Lee, Y.-J. Choi, Y. Kumar, C. Kim, A one cycle lock time slew-rate-controlled output driver, in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), (2007), pp. 408–611

Y.-H. Kwak, I.-H. Jung, C.-W. Kim, A Gb/s+ slew-rate/impedance-controlled output driver with single-cycle compensation time. IEEE Trans, Circuits Syst. II Exp. Briefs 57(2), 120–125 (2010)

T.-J. Lee, W. Lin, C.-C. Wang, Slew rate improved 2 \(\times \) VDD output buffer using leakage and delay compensation, in Proc. IEEE Int. Conf. on Electron Devices and Solid-State Circuits (EDSSC), (2014), pp. 1-2

T.-Y. Tsai, Y.-L. Teng, C.-C. Wang, A nano-scale 2 \(\times \) VDD I/O buffer with encoded PV compensation technique, in Proc. IEEE Int. Symp. on Circuits and Systems (ISCAS), (2016), pp. 598–601

C.-C. Wang, W.-J. Lu, H.-Y. Tseng, A high-speed 2 \(\times \) VDD output buffer with PVT detection using 40-nm CMOS technology, in Proc. IEEE Int. Symposium on Circuits and Systems (ISCAS), (2013), pp. 2079–2082

C.-C. Wang, T.-Y. Tsai, T.-J. Lee, K.-W. Ruan, 2 \(\times \) VDD output buffer with 36.4% slew rate improvement using leakage current compensation. Electron. Lett. 53(2), 62–64 (2017)

C.-C. Wang, C.-L. Chen, H.-Y. Tseng, H.-H. Hou, C.-Y. Juan, A 800 Mbps and 12.37 ps jitter bidirectional mixed-voltage I/O buffer with dual-path gate-tracking circuit. IEEE Trans. Circuits Syst. I, Reg. Papers 60(1), 116–124 (2013)

C.-C. Wang, T.-Y. Tsai, W. Lin, A high-speed 2 \(\times \) VDD output buffer with PVTL detection using 40-nm CMOS technology, in Proc. IEEE Int. Conf. on IC Design Technology (ICICDT), (2015), pp. 1–4

Acknowledgements

This proposed design was partially supported by the Ministry of Science and Technology, Taiwan, under Grant MOST 105-2218-E-110-006-, and the authors would like to express their deepest appreciation to CIC (Chip Implementation Center) in NARL (Nation Applied Research Laboratories), Taiwan, for their knowledgeable assistance in chip fabrication.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Wang, CC., Tsai, TY., Deng, YL. et al. 500 MHz 90 nm CMOS 2 \(\times \) VDD Digital Output Buffer Immunity to Process and Voltage Variations. Circuits Syst Signal Process 38, 556–568 (2019). https://doi.org/10.1007/s00034-018-0895-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-018-0895-4