Abstract

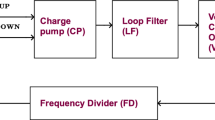

This paper describes a symmetric phase frequency detector (PFD). The symmetric structure of PFD provides phase-locked loop (PLL) functions with a low jitter. The most important point in designing PFDs is attention to their dead zone, the extent of their linearity, and the frequency range of operation. As the dead zone of a phase detector circuit is smaller, this circuit is capable of detecting fewer phase differences in high frequencies. In this paper, considering the trade-off between the dead zone and the maximum operating frequency, the highest operating frequency is achieved with minimal dead zone design. Post-layout simulation for TSMC 0.13 μm technology is performed using the CMOS technology: The results so obtained are then compared with existing literature. These results indicate a power consumption of less than 90 μW and a frequency response of 4.1 GHz, as well as a dead zone of less than 25 ps in the worst case: This is a suitable condition as compared to previous, related works. The area of the proposed symmetric circuit is 250 μm2. Finally, the proposed PFD tested in PLL and the results indicate that the structure is useful for frequency synthesizer applications.

Similar content being viewed by others

References

R.J. Baker, H.W. Li, D.E. Boyce, CMOS Circuit Design Layout and Simulation, IEEE Press Series on Microelectronics System (Wiley-IEEE Press, London, 2000), pp. 355–361 and 383–387

C.C. Chung, C.L. Chang, A wide-range all-digital delay-locked loop in 65 nm CMOS technology, in 2010 International Symposium on VLSI Design Automation and Test (VLSI-DAT), pp. 66–69, 26 Apr 2010

X. Gao, E. Klumperink, G. Socci, M. Bohsali, B. Nauta, Spur reduction techniques for phase-locked loops exploiting a sub-sampling phase detector. IEEE J. Solid-State Circuits 45(9), 1809–1821 (2010)

M. Gholami, G. Ardeshir, Analysis of DLL jitter due to voltage-controlled delay line. Circuits Syst. Signal Process. 32(5), 35–2119 (2013)

M. Gholami, Phase detector with minimal blind zone and reset time for GSamples/s DLLs. Circuits Syst Signal Process. 36, 3549–3563 (2017)

M. Gholami, Total jitter of delay-locked loops due to four main jitter sources. IEEE Trans. Very Large Scale Integr. Syst. 24(6), 9–2040 (2016)

S. Kao, A delay-locked loop with self-calibration circuit for reducing phase error. Microelectron. J. 44(8), 663–669 (2013)

S. Kazeminia, S.S. Mowloodi, K. Hadidi. Wide-range 16-phases DLL based on improved dead-zone phase detector and reduced gain charge pump, in 22nd Iranian Conference on Electrical Engineering (ICEE), May 2014

S. Kazeminia, S.S. Mowloodi, K. Hadidi, A 80-MHz-to-410-MHz 16-phases DLL based on improved dead-zone open-loop phase detector and reduced-gain charge pump. J. Circuits Syst. Comput. 24, 1550001 (2015)

H. Lee, T. Ahn, D. Jung, B. Park, Scheme for no dead zone, fast PFD design. J. Korean Phys. Soc. 40(4), 543–545 (2002)

F. Modarresi, M. Ghasemzadeh, M. Mazlumi, A. Amini, T. Abolfathi, A low-jitter, full-differential PLL in 0.18 μm CMOS technology. Int. J. Microelectron. Comput. Sci. 7(4), 119–122 (2016)

Y. Qiu, L. Zhao, F. Zhang, Design of 0.35-ps RMS jitter 4.4–5.6-GHz frequency synthesizer with adaptive frequency calibration using 55-nm CMOS technology. Circuits Syst. Signal Process. 37, 1479–1504 (2018)

J. Strzelecki, S. Ren, Near-zero dead zone phase frequency detector with wide input frequency difference. Electron. Lett. 51(14), 61–1059 (2015)

K.P. Thakore, H.C. Parmar, N.M. Devashrayee, High speed PFD with charge pump and loop filter for low jitter and low power PLL. IJECT 2(2), 55–59 (2011)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Sofimowloodi, S., Razaghian, F. & Gholami, M. Low-Power High-Frequency Phase Frequency Detector for Minimal Blind-Zone Phase-Locked Loops. Circuits Syst Signal Process 38, 498–511 (2019). https://doi.org/10.1007/s00034-018-0887-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-018-0887-4