Abstract

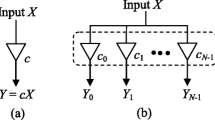

Online arithmetic operators offer advantages of reduction in resource utilization and interconnection complexity besides providing pipelining at digit level. Multiplierless constant coefficient multiplication using the shift-and-add technique is widely used in digital signal processing applications. This paper proposes a novel bit serial adaptation of the parallel shift-and-add algorithm to online arithmetic. The proposed multipliers use right shifts instead of the traditional left shifts resulting in causal online implementations. Graph-based and hybrid algorithms are developed for the estimation of the distance of a constant from a set of constants in terms of the number of additions and for the synthesis of online multiple constant multipliers under area and online delay constraints. The computational complexity of the algorithms is determined. Results of implementation on randomly generated constant sets and FIR filter instances show substantial improvements in the number of operations required using the distance heuristic. Further, it is shown that the proposed techniques and algorithms result in significant savings in resource utilization, logic depth, and clock frequency compared to parallel and digit-serial algorithms.

Similar content being viewed by others

References

L. Aksoy, E. Costa, P. Flores, J. Monteiro, Exact and approximate algorithms for the optimization of area and delay in multiple constant multiplications. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 27(6), 1013–1026 (2008)

L. Aksoy, E. Gunes, P. Flores, Search algorithms for the multiple constant multiplications problem: exact and approximate. Elsevier J. Microprocess. Microsyst. 34(5), 151–162 (2010)

L. Aksoy, E. Costa, P. Flores, J. Monteiro, Finding the optimal tradeoff between area and delay in multiple constant multiplications. Elsevier J. Microprocess. Microsyst. 35, 729–741 (2011)

L. Aksoy, C. Lazzari, E. Costa, P. Flores, J. Monteiro, High-level algorithms for the optimization of gate-level area in digit-serial multiple constant multiplications. INTEGRATION VLSI J. 45(3), 294–306 (2012)

F. Al-Hasani, M.P. Hayes, A. Bainbridge-Smith, A common subexpression elimination tree algorithm. IEEE Trans. Circuits Syst.-I: Regul. Pap. 60(9), 2389–2400 (2013)

D.R. Bull, D.H. Horrocks, Primitive operator digital filters. IEE Proc. G Circuits Devices Syst. 138(3), 401–412 (1991)

P. Cappello, K. Steiglitz, Some complexity issues in digital signal processing. IEEE Trans. Acoust. Speech Signal Process. 32(5), 1037–1041 (1984)

A.G. Dempster, M.D. Macleod, Constant integer multiplication using minimum adders. IEE Proc. Circuits Devices Syst. 141(5), 407–413 (1994)

A.G. Dempster, M.D. Macleod, Use of minimum-adder multiplier blocks in FIR digital filters. IEEE Trans. Circuits Syst.-II 42(9), 569–577 (1995)

M.D. Ercegovac, T. Lang, Digital Arithmetic (Morgan Kaufmann, San Francisco, 2004)

M. Farahani, E. Guerra, B. Colpitts, Efficient implementation of FIR filters based on a novel common subexpression elimination algorithm, in Proceedings Canadian Conference on Electrical and Computer Engineering, pp. 1–4 (2010)

O. Gustafsson, A difference based adder graph heuristic for multiple constant multiplication problems, in Proceedings IEEE International Symposium on Circuits and Systems, pp. 1097–1100 (2007)

K. Johansson, O. Gustafsson, A. Dempster, L. Wanhammar, Algorithm to reduce the number of shifts and additions in multiplier blocks using serial arithmetic, in Proceedings IEEE Meditteranean Electrotechnical Conference, pp. 197–200 (2004)

K. Johansson, O. Gustafsson, L. Wanhammar, Multiple constant multiplication for digit-serial implementation of low power FIR filters. WSEAS Trans. Circuits Syst. 5(7), 1001–1008 (2006)

G.B. Joseph, R. Devanathan, Radix-2h online floating point multipliers, in Proceedings 10th IEEE Dallas Circuits and Systems Conference, DCAS 14, pp. 1–4 (2014)

G.B. Joseph, Architectures for online processing in reconfigurable computing. Doctoral dissertation submitted to Hindustan Institute of Technology and Science, Chennai, India (2017)

M. Kumm, K. Liebisch, P. Zipf, Reduced complexity single and multiple constant multiplication in floating point precision, in Proceedings 22nd International Conference on Field Programmable Logic and Applications, pp. 255–261 (2012)

J.V. Moreno, T. Lang, J. Hormigo, Radix-2 multioperand and multiformat streaming online addition. IEEE Trans. Comput. 61(6), 790–803 (2012)

Y. Pan, P.K. Meher, Bit-level optimization of adder-trees for multiple constant multiplications for efficient FIR filter implementation. IEEE Trans. Circuits Syst. I: Regul. Pap. 61(2), 455–462 (2014)

K. Shi, D. Boland, G.A. Constantinides, Efficient FPGA implementation of digit parallel online arithmetic operators, in Proceedings IEEE International Conference on Field-Programmable Technology (FPT), pp. 115–122 (2014)

Y. Voronenko, M. Püschel, Multiplierless multiple constant multiplication. ACM Trans. Algorithms 3(2), 1–38 (2007)

C.Y. Yao, H.H. Chen, T.F. Lin, C.J. Chien, C.T. Hsu, A novel common subexpression elimination method for synthesizing fixed-point FIR filters. IEEE Trans. Circuits Systems-I Regul. Pap. 51(11), 2215–2221 (2004)

Author information

Authors and Affiliations

Corresponding author

Appendix

Appendix

Rights and permissions

About this article

Cite this article

Joseph, G.B., Devanathan, R. Algorithms for Multiplierless Multiple Constant Multiplication in Online Arithmetic. Circuits Syst Signal Process 37, 5127–5142 (2018). https://doi.org/10.1007/s00034-018-0811-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-018-0811-y