Abstract

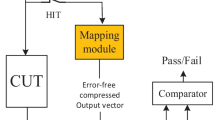

Area and test time are two major overheads encountered during data path high level synthesis for BIST. This paper presents an approach to behavioral synthesis for loop-based BIST. By taking into account the requirements of the BIST scheme during behavioral synthesis processes, an area optimal BIST solution can be obtained. This approach is based on the use of test resources reusability that results in a fewer number of resiters being modified to be test registers. This is achieved by incorporating self-testability constraints during register assignment operations. Experimental results on benchmarks are presented to demonstrate the effectiveness of the approach.

Similar content being viewed by others

References

Avra L. Allocation and assignment in high-level synthesis for self-testable data paths. InProc. IEEE 1991 International Test Conference (ITC’91), 1991, pp.463–472.

Parulkar I, Gupta S, Breuer M. Data path allocation for synthesizing RTL designs with low BIST area overhead. InProc. ACM/IEEE 1995 Design Automation Conference (DAC’95) 1995, pp.395–401.

Papachristou C A, Chiu S, Harmanani H. SYNTEST: A method for high-level SYNthesis with self-TESTability. InProc. IEEE 1994 Int. Conf. Computer Design (ICCD’94), 1994, pp.458–462.

Li X, Cheung P Y S. Data path synthesis for BIST with low area overhead. InProc. IEEE 1999 Asian and South Pacific Design Automation Conf. (ASP-DAC’99), 1999, pp.275–278.

Harris I G, Orailoglu A. SYNCBIST: SYNthesis for Concurrent Built-In Self-Testability. InProc. IEEE 1994 Int. Conf. Computer Design (ICCD’94), 1994, pp.101–104.

Wang L T, McClusky E J. Concurrent Built-In Logic Block Observer (CBILBO). InProc. IEEE Int. Symposium on Circuits & Systems (ISCAS’96), 1996, pp.1054–1057.

Abadir M S, Breuer M A. A knowledge-based system for designing testable VLSI chips.IEEE Design & Test of Computers, 1985, 2(3): 56–68.

Li X, Cheung P Y S. An effective apparatus for at-speed self-testing. InProc. IEEE Instrumentation and Measurement Conference (IMTC/99), May 24–26, 1999, 2: 844–848.

Lai K, Papachristou C A, Baklashov M. Design for testability across the boundary of behavioral and structural domains. InProc. Int. Conf. Computer Aided Design & Computer Graphics, 1997, pp.460–465.

Thearling K, Abraham J. An easily computed function level testability measure. InProc. Int. Test Conf. (ITC’89), 1989, pp.381–390.

Golumbic M C. algorithmic Graph theory and Perfect Graphs. Academic Press, 1980.

Paulin P G, Knight J P. Force-directed scheduling for the behavioral synthesis of ASICs.IEEE Trans. CAD, 1989, 8(6): 661–679.

Tseng C J, Wieviorek D P. Automated synthesis of data paths in digital systems.IEEE Trans. CAD., 1986, 5(3): 379–395.

Jain R, Parker A C, Park N. Predicting system-level area and delay for pipelined and non-pipelined designs.IEEE Trans. CAD, 1992, 11(8): 955–965.

Kung S Y, Whitehouse H J, Kailath T. VLSI and Modern Signal Processing. Prentice-Hall, ¢1985.

Park N, Parker A C. SEHWA: A program for synthesis of pipelines. InProc. ACM/IEEE Design Auto. Conf., 1986, pp.454–460.

Author information

Authors and Affiliations

Corresponding author

Additional information

This work was supported in part by the National Natural Science Foundation of China (NSFC) under grant No. 69976002 and in part by the Croucher Foundation under grant No.360/062/0994.

LI Xiaowei received his B.Eng. and M.Eng. degrees in computer science from Hefei University of Technology, China, in 1985 and 1988, respectively. He received his ph.D. degree in computer science from the Institute of Computing Technology, the Chinese Academy of Sciences in 1991. Dr. Li joined Peking University as a Postdoctoral Research Fellow and a Lecturer in 1991, and was promoted to Associate Professor in 1993, all with the Department of Computer Science and Technology. In 1997 and 1998, he was a Visiting Research Fellow in the Department of Electrical and Electronic Engineering at the University of Hong Kong. In 1999, he was a Visiting Professor in the Graduate School of Information Science, Nara Institute of Science and Technology, Japan. His research interests include VLSI testing, design for testability, built-in self-test, high-level synthesis for testability, software testing and hardware/software co-test.

Paul Y.S. CHEUNG received his B.S. (Eng) degree with first-class honor in 1973 and his Ph.D. degree in 1978, both in EE from the Imperial College of Science and Technology, University of London. After working for Queen’s University of Belfast for two years as an engineer-in-charge of a laboratory, he returned to Hong Kong in 1978 to take up an academic position at the Hong Kong Polytechnic University. He joined the University of Hong Kong as a lecturer in 1980 and was promoted to Senior Lecturer/Associate Professor in 1987. He served as the Associate Dean of Faculty of Engineering from 1991–1994 and has been the Dean of Faculty of Engineering at the University of Hong Kong since 1994. He was the Director of IEEE Asia Pacific in 1995–1996 and served as the Secretary of IEEE in 1997. His research interests include parallel computer architecture, Internet computing, VLSI design and testing, signal processing and pattern recognition.

Rights and permissions

About this article

Cite this article

Li, X., Cheung, P.Y.S. High level synthesis for loop-based BIST. J. Comput. Sci. & Technol. 15, 338–345 (2000). https://doi.org/10.1007/BF02948869

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF02948869