Abstract

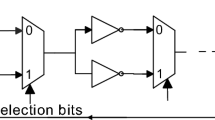

By analyzing the principle of process variations, a lightweight Physical Unclonable Function (PUF) circuit based on selectable cross-coupled inverters is proposed in this paper. Firstly, selectable cross-coupled inverters are chosen for two delay paths. Simultaneously, the circuit takes challenge signal to control each delay path. The PUF cell circuit is implemented in Semiconductor Manufacturing International Corporation (SMIC) 65 nm CMOS technology and the layout area is 2.94 μm × 1.68 μm. Then the 64-bit PUF circuit is achieved with the cascade connection of cell circuits. The simulation results show that the randomness is 49.4% and the reliability is 96.5%. Compared to the other works, this PUF circuit improves the encrypt performance and greatly reduces the area.

Similar content being viewed by others

References

S. R. Nassif. Modeling and analysis of manufacturing variations. IEEE Conference on Custom Integrated Circuits, San Diego, CA, USA, May 6–9, 2001, 223–228.

R. Pappu, B. Recht, J. Taylor, et al.. Physical one-way functions. Science, 297(2002)5589, 2026–2030.

D. Lim, J. W. Lee, B. Gassend, et al.. Extracting secret keys from integrated circuits. IEEE Transactions on Very Large Scale Integration) (VLSI) Systems, 13(2005)10, 1200–1205.

Y. Su, J. Holleman, and B. Otis. A 1.6pJ/bit 96% stable chip ID generating circuit using process variations. IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, February 11–15, 2007, 200–201.

G. E. Suh and S. Devadas. Physical unclonable functions for device authentication and secret key generation. Proceedings of the 44th Annual Design Automation Conference (DAC), New York, NY, USA, June 4–8, 2007, 9–14.

J. Guajardo, S. Kumar, G. Schrijen, et al.. FPGA intrinsic PUFs and their use for IP protection. Workshop on Cryptographic Hardware and Embedded Systems (CHES2007), Springer Berlin Heidelberg, September 10–13, 2007, 63–80.

L. Lin, S. Srivathsa, D. K. Krishnappa, et al.. Design and validation of arbiter-based PUFs for sub-45-nm low-power security applications. IEEE Transactions on Information Forensics and Security, 7(2012)4, 1394–1403.

Y. J. Zhang, P. J. Wang, Y. Li, et al.. Model and physical implementation of multi-port PUF in 65 nm CMOS. International Journal of Electronics, 100(2012) 11, 112–125.

K. Bernstein, D. J. Frank, A. E. Gattiker, et al.. High-performance CMOS variability in the 65-nm regime and beyond. IBM Journal of Research and Development, 50(2006)45, 433–449.

A. Asenov, A. R. Brown, J. H. Davies, et al.. Simulation of intrinsic parameter fluctuations in decananometer and nanometer-scale MOSFETs. IEEE Transactions on Electron Devices, 50(2003)9, 1837–1852.

X. L. Zhang, P. J. Wang, and Y. J. Zhang. Highly stable data SRAM-PUF in 65 nm CMOS process. IEEE 10th International Conference on ASIC, Shenzhen, China, October 28–31, 2013, 705–708.

M. Majzoobi and F. Koushanfar. Time-bounded authentication of FPGAs. IEEE Transactions on Information Forensics and Security, 6(2011)3, 1123–1135.

Author information

Authors and Affiliations

Corresponding author

Additional information

Supported by the National Natural Science Foundation of China (Nos. 61474068, 61404076, 61274132), the Zhejiang Provincial Natural Science Foundation of China (No. LQ14F040001), and the Doctoral Program of Higher Education of China (No. 20113305110005).

About this article

Cite this article

Zhang, X., Li, J., Wang, P. et al. Design of lightweight PUF circuit based on selectable cross-coupled inverters. J. Electron.(China) 31, 513–518 (2014). https://doi.org/10.1007/s11767-014-4108-4

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11767-014-4108-4