Abstract

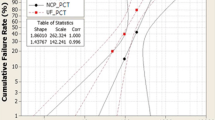

This study assesses the high-temperature storage (HTS) test and the pressure-cooker test (PCT) reliability of an assembly of chips and flexible substrates. After the chips were bonded onto the flexible substrates, specimens were utilized to assess the HTS test and PCT reliability. After the PCT and HTS tests, the die-shear test was applied to examine changes in die-shear forces. The microstructure of the test specimens was analyzed to evaluate reliability and to identify possible failure mechanisms. When the duration of the HTS test was increased, the percentage of gold bumps that peeled off from the surface of the copper pads on the chip side increased, and a crack was present at the bonding interface between the gold bumps and chip bond pads. This crack was due to thermal stress generated during the HTS test, and degraded the die-shear force of the assembly of chips and flexible substrates. After the PCT, the crack was present at the interface between deposited layers of copper electrodes after the specimens were subjected to the PCT for various durations. Moisture penetrated into the deposited layers of the copper electrodes, deposited layers lost their adhesion, and the crack progressed from the corner into the central bond area as the test duration increased. To improve the PCT reliability of assemblies of chips and flexible substrates using the thermosonic flip-chip bonding process, one must prevent moisture from penetrating into deposited layers of copper electrodes and prevent crack formation at the interface between nickel and copper layers. Underfill would be an effective approach to prevent moisture from penetrating into deposited layers during the PCT, thereby improving the reliability of the samples during the PCT.

Similar content being viewed by others

References

D. Wojciechowski, J. Vaneteren, E. Reese, and H.W. Hagedorn, Microelectron. Reliab. 40, 1215 (2000).

J.C. Jagt, IEEE Trans. Comp. Packag. Manuf. Technol. A 21, 215 (1998).

C.L. Chuang, Q.A. Liao, H.T. Li, S.J. Liao, and G.S. Huang, Microelectron. Eng. 87, 624 (2010).

C.L. Chuang, J.N. Aoh, and C.H. Pan, Microelectron. Eng., revised.

C.L. Chuang and H.F. Fan, Microelectron. Eng. 88, 3080 (2011).

H. Ji, M. Li, C. Wang, and H.S. Bang, Mater. Sci. Eng. 447, 111 (2007).

C.D. Breach and F. Wulff, Microelectron. Reliab. 46, 2112 (2006).

T. Uno, Microelectron. Reliab. 51, 148 (2011).

C.L. Chuang, W.-H. Chen, H.-T. Li, and H.-T. Chen, Microelectron. Eng. 87, 2146 (2010).

L.K. The, E. Anto, C.C. Wong, S.G. Mhaisalkar, E.H. Wong, P.S. Teo, and Z. Chen, Thin Solid Film 462, 446 (2004).

JEDEC Standard, JESD22-A-103-B, “High Temperature Storage Life”, 2001.

JEDEC Standard, JESD22-A-102-C, “Pressure Cooker Testing”, 2000.

C.L. Chuang, Microelectron. Eng. 84, 551 (2007).

JEDEC Standard, EIA/JESD22-B-116, ``Wire Bond Shear Test'', 1998.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chuang, CL., Kang, MY. HTS and PCT Reliability of Chips and Flex Substrates Assembled Using a Thermosonic Flip-Chip Bonding Process. J. Electron. Mater. 41, 2588–2598 (2012). https://doi.org/10.1007/s11664-012-2033-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-012-2033-6